| Citation: |

Sarabdeep Singh, Ashish Raman, Naveen Kumar. Design and optimization analysis of dual material gate on DG-IMOS[J]. Journal of Semiconductors, 2017, 38(12): 124003. doi: 10.1088/1674-4926/38/12/124003

****

S Singh, A Raman, N Kumar. Design and optimization analysis of dual material gate on DG-IMOS[J]. J. Semicond., 2017, 38(12): 124003. doi: 10.1088/1674-4926/38/12/124003.

|

Design and optimization analysis of dual material gate on DG-IMOS

DOI: 10.1088/1674-4926/38/12/124003

More Information

-

Abstract

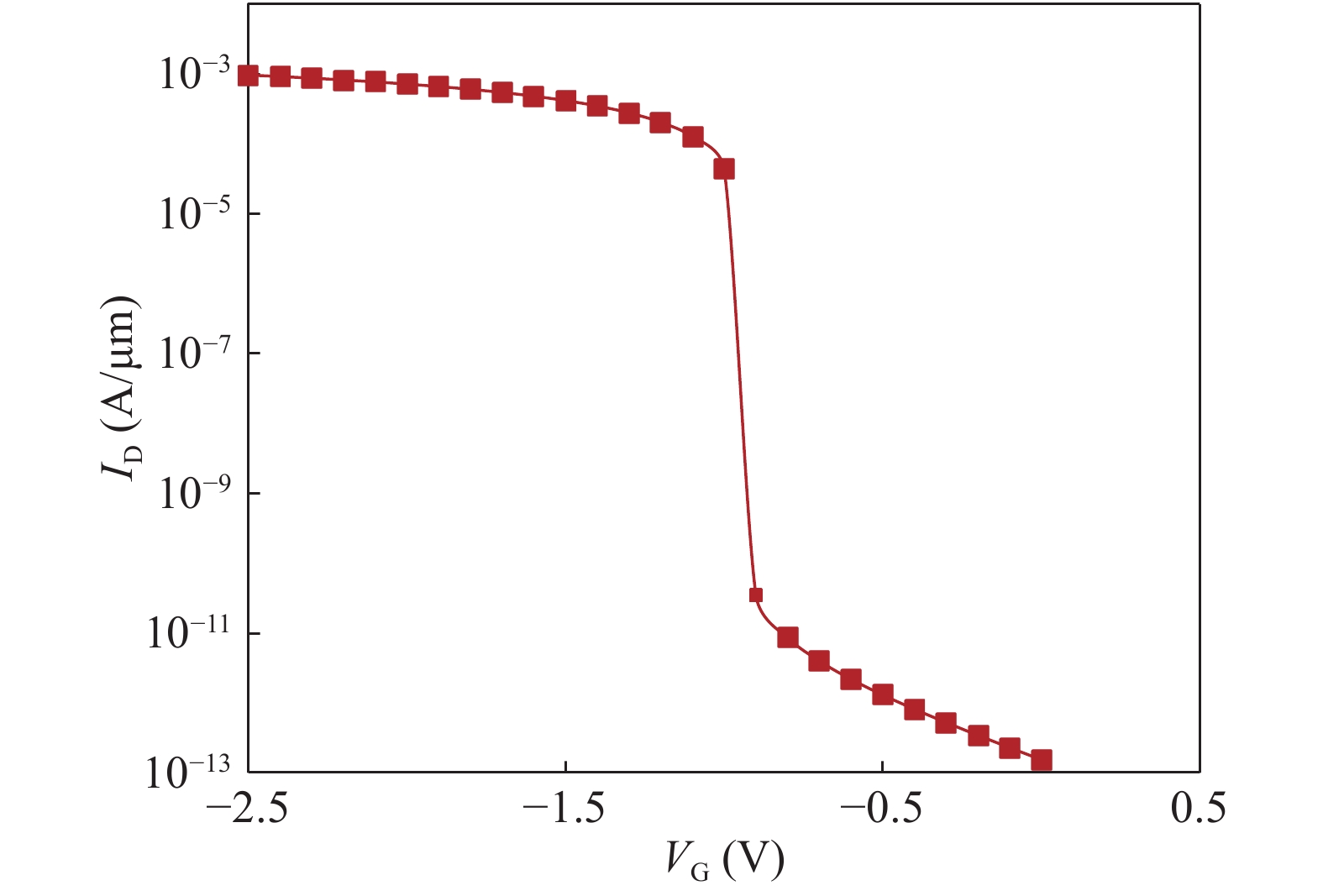

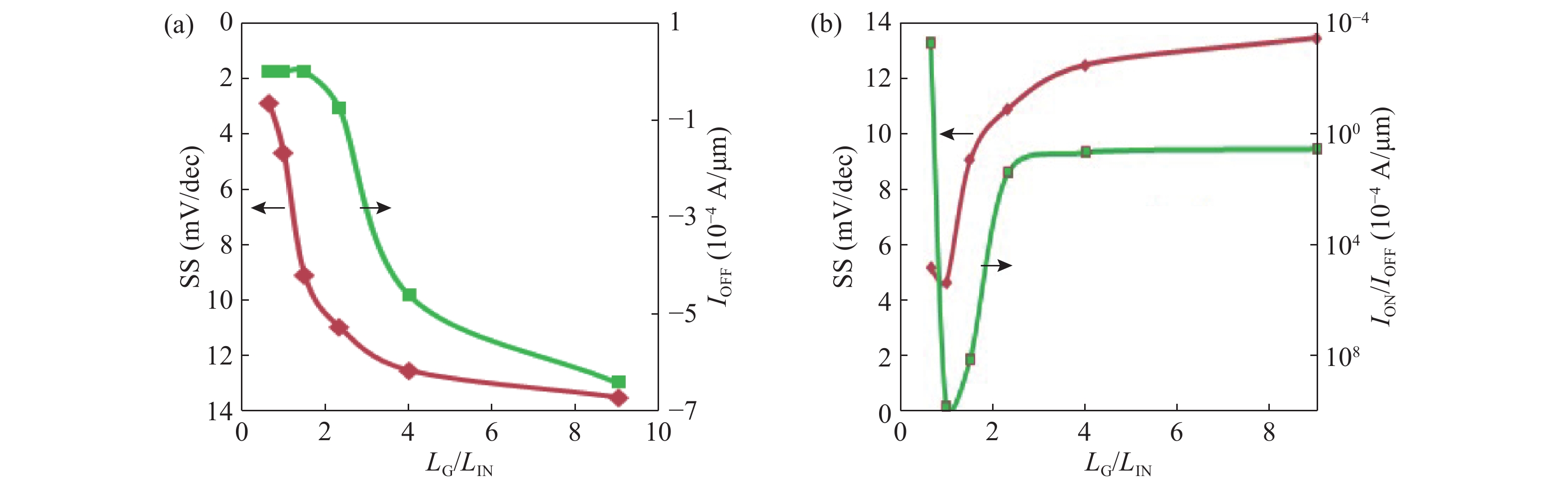

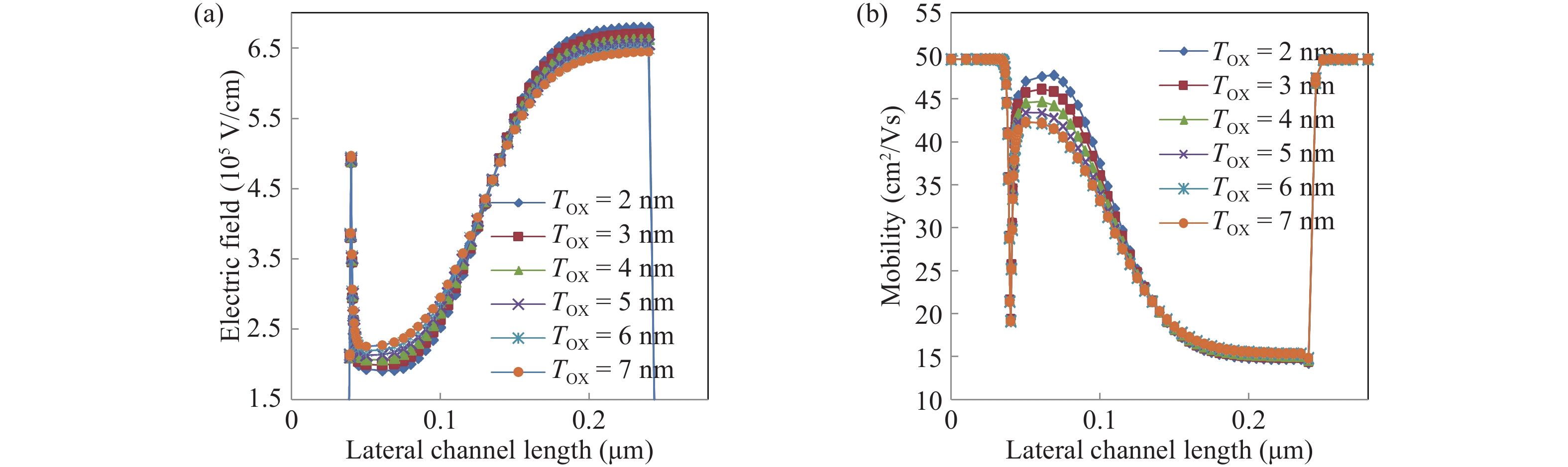

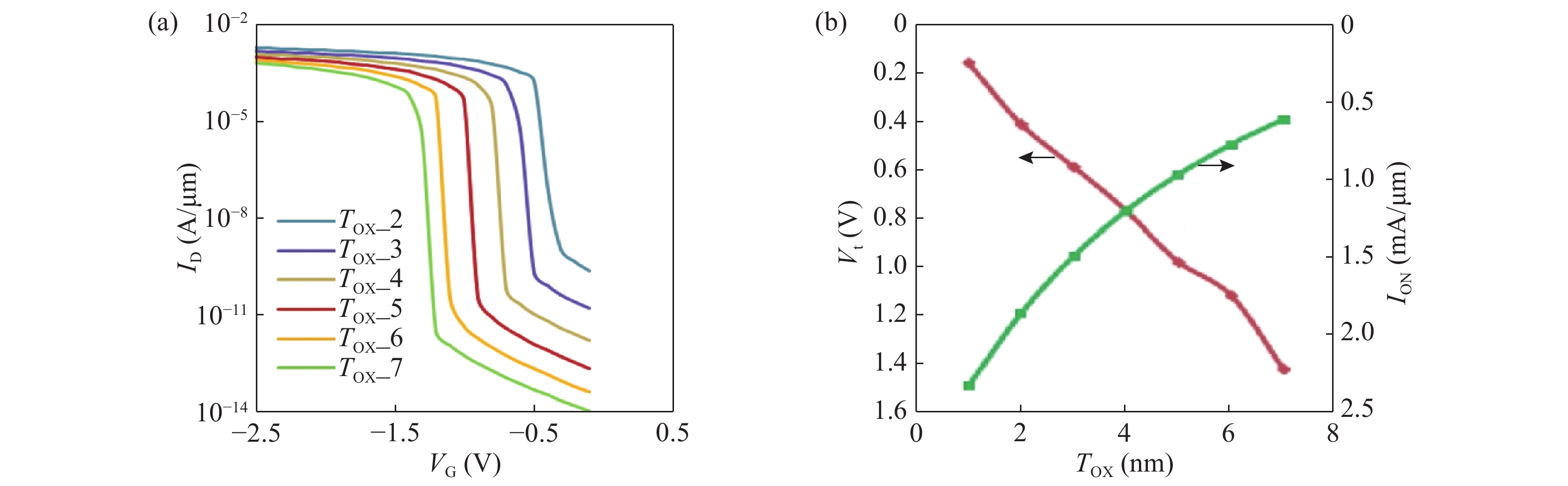

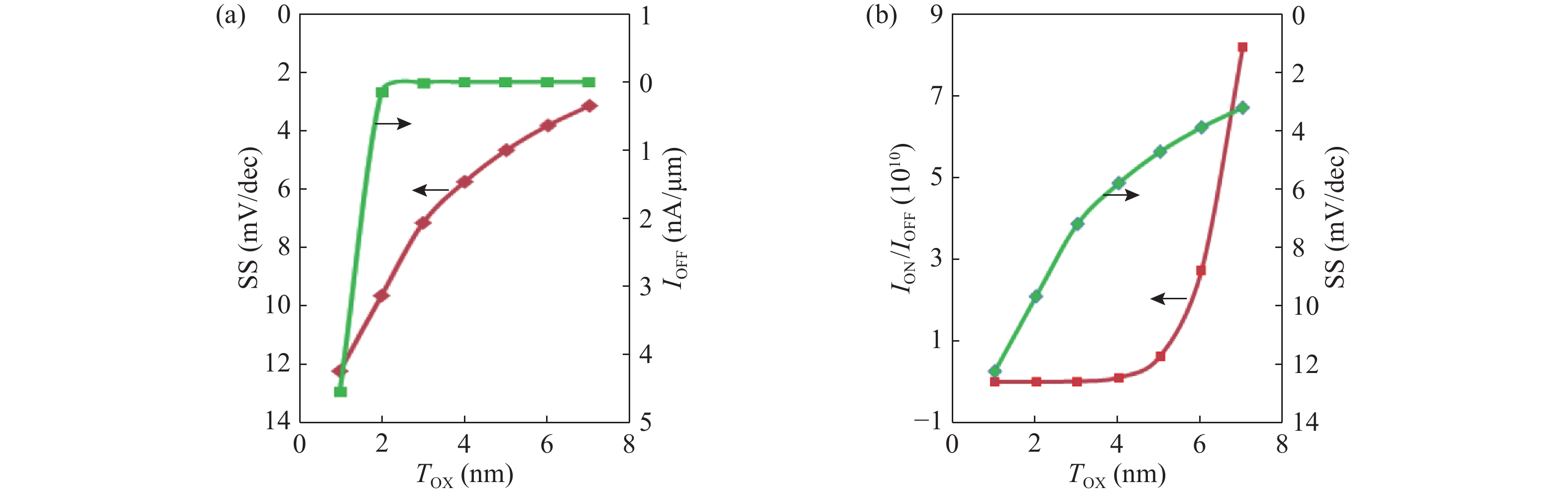

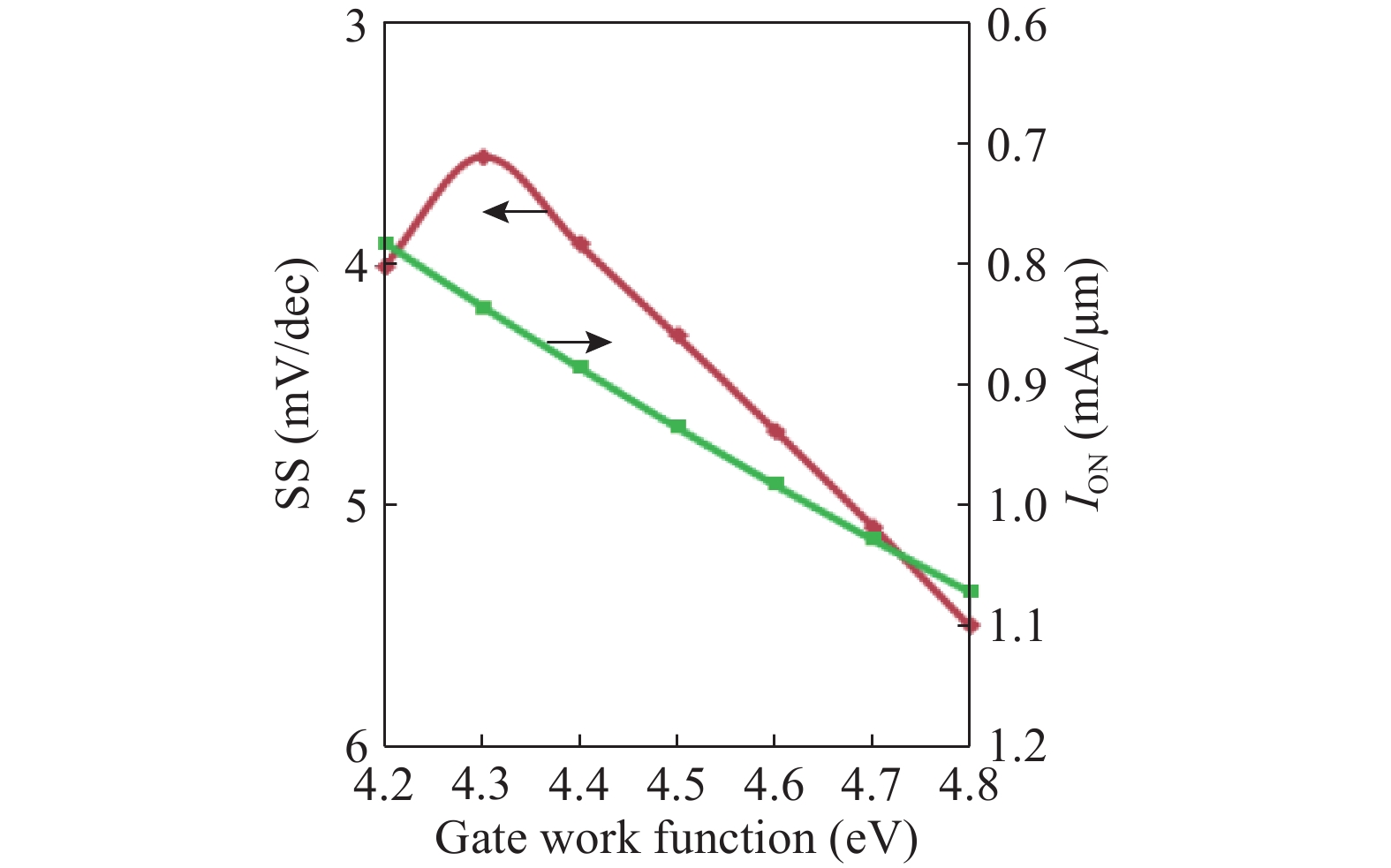

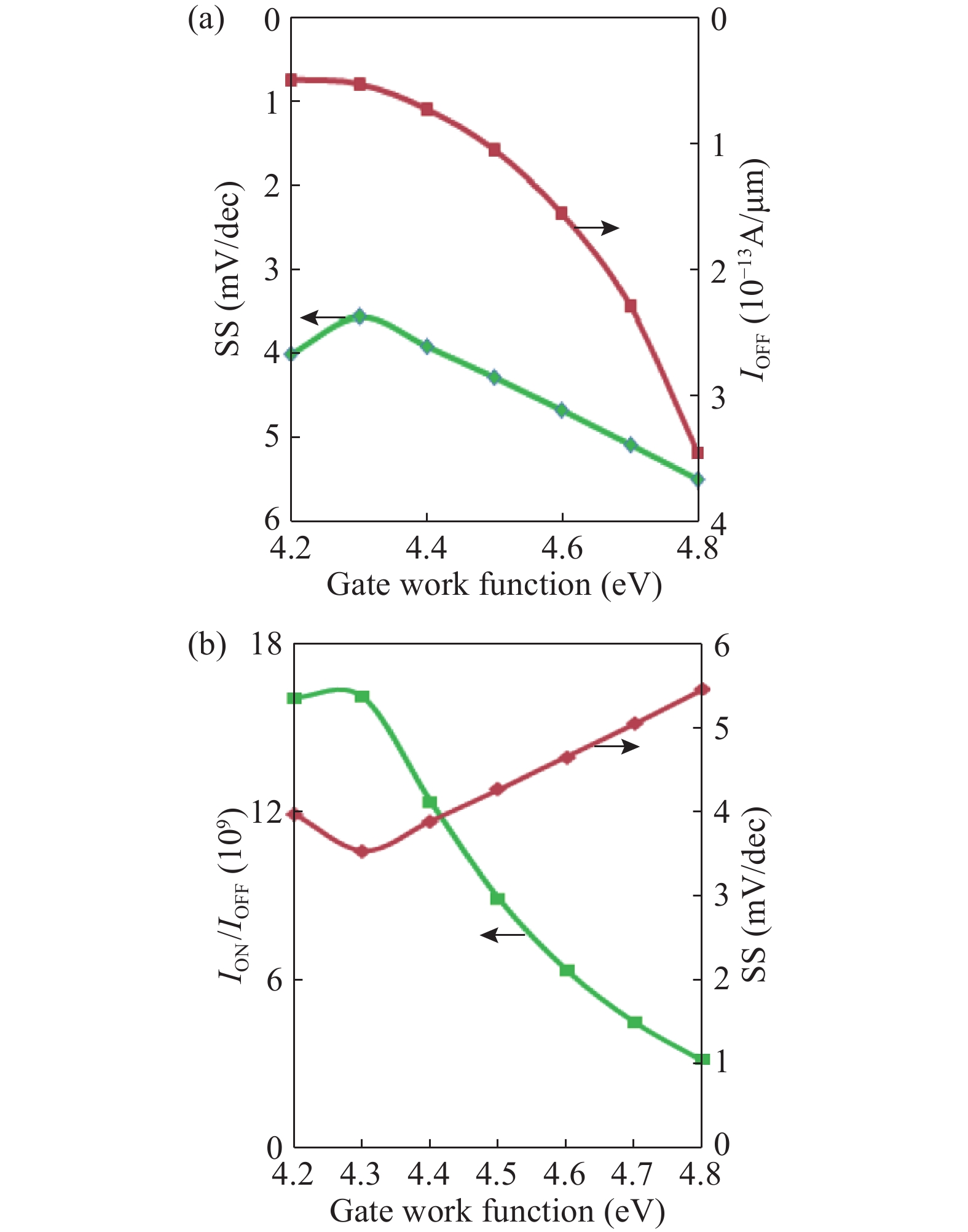

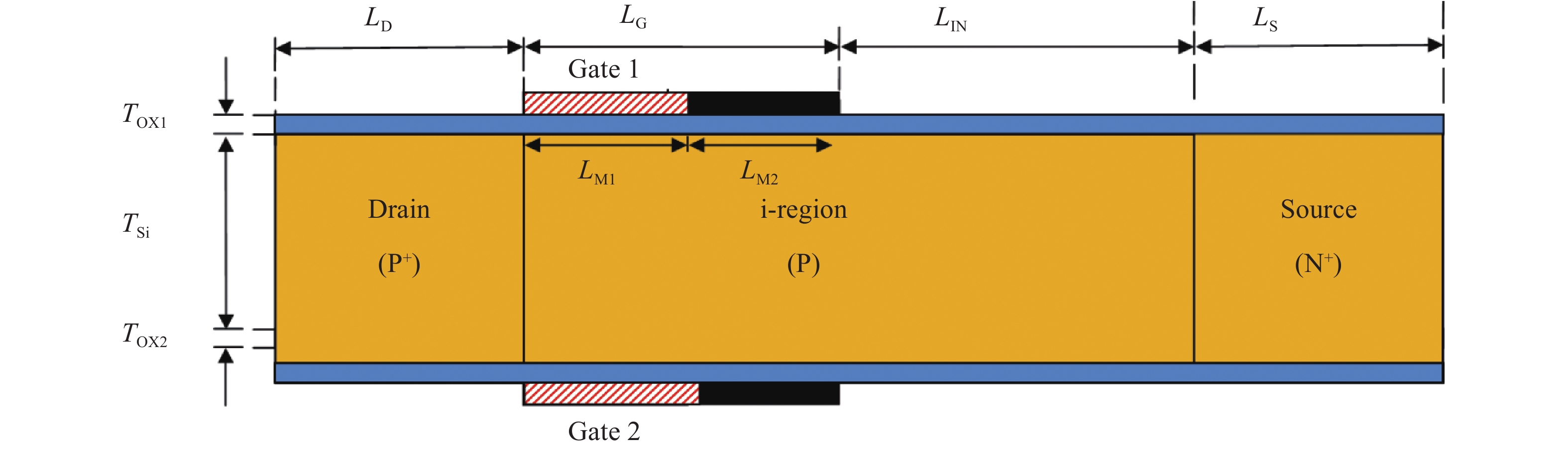

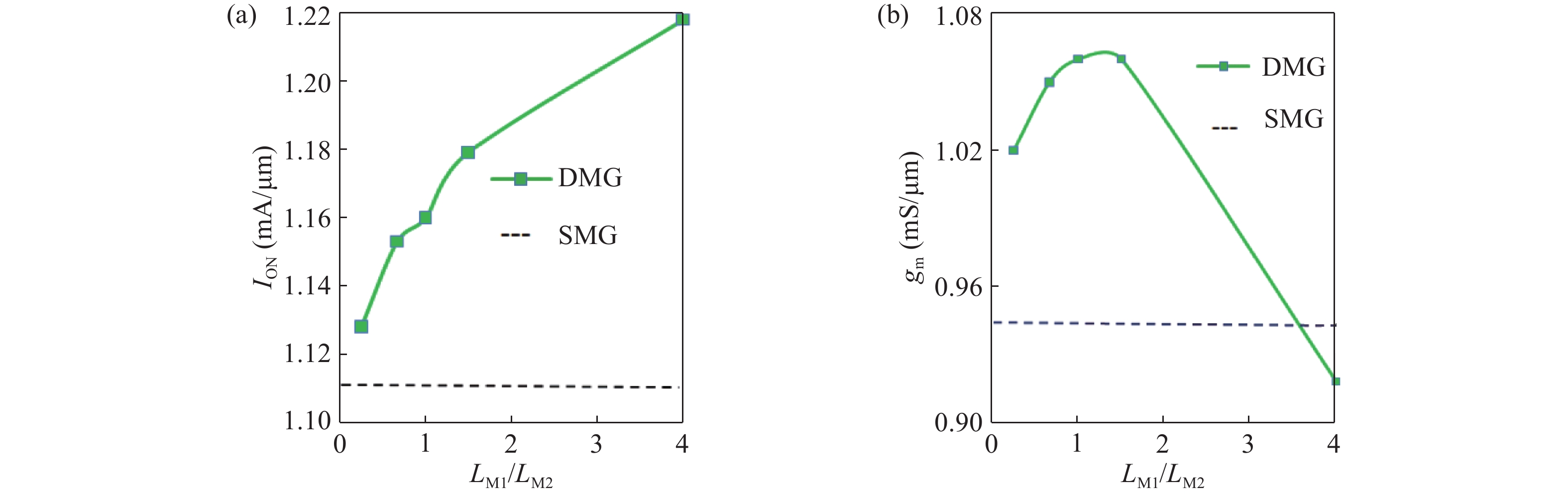

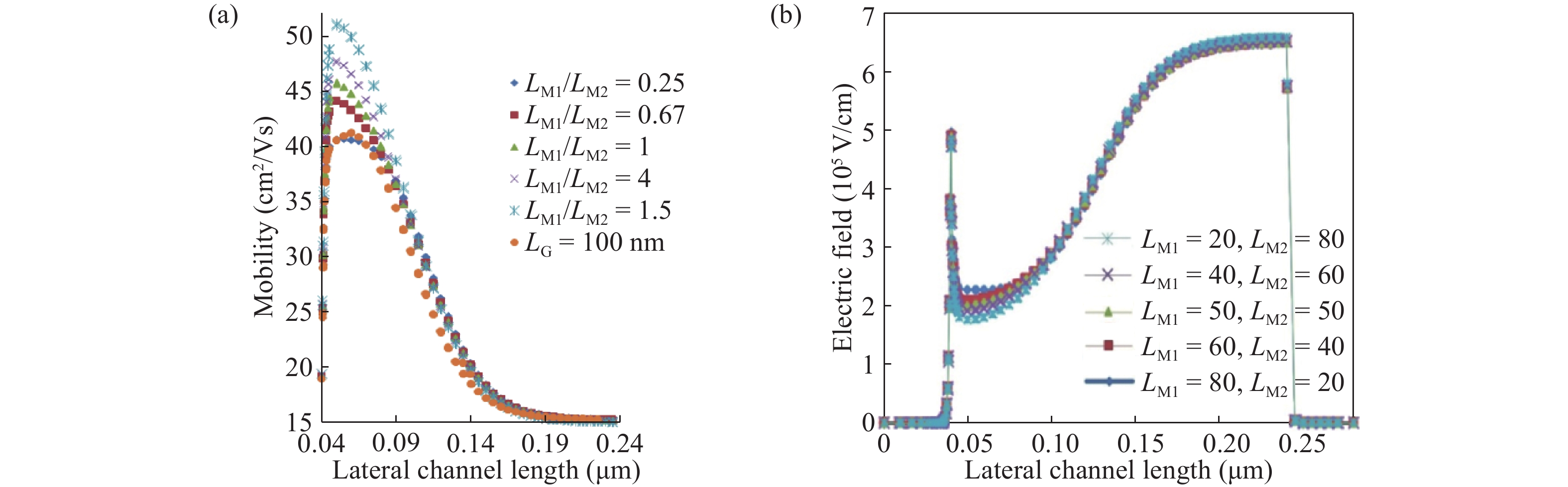

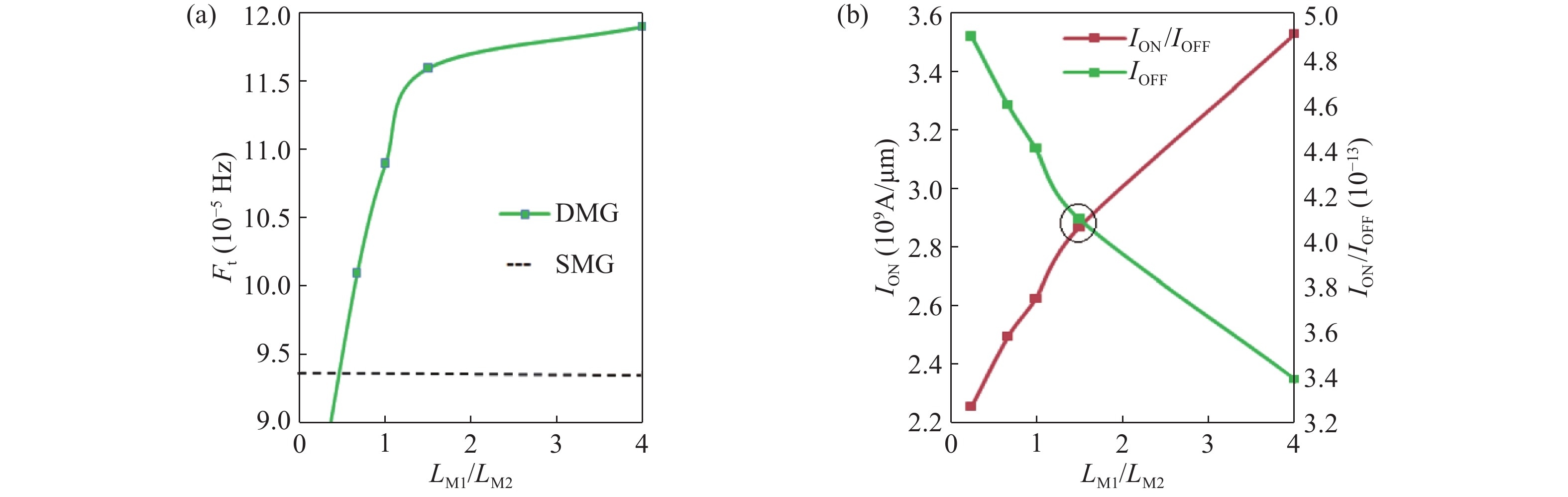

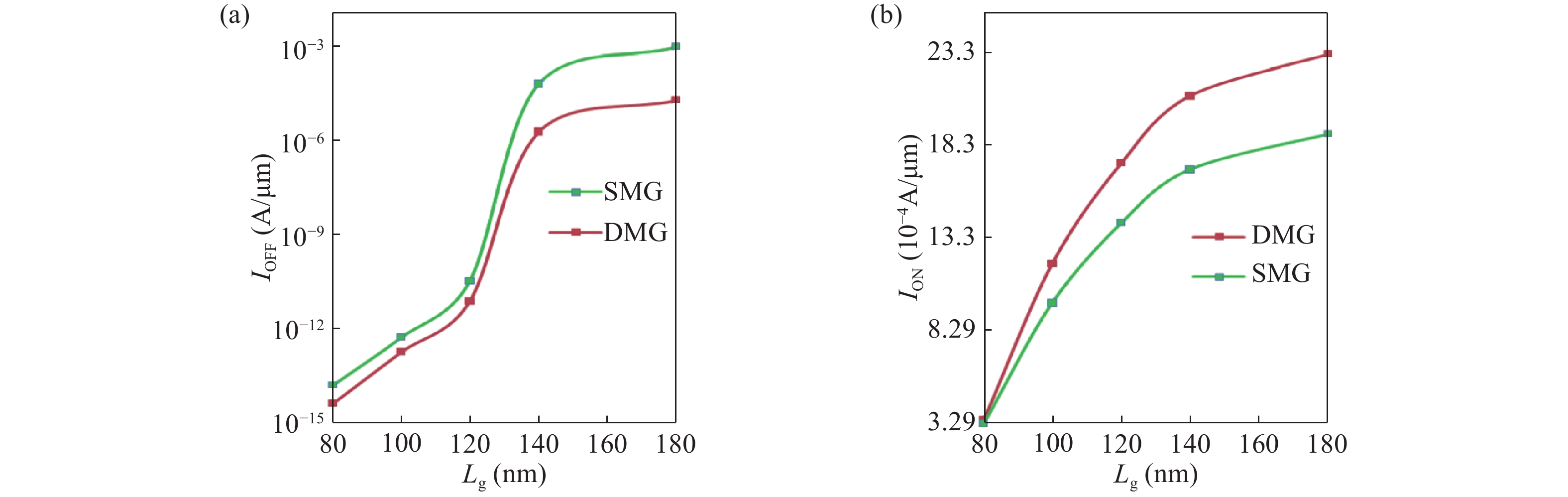

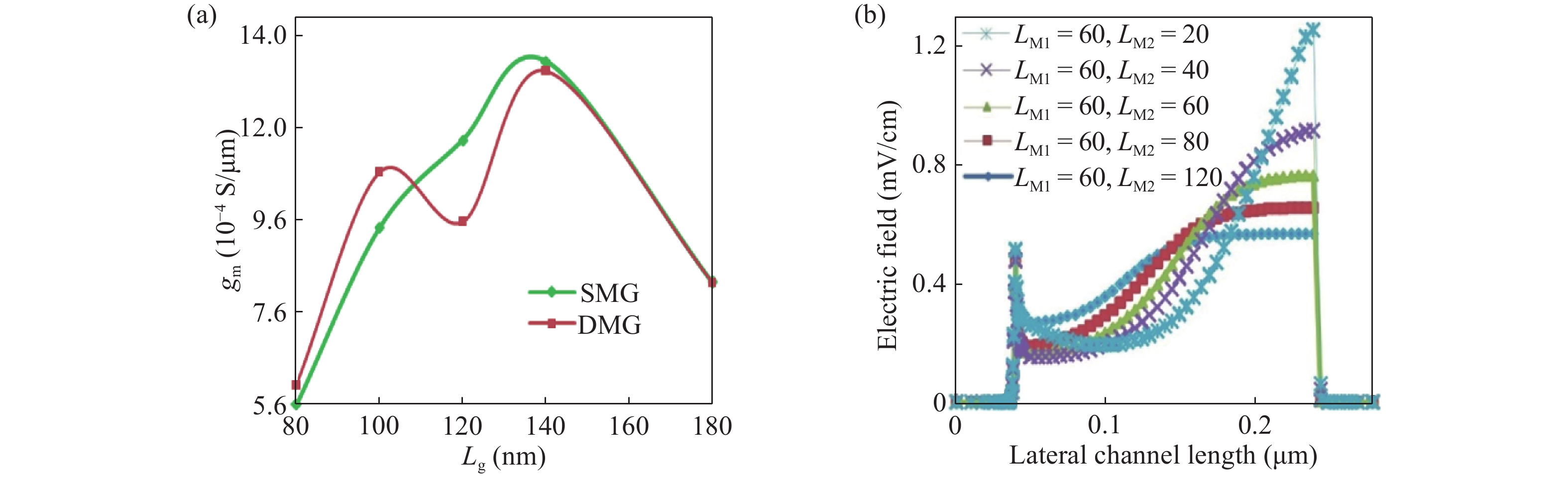

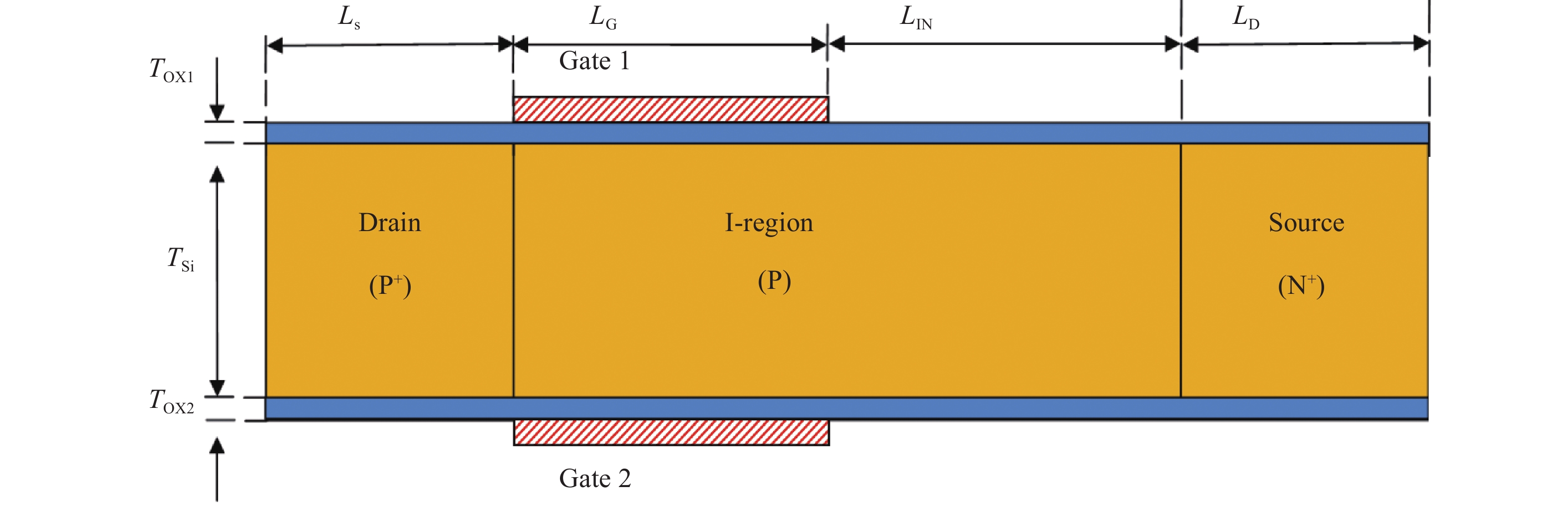

An impact ionization MOSFET (IMOS) is evolved for overcoming the constraint of less than 60 mV/decade sub-threshold slope (SS) of conventional MOSFET at room temperature. In this work, first, the device performance of the p-type double gate impact ionization MOSFET (DG-IMOS) is optimized by adjusting the device design parameters. The adjusted parameters are ratio of gate and intrinsic length, gate dielectric thickness and gate work function. Secondly, the DMG (dual material gate) DG-IMOS is proposed and investigated. This DMG DG-IMOS is further optimized to obtain the best possible performance parameters. Simulation results reveal that DMG DG-IMOS when compared to DG-IMOS, shows better ION, ION/IOFF ratio, and RF parameters. Results show that by properly tuning the lengths of two materials at a ratio of 1.5 in DMG DG-IMOS, optimized performance is achieved including ION/IOFF ratio of 2.87 × 109 A/μm with ION as 11.87 × 10−4 A/μm and transconductance of 1.06×10−3 S/μm. It is analyzed that length of drain side material should be greater than the length of source side material to attain the higher transconductance in DMG DG-IMOS. -

References

[1] Gopalakrishnan K, Griffin P B, Plummer J D. I-MOS: a novel semiconductor device with a subthreshold slope lower than kT/q. IEEE Electron Devices Meeting, 2002: 289[2] Gopalakrishnan K, Griffin P B, Plummer J D. Impact ionization MOS (I-MOS)-Part I: device and circuit simulations. IEEE Trans Eelectron devices, 2005, 52(1): 69 doi: 10.1109/TED.2004.841344[3] Saad I, Zuhir H M, Seng C B, et al. Characterization of vertical strained SiGe impact ionization MOSFET for ultra-sensitive biosensor application. IEEE International Conference on Semiconductor Electronics, 2014: 154[4] Singh S, Kondekar P N. Analytical modeling of Schottky tunneling source impact ionization MOSFET with reduced breakdown voltage. Eng Sci Technol, 2016, 19(1): 421[5] Choi W Y, Song J Y, Lee J D, et al. A novel biasing scheme for I-MOS (impact-ionization MOS) devices. IEEE Trans Nanotechnol, 2005, 4(3): 322 doi: 10.1109/TNANO.2005.847001[6] Ramaswamy S, Kumar M J. Junctionless impact ionization MOS: proposal and investigation. IEEE Trans Electron Devices, 2014, 61(12): 4295 doi: 10.1109/TED.2014.2361343[7] Hassani FA, Fathipour M, Mehran M. A comparison study between double and single gate p-IMOS. IEEE AFRICON 2007 :1.[8] ATLAS Device Simulation Software, Silvaco International, Santa Clara, CA, USA, 2014[9] Dixit A, Singh S, Kondekar P N, et al. Parameters optimization of lateral impact ionization MOS (LIMOS). IEEE Global High Tech Congress on Electronics (GHTCE), 2013: 56[10] Long W, Ou H, Kuo J M, et al. Dual-material gate (DMG) field effect transistor. IEEE Trans Electron Devices, 1999, 46(5): 865 doi: 10.1109/16.760391[11] Zhou X, Long W. A novel hetero-material gate (HMG) MOSFET for deep-submicron ULSI technology. IEEE Transactions on Electron Devices. 1998, 45(12): 2546 doi: 10.1109/16.735743[12] Amin SI, Sarin RK. Charge-plasma based dual-material and gate-stacked architecture of junctionless transistor for enhanced analog performance. Superlattices Microstruct, 2015, 88: 582 doi: 10.1016/j.spmi.2015.10.017[13] Sharma S K, Raj B, Khosla M. Subthreshold performance of In1-xGax as based dual metal with gate stack cylindrical/surrounding gate nanowire MOSFET for low power analog applications. J Nanoelectron Optoelectron, 2017, 12(2): 171 doi: 10.1166/jno.2017.1961[14] Kumar S, Raj B. Analysis of ION and ambipolar current for dual-material gate-drain overlapped DG-TFET. J Nanoelectron Optoelectron, 2016, 11(3): 323 doi: 10.1166/jno.2016.1902[15] Anand S, Sarin RK. Dual material gate doping-less tunnel FET with hetero gate dielectric for enhancement of analog/RF performance. J Semicond, 2017, 38(2): 024001 doi: 10.1088/1674-4926/38/2/024001 -

Proportional views

DownLoad:

DownLoad: