| Citation: |

Shizhe Wei, Haifeng Wu, Qian Lin, Mingzhe Zhang. A 0.1–1.5 GHz multi-octave quadruple-stacked CMOS power amplifier[J]. Journal of Semiconductors, 2020, 41(6): 062401. doi: 10.1088/1674-4926/41/6/062401

****

S Z Wei, H F Wu, Q Lin, M Z Zhang, A 0.1–1.5 GHz multi-octave quadruple-stacked CMOS power amplifier[J]. J. Semicond., 2020, 41(6): 062401. doi: 10.1088/1674-4926/41/6/062401.

|

A 0.1–1.5 GHz multi-octave quadruple-stacked CMOS power amplifier

DOI: 10.1088/1674-4926/41/6/062401

More Information

-

Abstract

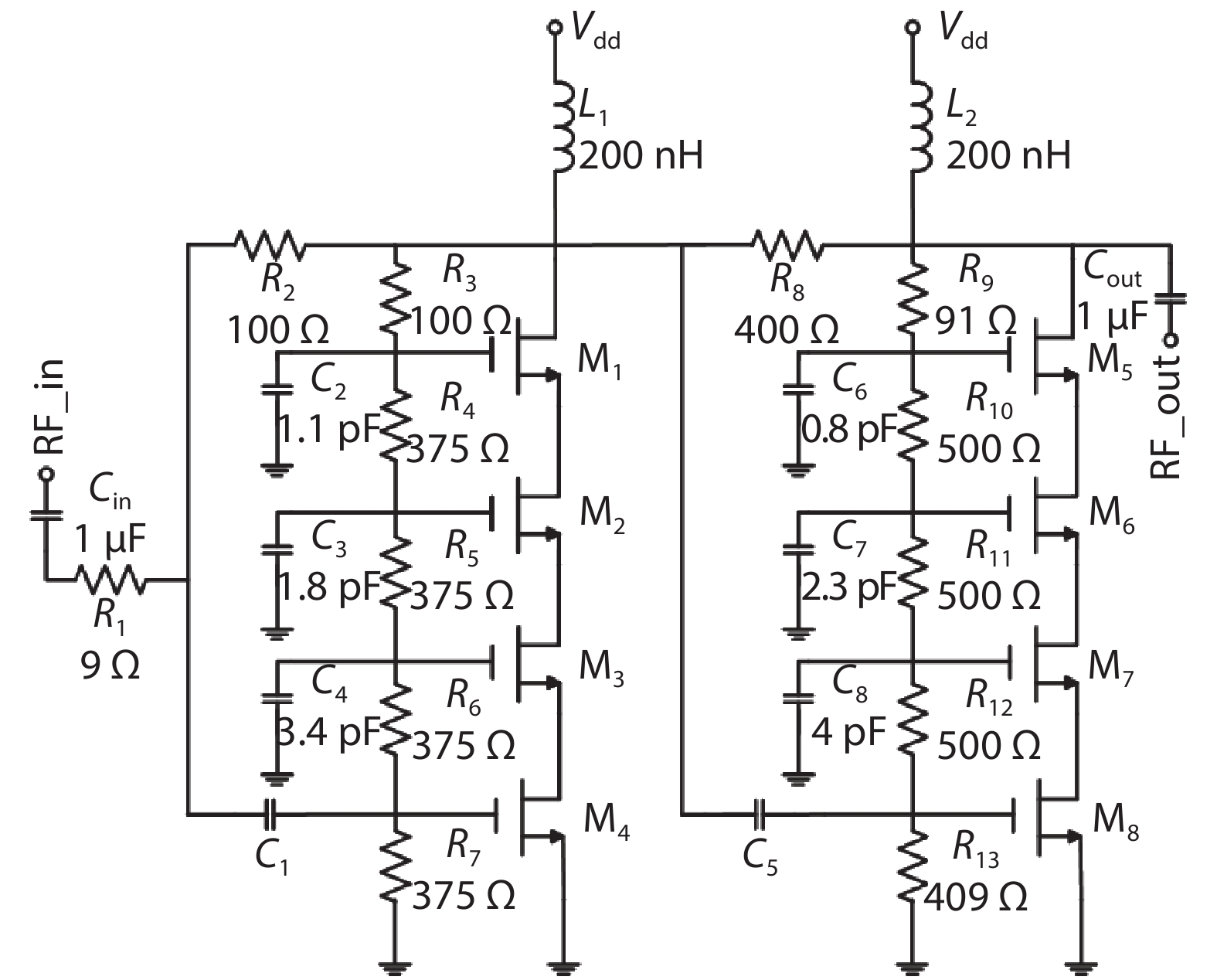

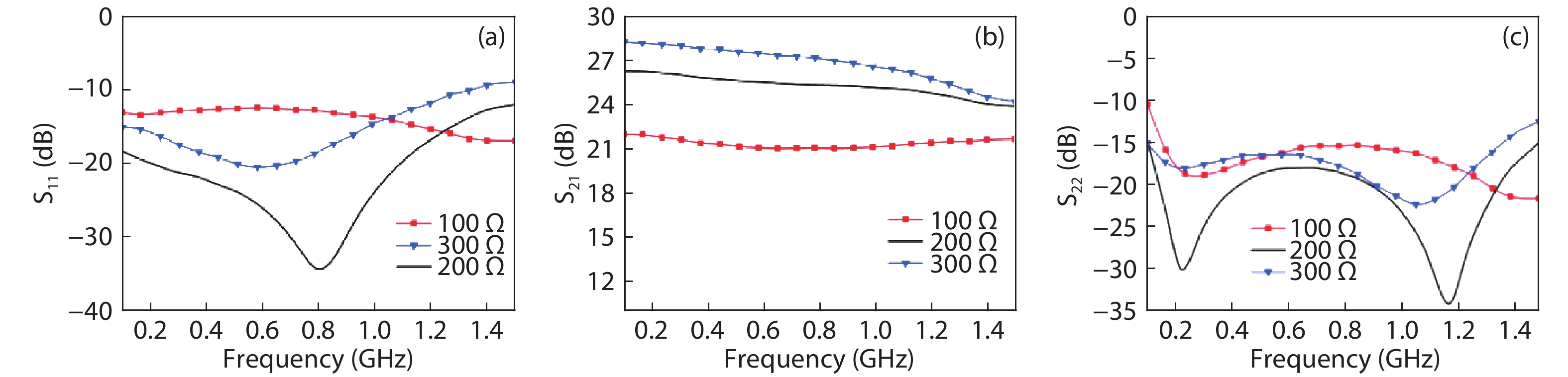

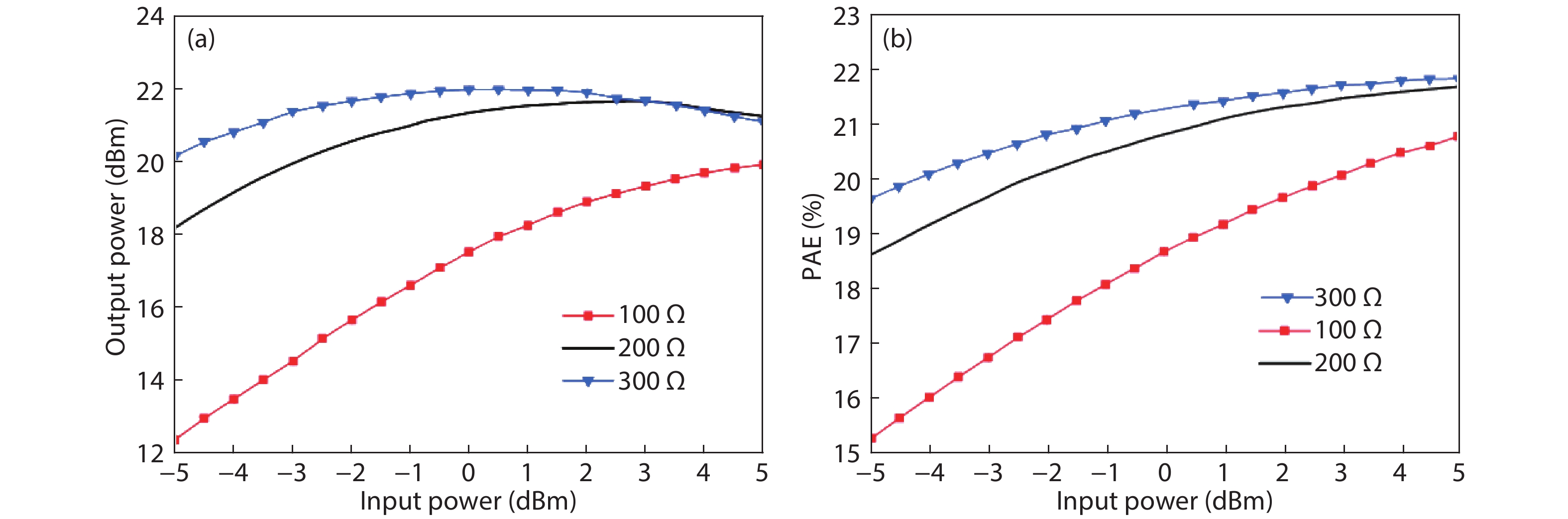

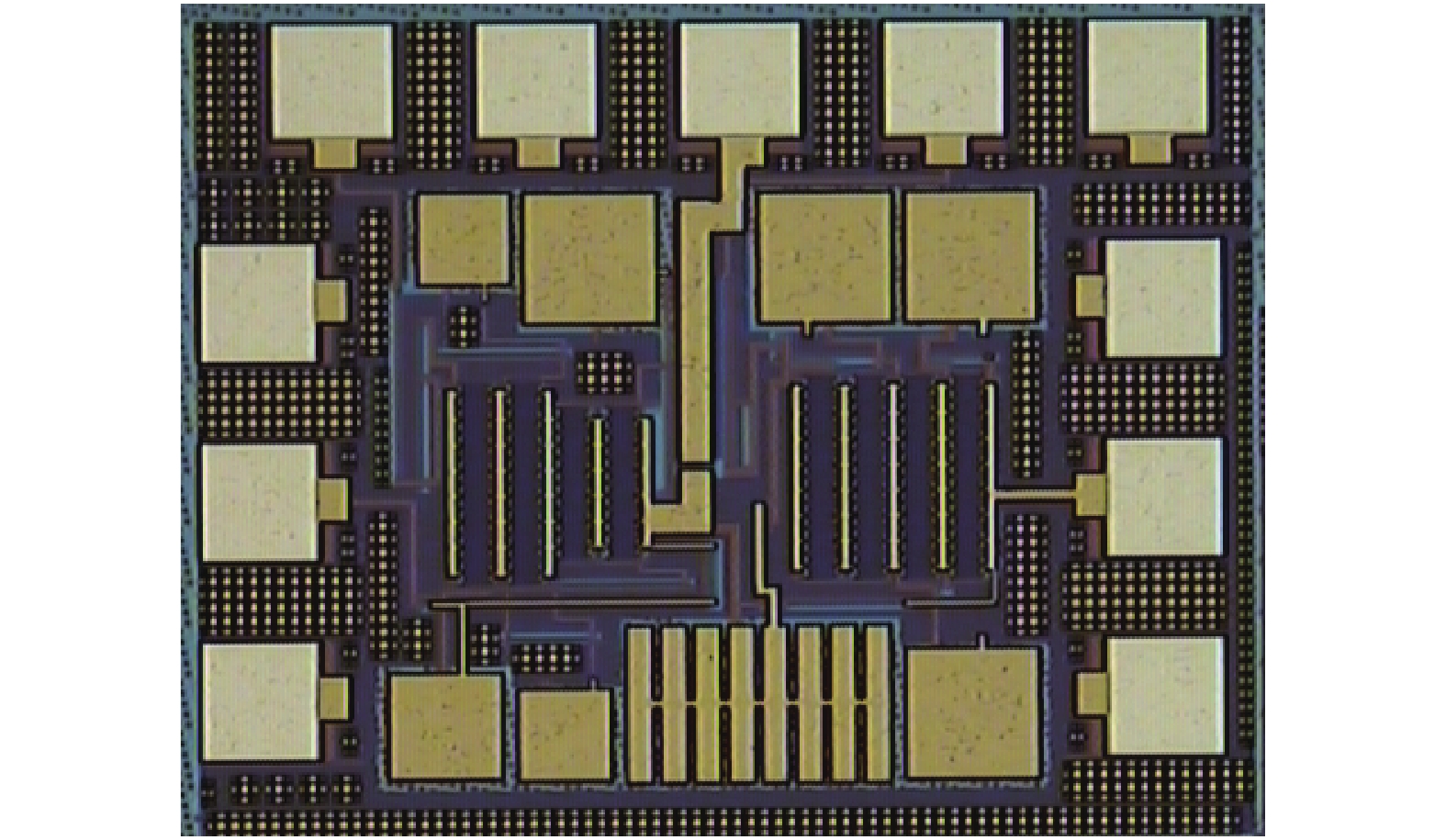

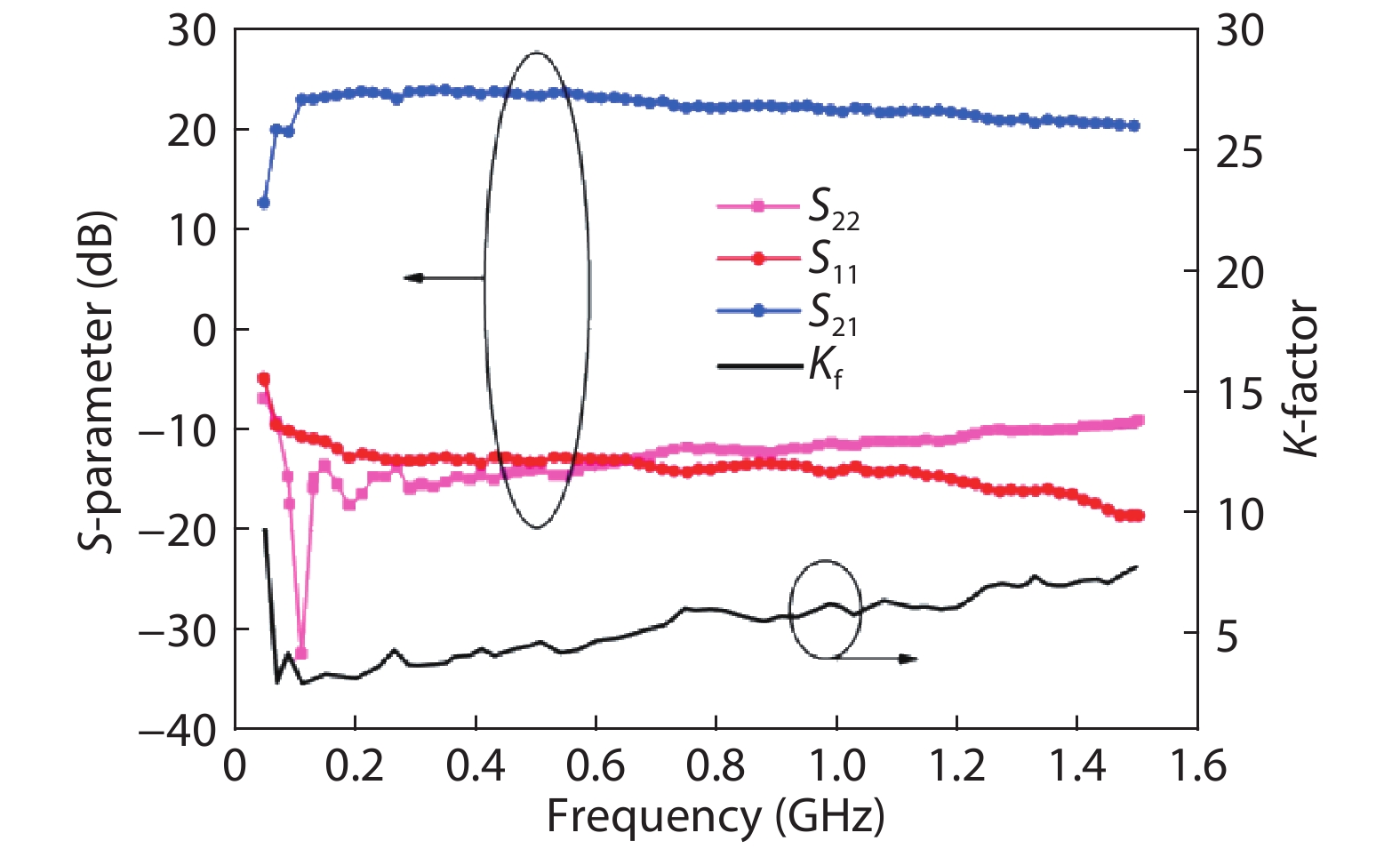

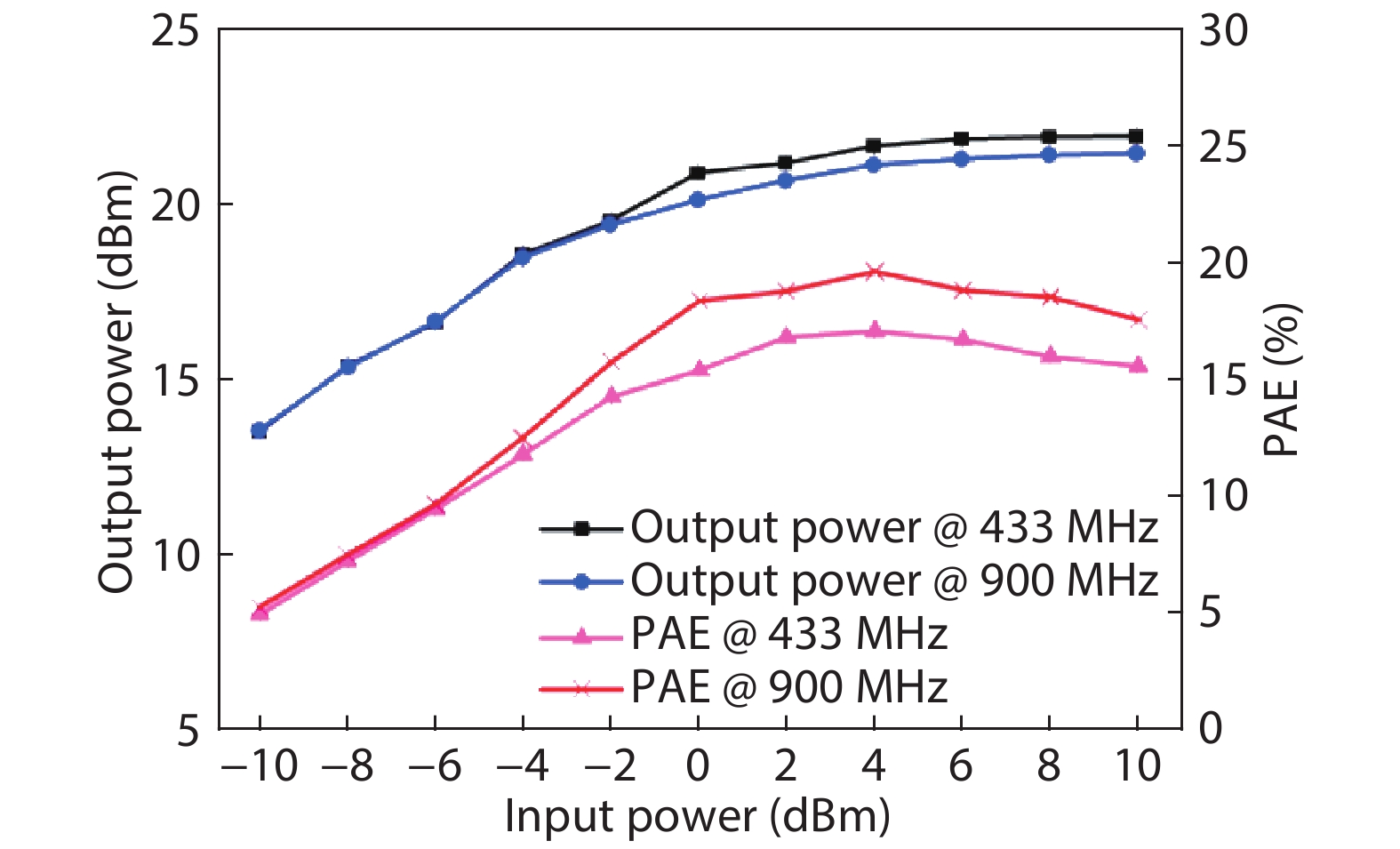

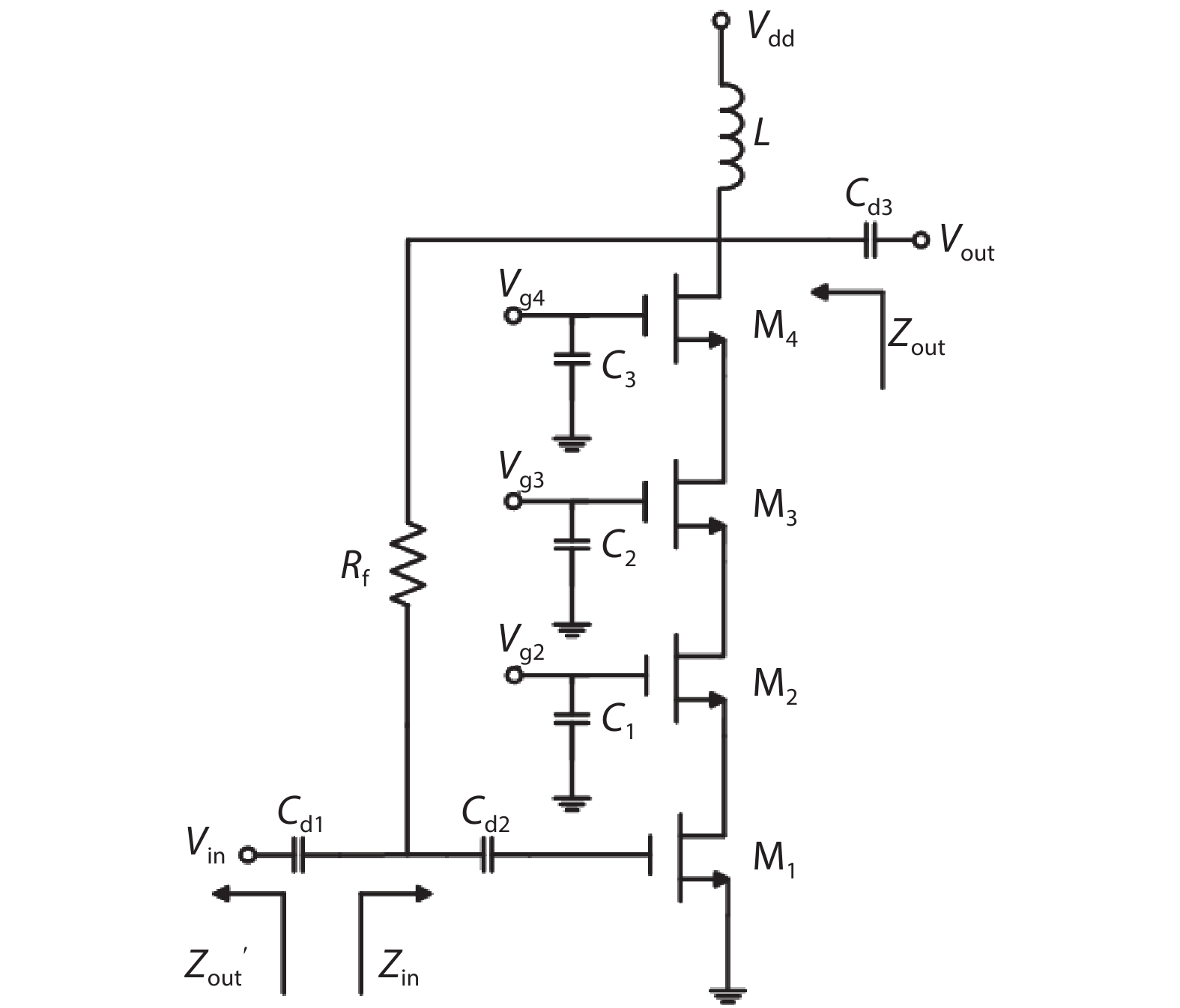

In this letter, we design and analyze 0.1–1.5 GHz multi-octave quadruple-stacked CMOS power amplifier (PA) in 0.18 μm CMOS technology. By using two-stage quadruple-stacked topology and feedback technology, the proposed PA realizes an ultra-wideband CMOS PA in a small chip area. Wideband impedance matching is achieved with smaller chip dimension. The effects of feedback resistors on the RF performance are also discussed for this stacked-FET PA. The PA shows measured input return loss (< –10.8 dB) and output return loss (< –9.6 dB) in the entire bandwidth. A saturated output power of 22 dBm with maximum 20% power added efficiency (PAE) is also measured with the drain voltage at 5 V. The chip size is 0.44 mm2 including all pads.-

Keywords:

- power amplifier,

- CMOS,

- stacked,

- multi-octave,

- resistive matching

-

References

[1] Jin J, Shi J, Ai B L, et al. A highly linear power amplifier for WLAN. J Semicond, 2016, 37(2), 025006 doi: 10.1088/1674-4926/37/2/025006[2] Gong J, Li W, Hu J T, et al. An 8–18 GHz power amplifier with novel gain fluctuation compensation technique in 65 nm CMOS. J Semicond, 2018, 39(12), 125008 doi: 10.1088/1674-4926/39/12/125008[3] Park J S, Wang Y J, Pellerano S, et al. A CMOS wideband current-mode digital polar power amplifier with built-in AM–PM distortion self-compensation. IEEE J Solid-State Circuits, 2018, 53(2), 340 doi: 10.1109/JSSC.2017.2760898[4] Wang H, Sideris C, Hajimiri A, et al. A CMOS broadband power amplifier with a transformer-based high-order output matching network. IEEE J Solid-State Circuits, 2018, 45(12), 2709 doi: 10.1109/jssc.2010.2077171[5] Xia J, Fang X, Boumaiza S. 60-GHz power amplifier in 45-nm SOI-CMOS using stacked transformer-based parallel power combiner. IEEE Microwave Wireless Compons Lett, 2018, 28(8), 711 doi: 10.1109/LMWC.2018.2843160[6] Ahn H T, Allstot D J. A 0.5–8.5-GHz fully differential CMOS distributed amplifier. IEEE J Solid-State Circuits, 2002, 37(8), 985 doi: 10.1109/JSSC.2002.800960[7] Hsu H C, Wang Z W, Ma G K. A low power CMOS full-band UWB power amplifier using wideband RLC matching method. Electron Devices and Solid-State Circuits Conf Dig Tech Papers, 2005, 233[8] Huang P C, Tsai Z M, Lin K Y, et al. A high-efficiency, broadband CMOS power amplifier for cognitive radio applications. Trans Microwave Theory Tech, 2010, 58(12), 3556 doi: 10.1109/TMTT.2010.2086351[9] Chou M L, Wang H K, Chiu H C, et al. A broadband Darlington power amplifier using 0.5 µm GaN-on-SiC HEMT process. 2016 URSI Asia-Pacific Radio Science Conference, 2016, 1947[10] Wu H F, Liao X J, Lin Q, et al. A compact ultrabroadband stacked traveling-wave GaN on Si power amplifier. IEEE Trans Microwave Theory Tech, 2018, 66(7), 3306 doi: 10.1109/TMTT.2018.2828434[11] Thome F, Leuther A, Schlechtweg M, et al. Broadband high-power W-band amplifier MMICs based on stacked-HEMT unit cells. Trans Microwave Theory Tech, 2018, 66(3), 1312 doi: 10.1109/TMTT.2017.2772809[12] Wu C, Lin Y, Hsiao Y, et al. Design of a 60-GHz high-output power stacked- FET power amplifier using transformer-based voltage-type power combining in 65-nm CMOS. Trans Microwave Theory Tech, 2018, 66(10), 4595 doi: 10.1109/TMTT.2018.2859980[13] Pornpromlikit S, Jeong J, Presti C D, et al. A Watt-level stacked-FET linear power amplifier in silicon-on-insulator CMOS. IEEE Trans Microwave Theory Tech, 2010, 58(1), 57 doi: 10.1109/TMTT.2009.2036323[14] Razavi B. Design of analog CMOS integrated circuits. Boston: McGraw-Hill, 2001[15] Dabag H T, Hanafi B, Golcuk F, et al. Analysis and design of stacked-FET millimeter-wave power amplifiers. IEEE Trans Microwave Theory Tech, 2013, 61(4), 1543 doi: 10.1109/TMTT.2013.2247698 -

Proportional views

DownLoad:

DownLoad: