| Citation: |

Qi Zhao, Ran Li, Dong Qiu, Ting Yi, Yang Liu Bill, Zhiliang Hong. A 14-bit 1-GS/s DAC with a programmable interpolation filter in 65 nm CMOS[J]. Journal of Semiconductors, 2013, 34(2): 025004. doi: 10.1088/1674-4926/34/2/025004

****

Q Zhao, R Li, D Qiu, T Yi, Y L Bill, Z L Hong. A 14-bit 1-GS/s DAC with a programmable interpolation filter in 65 nm CMOS[J]. J. Semicond., 2013, 34(2): 025004. doi: 10.1088/1674-4926/34/2/025004.

|

A 14-bit 1-GS/s DAC with a programmable interpolation filter in 65 nm CMOS

DOI: 10.1088/1674-4926/34/2/025004

More Information

-

Abstract

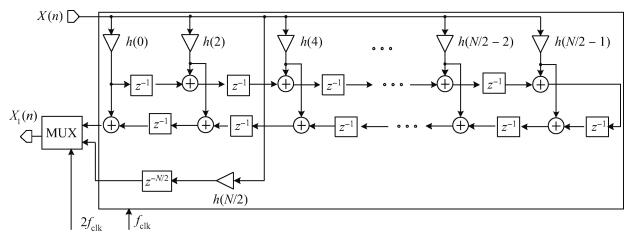

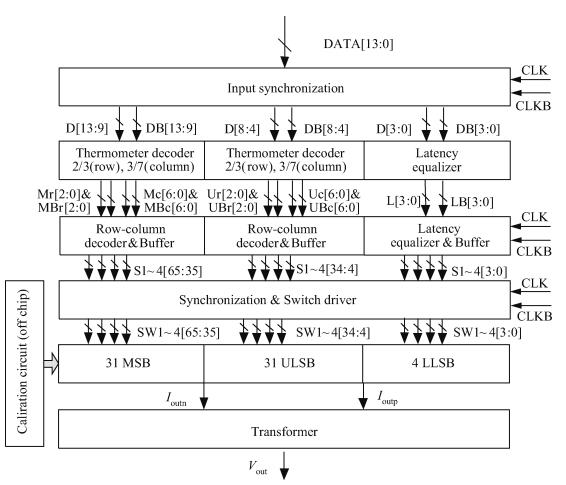

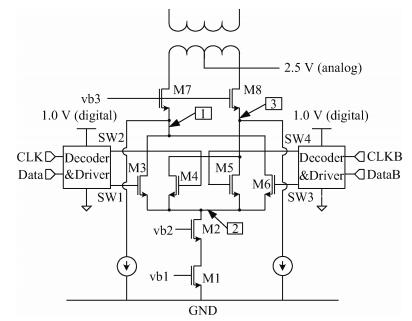

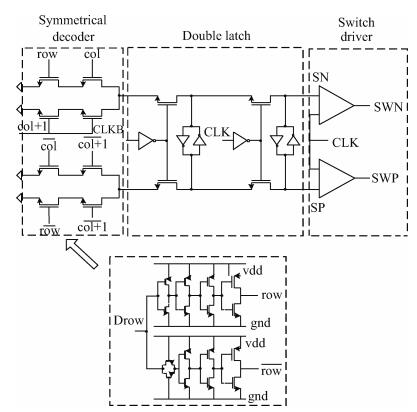

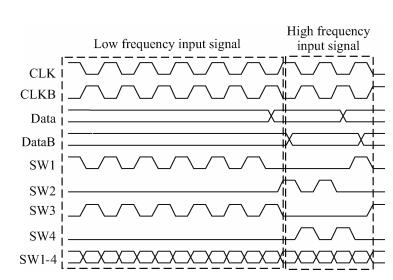

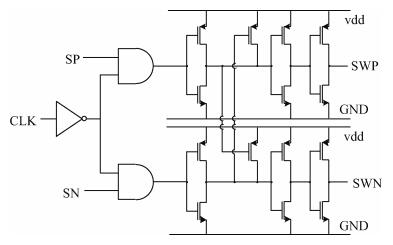

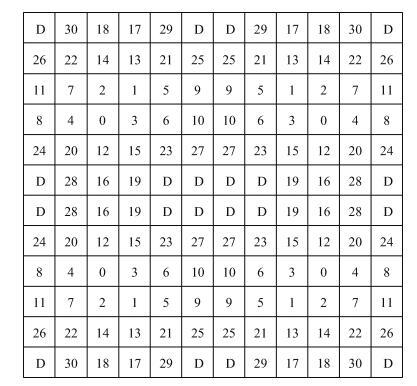

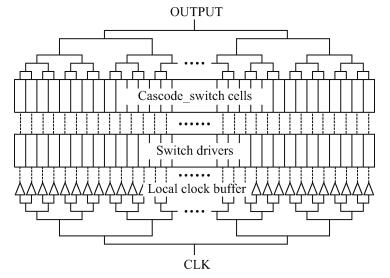

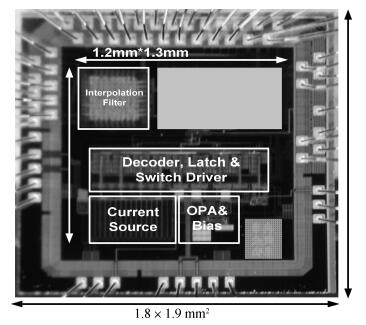

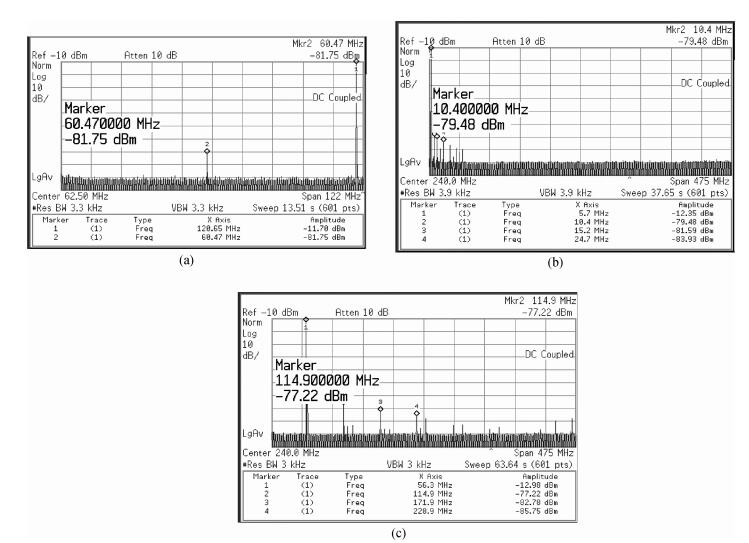

A programmable 14-bit 1-GS/s current-steering digital-to-analog converter is presented. It features a selectable interpolation rate (2x/4x/8x) with a programmable interpolation filter. To improve the high-frequency performance, a "fast switching" technique that adds additional biasing to the current-switch is adopted. The data-dependent clock loading effect is also minimized with an improved switch control by using a double latch. This DAC is implemented in 65 nm CMOS technology with an active area of 1.56 mm2. The measured SFDRs are 70.05 dB at 250 MS/s for 120.65 MHz input sine-wave signal and 64.24 dB at 960 MS/s for 56.3 MHz input sine-wave signal, respectively.-

Keywords:

- DAC,

- high speed,

- high resolution,

- programmable

-

References

[1] Huang Q, Francese P A, Martelli C, et al. A 200 MS/s 14 b 97 mW DAC in 0.18μm CMOS. ISSCC Dig Tech Papers, 2004:364 doi: 10.1007/978-3-642-31229-8_6/fulltext.html[2] Chan K L, Galton L. A 14 b 100 MS/s DAC with fully segmented dynamic element matching. ISSCC Dig Tech Papers, 2006:582[3] Tseng W H. A 12 b 1.25 GS/s DAC in 90 nm CMOS with >70 dB SFDR up to 500 MHz. ISSCC Dig Tech Papers, 2011:192 http://www.wenkuxiazai.com/doc/1ae59ba226fff705cd170a3f.html[4] Tseng W H, Wu J T, Chu Y C. A CMOS 8-bit 1.6-GS/s DAC with digital random return to zero. IEEE Trans Circuits Syst I, 2011, 58(1):1 doi: 10.1109/TCSI.2010.2097652[5] Van den Bosch A, Borremans M A F, Steyaert M S J, et al. A 10-ewpage bit 1-GSample/s Nyquist current-steering CMOS D/A converter. IEEE J Solid-State Circuits, 2001, 36(3):315 doi: 10.1109/4.910469[6] Lin C H, van der Goes F M L, Westra J R, et al. A 12 bit 2.9 GS/s DAC with IM3<-60 dBc beyond 1 GHz in 65 nm CMOS. IEEE J Solid-State Circuits, 2009, 44(12):3285 doi: 10.1109/JSSC.2009.2032624[7] Palimers P, Steyaert M S J. A 10-bit 1.6-GS/s 27-mW current-steering D/A converter with 550-MHz 54-dB SFDR bandwidth in 130-nm CMOS. IEEE Trans Circuits Syst I, 2010, 57(11):2870 doi: 10.1109/TCSI.2010.2052491[8] Mercer D A. Low-power approaches to high-speed current-steering digital-to-analog converters in 0.18μm CMOS. IEEE J Solid-State Circuits, 2007, 42(8):1688 doi: 10.1109/JSSC.2007.900279[9] Schafferer B, Adams R. A 3 V CMOS 400 mW 14 b 1.4 GS/s DAC for multi-carrier applications. ISSCC Dig Tech Papers, 2004:360 doi: 10.1007/978-3-642-31600-5_60[10] Cong Y, Geiger R L. Switching sequence optimization for gradient error compensation in thermometer-decoded DAC arrays. IEEE Trans Circuits Syst I, 2000, 47(7):589 http://www.oalib.com/paper/1520860 -

Proportional views

DownLoad:

DownLoad: