| Citation: |

Jianjun Wei, Hanjun Jiang, Lingwei Zhang, Jingjing Dong, Fule Li, Zhihua Wang, Chun Zhang. A wide range sigma-delta fractional-N frequency synthesizer with adaptive frequency calibration[J]. Journal of Semiconductors, 2013, 34(6): 065002. doi: 10.1088/1674-4926/34/6/065002

****

J J Wei, H J Jiang, L W Zhang, J J Dong, F L Li, Z H Wang, C Zhang. A wide range sigma-delta fractional-N frequency synthesizer with adaptive frequency calibration[J]. J. Semicond., 2013, 34(6): 065002. doi: 10.1088/1674-4926/34/6/065002.

|

A wide range sigma-delta fractional-N frequency synthesizer with adaptive frequency calibration

DOI: 10.1088/1674-4926/34/6/065002

More Information

-

Abstract

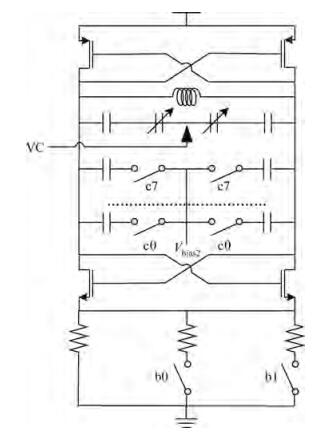

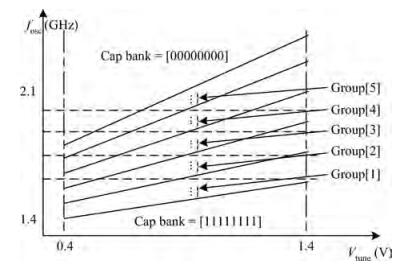

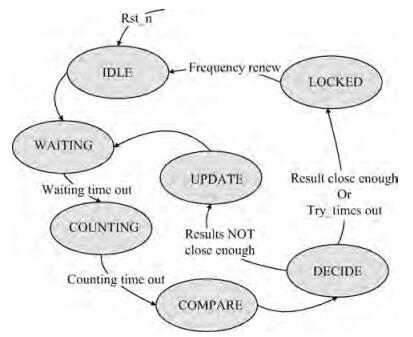

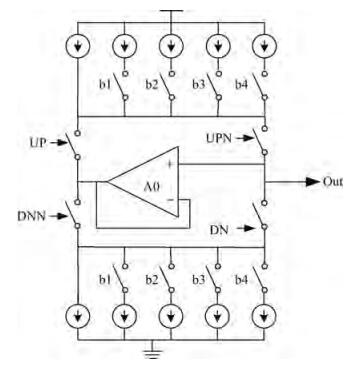

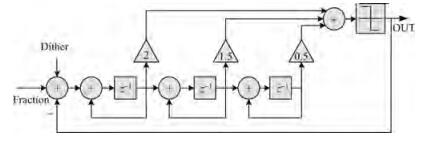

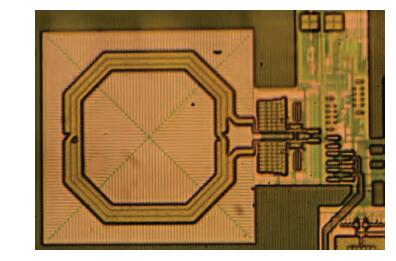

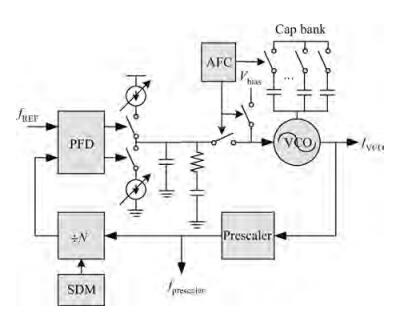

A wide range fractional-N frequency synthesizer in 0.18 μm RF CMOS technology is implemented. A switched-capacitors bank LC-tank VCO and an adaptive frequency calibration technique are used to expand the frequency range. A 16-bit third-order sigma-delta modulator with dither is used to randomize the fractional spur. The active area is 0.6 mm2. The experimental results show the proposed frequency synthesizer consumes 4.3 mA from a single 1.8 V supply voltage except for buffers. The frequency range is 1.44-2.11 GHz and the frequency resolution is less than 0.4 kHz. The phase noise is-94 dBc/Hz@100 kHz and-121 dBc/Hz@1 MHz at the output of the prescaler with a loop bandwidth of approximately 120 kHz. The performance meets the requirements for the multi-band and multi-mode transceiver applications. -

References

[1] Shin J. A 1.9-3.8 GHz fractional-N PLL frequency synthesizer with fast auto-calibration of loop bandwidth and VCO frequency. IEEE J Solid-State Circuits, 2012, 47:665 doi: 10.1109/JSSC.2011.2179733[2] Shanan H, Retz G. A 2.4 GHz 2 Mb/s versatile PLL-based transmitter using digital pre-emphasis and auto calibration in 0.18μm CMOS for WPAN. IEEE Int Solid-State Circuits Conf Dig, 2009:420 https://es.scribd.com/document/192715914/Acronyms-A4-Duplex[3] Chen N. Low phase noise and linear gain VCO using self-switched biasing. IEEE International Symposium on Radio-Frequency Integration Technology, 2011:137[4] Moon Y J. A 4.39-5.26 GHz LC-tank CMOS voltage-controlled oscillator with small VCO-gain variation. IEEE Microw Wireless Compon Lett, 2009, 19:524 doi: 10.1109/LMWC.2009.2024846[5] Hauspie D, Park E C, Craninckx J. Wide-band VCO with simultaneous switching of frequency band, active core, and varactor size. IEEE J Solid-State Circuits, 2007, 42:1472 doi: 10.1109/JSSC.2007.899105[6] Lou L, Sun L, Gao H, et al. A 0.68-1.65 GHz CMOS LC voltage-controlled oscillator with small VCO-gain and step variation. 201113th International Symposium on Integrated Circuits (ISIC), 2011:79[7] Lee H. A Σ-Δ fractional frequency synthesizer using a wide-band integrated VCO and a fast AFC technique for GSM/GPRS/WCDMA applications. IEEE J Solid-State Circuits, 2004, 39:1164 doi: 10.1109/JSSC.2004.829938[8] Pellerano S, Levantino S, Samori C, et al. A 13.5 mW 5 GHz frequency synthesizer with dynamic-logic frequency divider. IEEE J Solid-State Circuits, 2004, 39:378 doi: 10.1109/JSSC.2003.821784[9] Shin J, Shin H. A fast and high-precision VCO frequency calibration technique for wideband fractional-N frequency synthesizers. IEEE Trans Circuits Syst I: Regular Papers, 2010, 57(7): 1573[10] Jeong C Y, Choi D H, Yoo C. A fast automatic frequency calibration (AFC) scheme for phase-locked loop (PLL) frequency synthesizer. IEEE Radio Frequency Integrated Circuits Symposium, 2009: 583[11] Kim M, Lee K, Kwon Y. 5-GHz frequency synthesizer with auto-calibration loop. IEEE Radio Frequency Integrated Circuits Symposium, 2007:713 -

Proportional views

DownLoad:

DownLoad: