| Citation: |

Jun Liu, Jincai Wen, Qian Zhao, Lingling Sun. A novel compact model for on-chip stacked transformers in RF-CMOS technology[J]. Journal of Semiconductors, 2013, 34(8): 084006. doi: 10.1088/1674-4926/34/8/084006

****

J Liu, J C Wen, Q Zhao, L L Sun. A novel compact model for on-chip stacked transformers in RF-CMOS technology[J]. J. Semicond., 2013, 34(8): 084006. doi: 10.1088/1674-4926/34/8/084006.

|

A novel compact model for on-chip stacked transformers in RF-CMOS technology

DOI: 10.1088/1674-4926/34/8/084006

More Information

-

Abstract

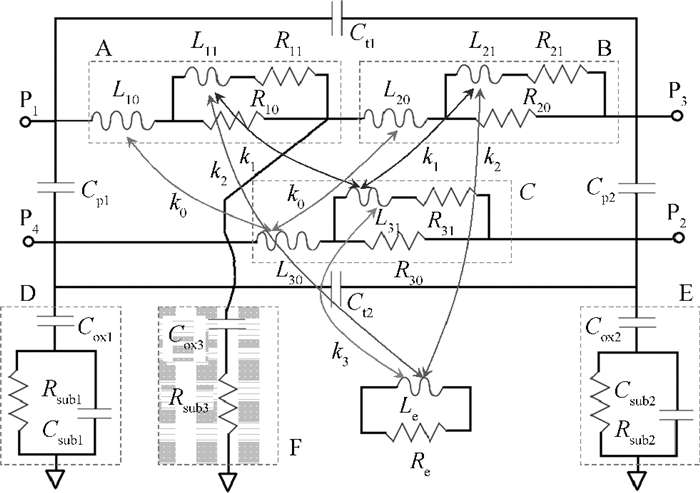

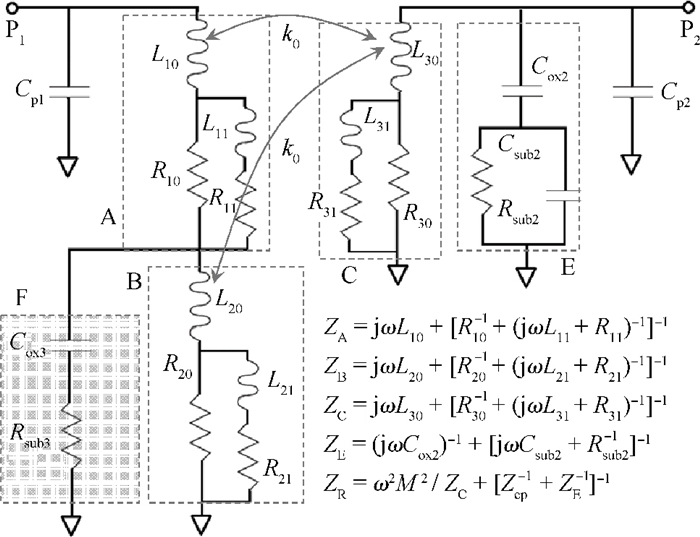

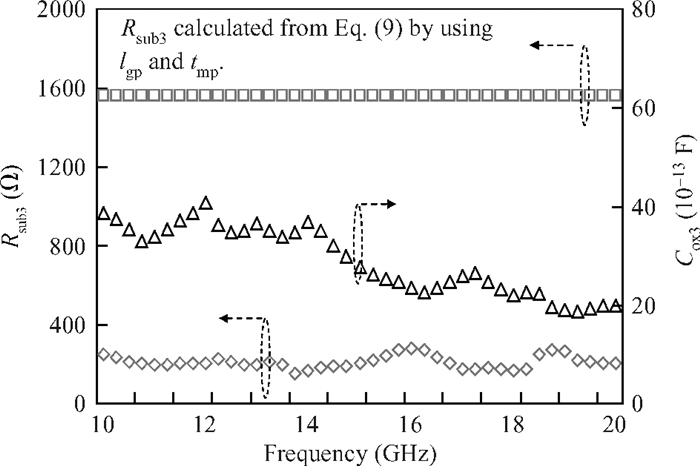

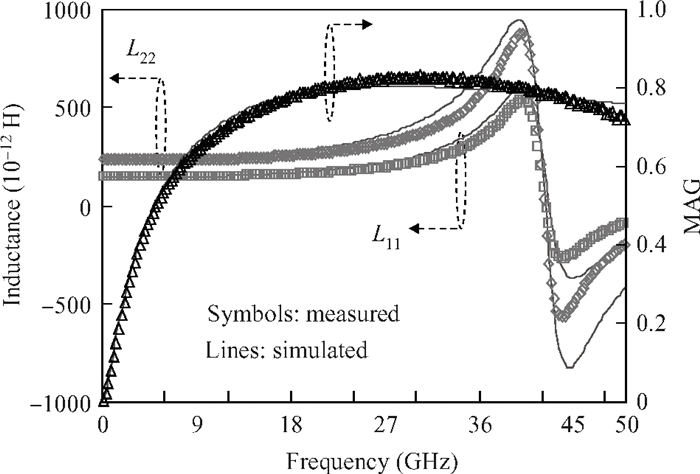

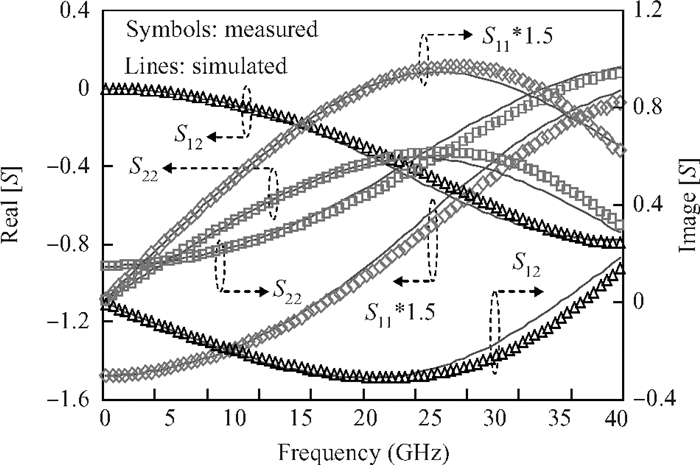

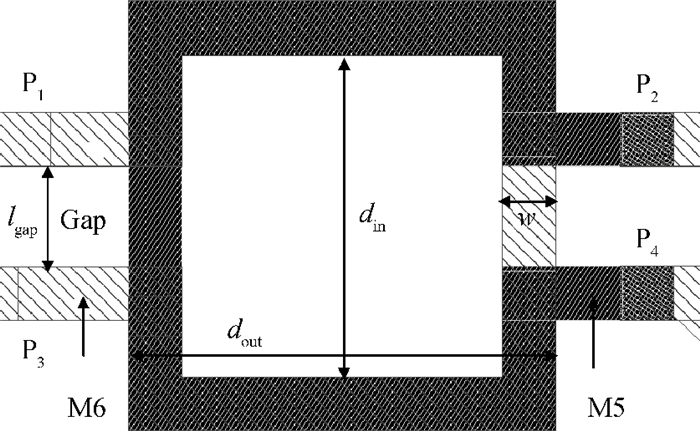

A novel compact model for on-chip stacked transformers is presented. The proposed model topology gives a clear distinction to the eddy current, resistive and capacitive losses of the primary and secondary coils in the substrate. A method to analytically determine the non-ideal parasitics between the primary coil and substrate is provided. The model is further verified by the excellent match between the measured and simulated S-parameters on the extracted parameters for a 1:1 stacked transformer manufactured in a commercial RF-CMOS technology.-

Keywords:

- on-chip,

- stacked transformer,

- compact model

-

References

[1] Zolfaghari A, Chan A, Razavi B. Stacked inductors and transformers in CMOS technology. IEEE J Solid-State Circuits, 200136(4):620 doi: 10.1109/4.913740[2] Cen C, Lin Y, Chen C, et al. High-coupling and ultra-low-loss interlaced stacked transformers for 60-100 GHz CMOS RFIC applications. IEEE Radio and Wireless Symposium, 2007:357 http://ieeexplore.ieee.org/document/4160725/?reload=true&arnumber=4160725&contentType=Conference%20Publications[3] Fong N, Plouchart J O, Zamdmer N, et al. High-performance and area-efficient stacked transformers for RF CMOS integrated circuits. IEEE MTT-S International Microwave Symposium, 2003, 2:967 http://ieeexplore.ieee.org/document/1212530/?arnumber=1212530[4] Gao W, Jiao C, Liu T, et al. Scalable compact circuit model for differential spiral transformers in CMOS RFICs. IEEE Trans Electron Devices, 2006, 53(9):2187 doi: 10.1109/TED.2006.880230[5] Lim C C, Yeo K S, Chew K W, et al. Fully symmetrical monolithic transformer (true 1:1) for silicon RFIC. IEEE Trans Microw Theory Tech, 2008, 56(10):2301 doi: 10.1109/TMTT.2008.2003531[6] Biondi T, Scuderi A, Ragonese E, et al. Analysis and modeling of layout scaling in silicon integrated stacked transformers. IEEE Trans Microw Theory Tech, 2006, 54(5):2203 doi: 10.1109/TMTT.2006.872788[7] Mayevskiy Y, Watson A, Francis P, et al. A new compact model for monolithic transformers in silicon-based RFICs. IEEE Microw Wireless Compon Lett, 2005, 15(6):419 doi: 10.1109/LMWC.2005.850558[8] Chuan W, Liao H, Yongzhong X, et al. A physics-based equivalent-circuit model for on-chip symmetric transformers with accurate substrate modeling. IEEE Trans Microw Theory Tech, 2009, 57(4):980 doi: 10.1109/TMTT.2009.2014479[9] Arcioni P, Castello R, Perregrini L, et al. An innovative modelization of loss mechanism in silicon integrated inductors. IEEE Trans Circuits Syst Ⅱ, 1999, 46(12):1453 doi: 10.1109/82.809531[10] Chuan W, Liao H, Li C, et al. A wideband predictive double-π equivalent-circuit model for on-chip spiral inductors. IEEE Trans Electron Devices, 2009, 56(4):609 doi: 10.1109/TED.2009.2014184[11] Jun L, Lin Z, Huang W, et al. Double-fully scalable model for on-chip spiral inductors. Journal of Semiconductors, 2012, 33(8):084007 doi: 10.1088/1674-4926/33/8/084007 -

Proportional views

DownLoad:

DownLoad: