| Citation: |

Songting Li, Jiancheng Li, Xiaochen Gu, Hongyi Wang, Zhaowen Zhuang. A high linearity downconverter for digital broadcasting system[J]. Journal of Semiconductors, 2014, 35(12): 125010. doi: 10.1088/1674-4926/35/12/125010

****

S T Li, J C Li, X C Gu, H Y Wang, Z W Zhuang. A high linearity downconverter for digital broadcasting system[J]. J. Semicond., 2014, 35(12): 125010. doi: 10.1088/1674-4926/35/12/125010.

|

A high linearity downconverter for digital broadcasting system

DOI: 10.1088/1674-4926/35/12/125010

More Information

-

Abstract

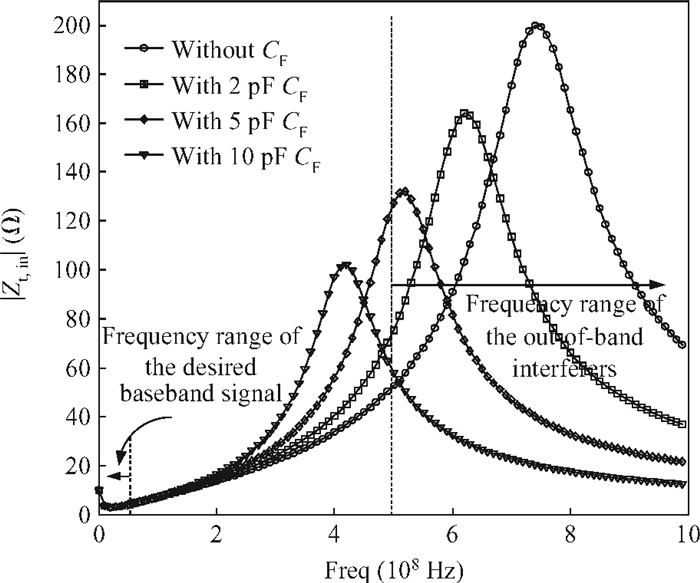

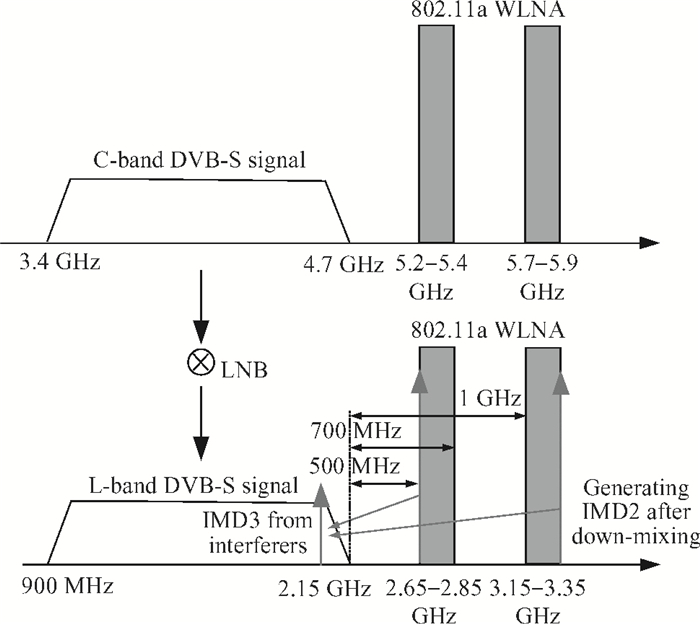

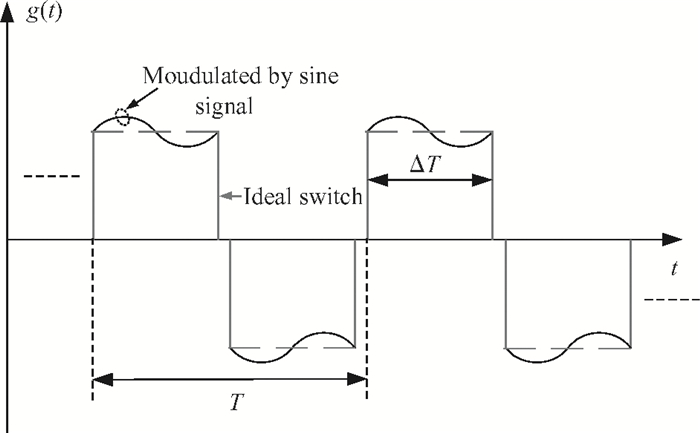

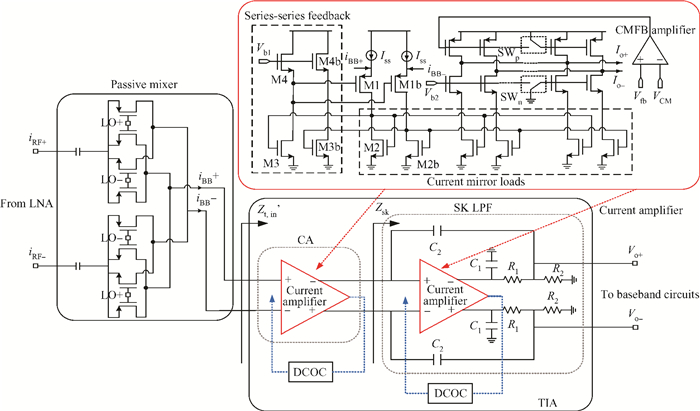

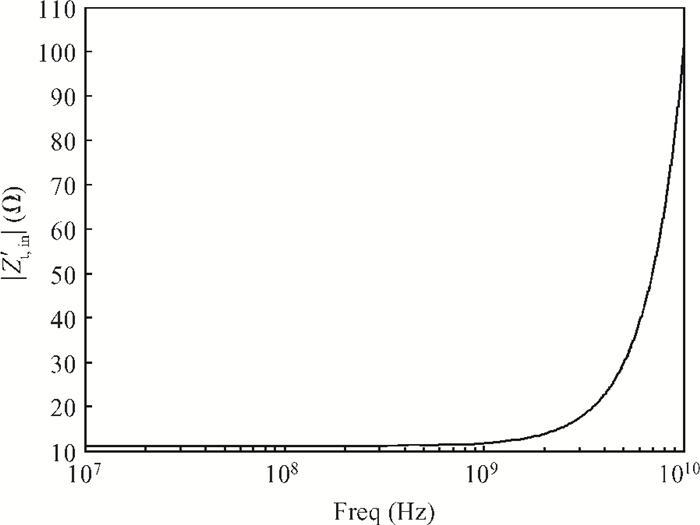

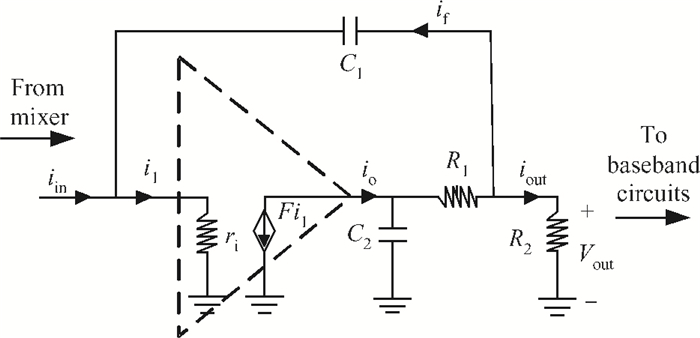

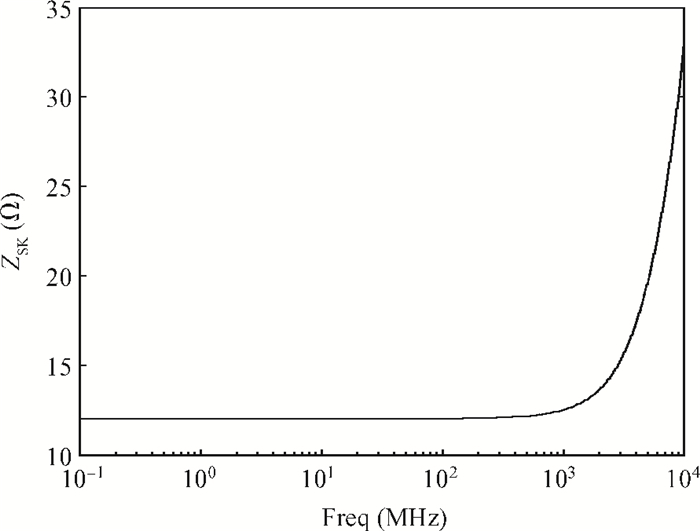

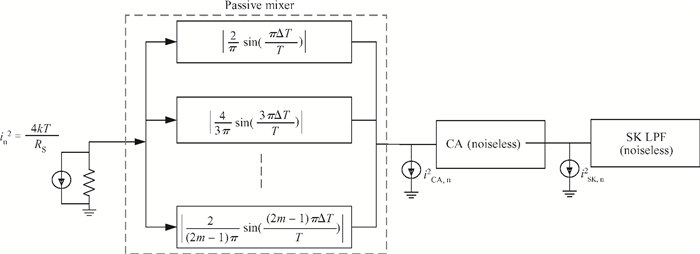

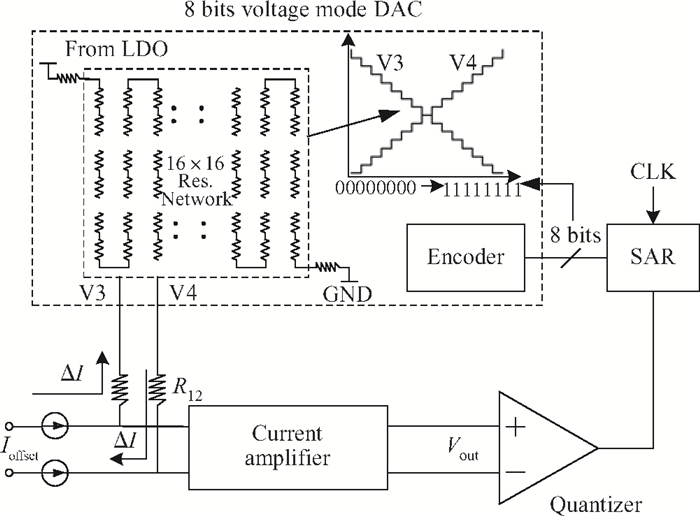

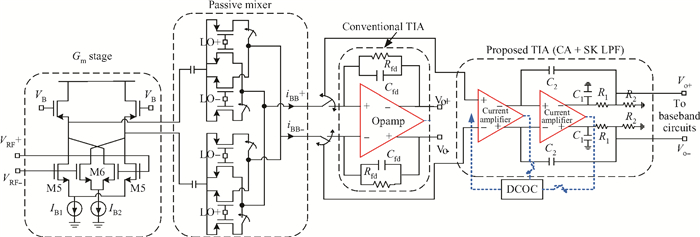

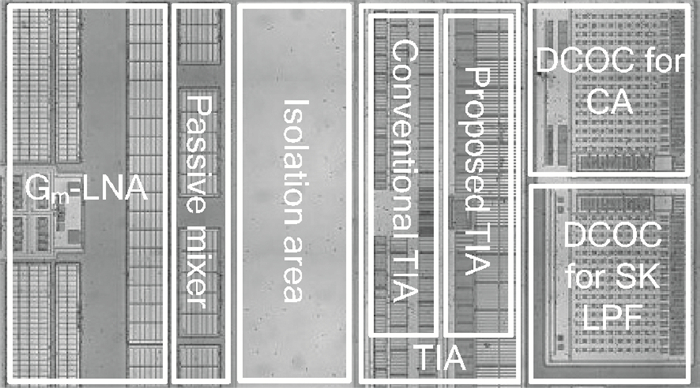

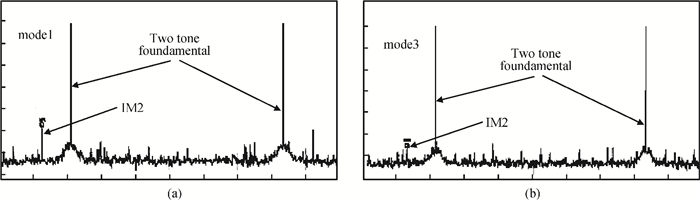

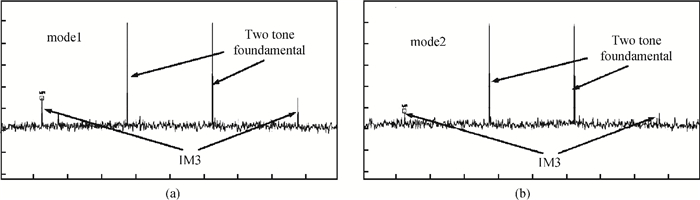

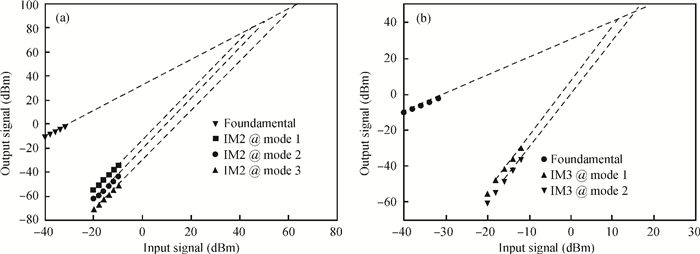

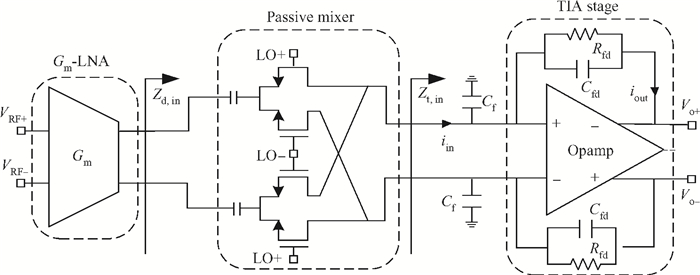

An integrated downconverter with high linearity for digital broadcasting system receivers is implemented in a 0.13 μm CMOS process with an active area of 0.1 mm2. The current-mode scheme is adopted to improve linearity performance by avoiding voltage fluctuation. A passive CMOS switching pair is utilized to improve the even-order linearity of the downconverter. A current amplifier is used to provide low input impedance which will easily lead to a wide operating bandwidth and high linearity. Moreover, a current-mode Sallen-Key low-pass filter is adopted for effective rejection of out-of-band interferers and also low input impedance. The digital-assisted DC offset calibration improves the second-order distortion of the downconverter. This design achieves a maximum gain of 40 dB and a dynamic range of 10 dB. Measured noise figure is 8.2 dB, an ⅡP2 of 63 dBm, an ⅡP3 of 17 dBm at the minimum gain of 30 dB. The downconverter consumes about 7.7 mA under a supply of 1.2 V. -

References

[1] Kuo M C, Kao S W, Chen C H, et al. A 1.2 V 114 mW dual-band direct-conversion DVB-H tuner in 0.13μm CMOS. IEEE J Solid-State Circuits, 2009, 44:740 doi: 10.1109/JSSC.2008.2012366[2] Iason V, Kostis V, Nikos H, et al. A 65 nm CMOS multistandard, multiband TV tuner for mobile and multimedia applications. IEEE J Solid-State Circuits, 2008, 43:1522 doi: 10.1109/JSSC.2008.923721[3] Yaduru N, Griffith D, Bhagavatheeswaran S, et al. A WCDMA, GSM/GPRS/EDGE receiver front end without interstage SAW filter. IEEE RFIC Symp, 2006:77 http://ewh.ieee.org/soc/cas/dallas/documents/Sem-062107-yanduru.pdf[4] Ingels M, Giannini V, Borremans J, et al. A 5 mm2 40 nm LP CMOS 0.1-to-3 GHz multistandard transceiver. IEEE Int Solid-State Circuits Conf, 2010:458[5] Namsoo K, Vladimir A, Lawrence E L. A resistively degenerated wide-band passive mixer with low noise figure and high ⅡP2. IEEE Trans Microw Theory Tech, 2010, 58:820 doi: 10.1109/TMTT.2010.2042644[6] Zhou S, Chang M C. A CMOS passive mixer with low flicker noise for low-power direct-conversion receiver. IEEE J Solid-State Circuits, 2009, 40:1088 http://ieeexplore.ieee.org/document/1425716/[7] Shin H Y, Kuo C N, Chen W H, et al. A 250 MHz 14 dB-NF 73 dB-gain 82dB-DR analog baseband chain with digital-assisted DC-Offset calibration for ultra-wideband. IEEE J Solid-State Circuits, 2010, 45:338 doi: 10.1109/JSSC.2009.2036320[8] Dufrene K, Boos Z, Weigel R. Digital adaptive ⅡP2 calibration scheme for CMOS down conversion mixers. IEEE J Solid-State Circuits, 2008, 43:2434 doi: 10.1109/JSSC.2008.2005453[9] Chakib B, Serge T, Tchanguiz R. A broadband highly linear BiCMOS mixer for direct conversion applications. IEEE Microw Wireless Compen Lett, 2004, 14:374 doi: 10.1109/LMWC.2004.832624[10] Nuntachai P, Chen W H, Zdravko B, et al. A 1.5-V 0.7-2.5-GHz CMOS quadrature demodulator for multiband direct-conversion receivers. IEEE J Solid-State Circuits, 2007, 42:1669 doi: 10.1109/JSSC.2007.900294[11] Wu J M, Ye R F, Horng T S. A high ⅡP2 Gilbert mixer-based downconverter design for direct-conversion WiMAX receivers. IEEE Radio Microwave Symp, 2010:404 http://ieeexplore.ieee.org/document/5434233/[12] Khatri H, Gudem P S, Larson L E. Distortion in current commutating passive CMOS downconversion mixers. IEEE Trans Microw Theory Tech, 2009, 57:2671 doi: 10.1109/TMTT.2009.2031930[13] Manstretta D, Brandolini M, Svelto F. Second-order intermodulation mechanisms in CMOS downconverters. IEEE J Solid-State Circuits, 2003, 38:394 doi: 10.1109/JSSC.2002.808310[14] Li S T, Li J C, Gu X C, et al. A continuously and widely tunable analog baseband chain with digital-assisted calibration for multi-standard DBS applications. Journal of Semiconductors, 2013, 34:065009 doi: 10.1088/1674-4926/34/6/065009[15] Barrie G. A precise four-quadrant multiplier with subnanosecond response. IEEE J Solid-State Circuits, 1968, 3:365 doi: 10.1109/JSSC.1968.1049925 -

Proportional views

DownLoad:

DownLoad: