| Citation: |

Ning Xu, Fule Li, Chun Zhang, Zhihua Wang. An IP-oriented 11-bit 160 MS/s 2-channel current-steering DAC[J]. Journal of Semiconductors, 2014, 35(12): 125011. doi: 10.1088/1674-4926/35/12/125011

****

N Xu, F L Li, C Zhang, Z H Wang. An IP-oriented 11-bit 160 MS/s 2-channel current-steering DAC[J]. J. Semicond., 2014, 35(12): 125011. doi: 10.1088/1674-4926/35/12/125011.

|

An IP-oriented 11-bit 160 MS/s 2-channel current-steering DAC

DOI: 10.1088/1674-4926/35/12/125011

More Information

-

Abstract

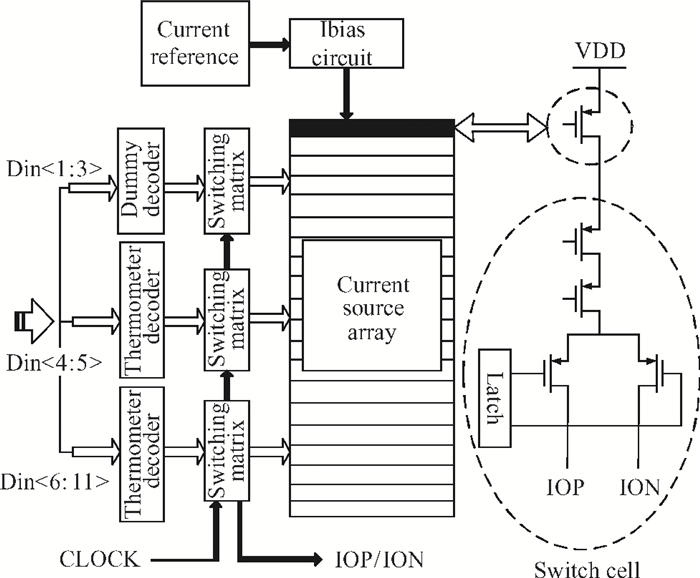

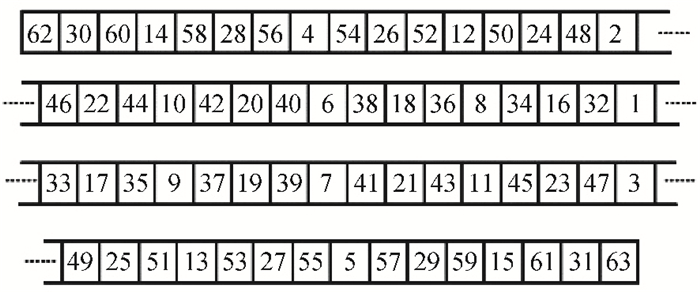

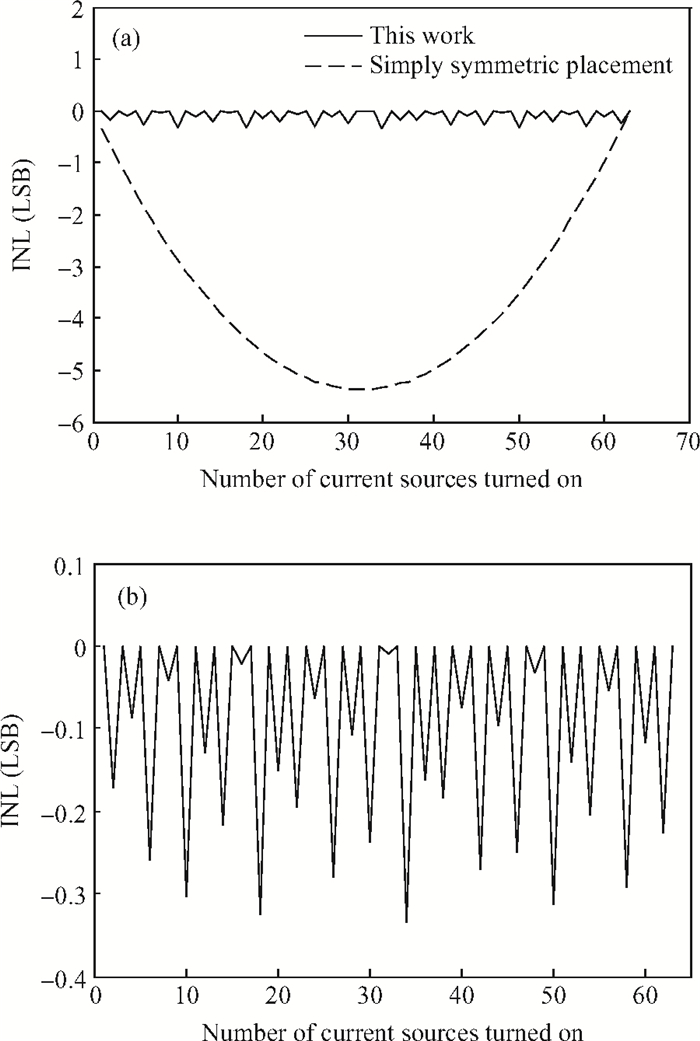

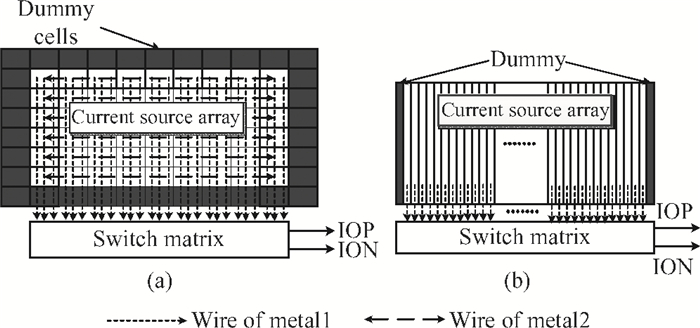

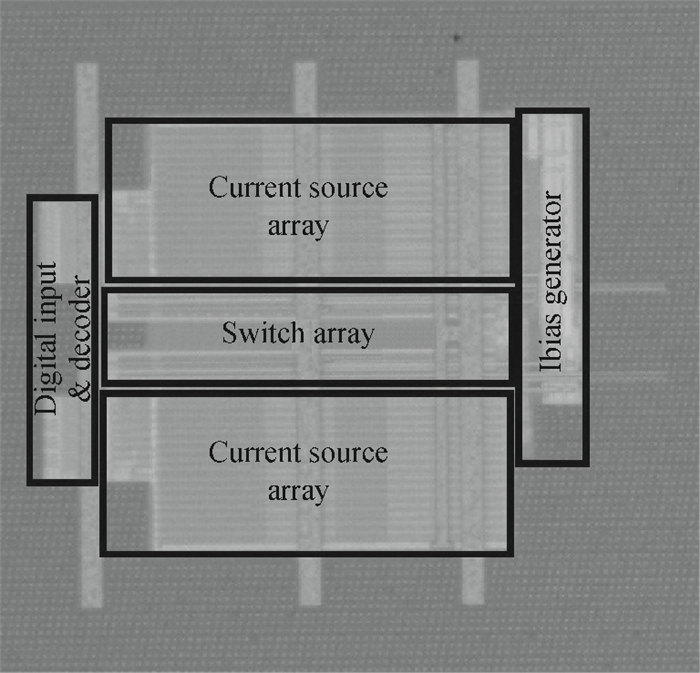

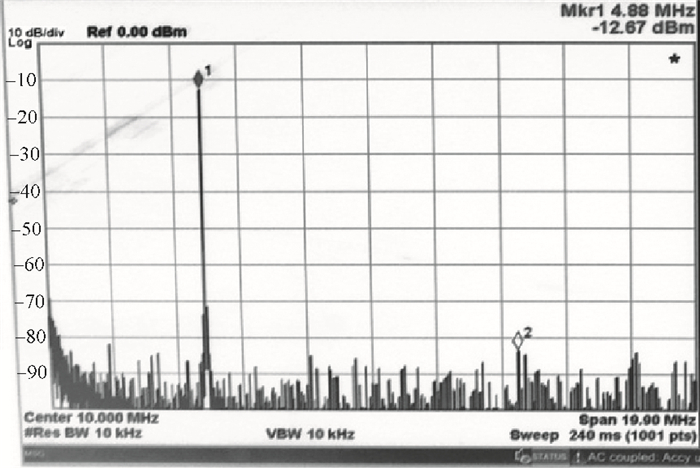

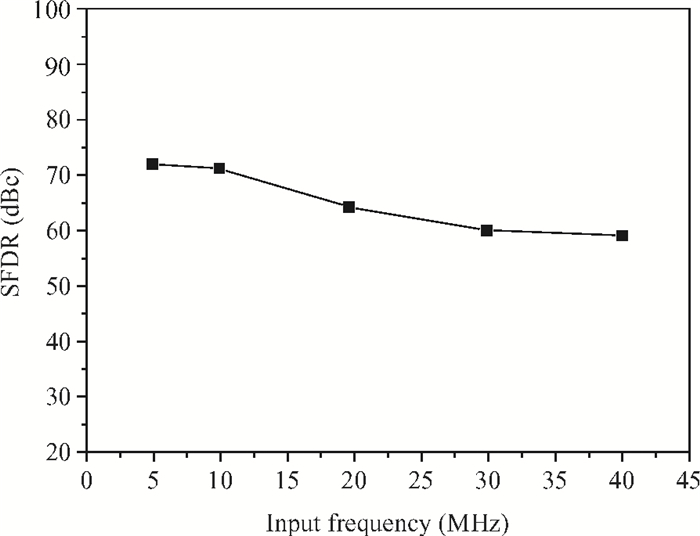

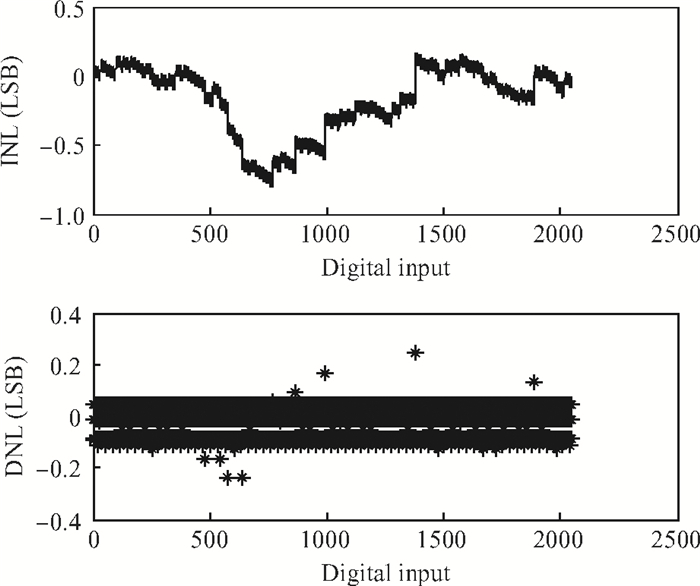

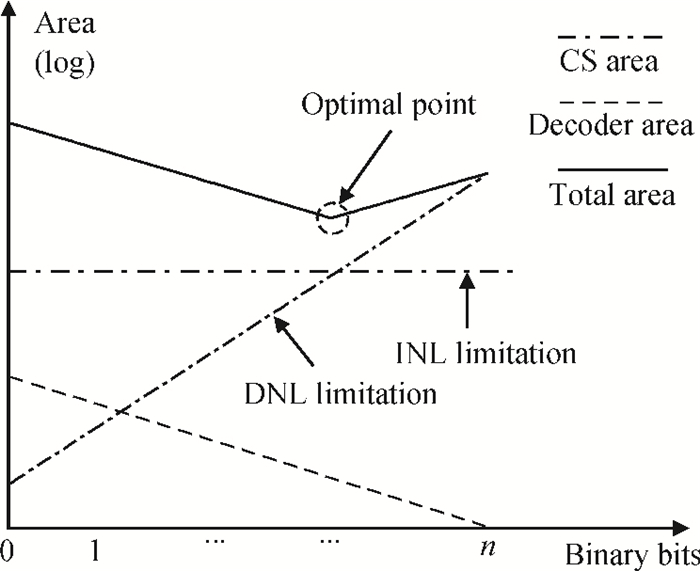

This paper presents an 11-bit 160 MS/s 2-channel current-steering digital-to-analog converter (DAC) IP. The circuit and layout are carefully designed to optimize its performance and area. A 6-2-3 segmented structure is used for the trade-off among linearity, area and layout complexity. The sizes of current source transistors are calculated out according to the process matching parameter. The unary current cells are placed in a one-dimension distribution to simplify the layout routing, spare area and wiring layer. Their sequences are also carefully designed to reduce integral nonlinearity. The test result presents an SFDR of 72 dBc at 4.88 MHz input signal with DNL ≤ 0.25 LSB, INL ≤ 0.8 LSB. The full-scale output current is 5 mA with a 2.5 V analog power supply. The core of each channel occupies 0.08 mm2 in a 1P-8M 55 nm CMOS process.-

Keywords:

- current-steering DAC,

- IP,

- matching,

- area optimization,

- mapping

-

References

[1] Mercer D A. Low-power approaches to high-speed current-steering digital-to-analog converters in 0.18-μm CMOS. IEEE J Solid-State Circuits, 2007, 42(8):1688 doi: 10.1109/JSSC.2007.900279[2] Li X, Wei Q, Yang H. Code-independent output impedance:a new approach to increasing the linearity of current-steering DACs. 18th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2011:216 http://www.cse.psu.edu/~xzl3/resources/ICECS2011_DAC.pdf[3] Sarkar S, Banerjee S. An 8-bit 1. 8 V 500 MSPS CMOS segmented current steering DAC. IEEE Computer Society Annual Symposium on VLSI, 2009: 268[4] Deveugele J, Steyaert M S J. A 10-bit 250-MS/s binary-weighted current-steering DAC. IEEE J Solid-State Circuits, 2006, 41(2):320 doi: 10.1109/JSSC.2005.862342[5] Li R, Zhao Q, Yi T, et al. A 14-bit 2-GS/s DAC with SFDR > 70 dB up to 1-GHz in 65-nm CMOS. IEEE 9th International Conference on ASIC (ASICON), 2011:500 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=6157231[6] Chen T, Gielen G. The analysis and improvement of a current-steering DAC's dynamic SFDR-Ⅱ:the output-dependent delay differences. IEEE Trans Circuits Syst Ⅰ:Regular Papers, 2007, 54(2):268 doi: 10.1109/TCSI.2006.887598[7] Van den Bosch A, Steyaert M, Sansen W. SFDR-bandwidth limitations for high speed high resolution current steering CMOS D/A converters. The 6th IEEE International Conference on Electronics, Circuits and Systems, 1999, 3:1193 http://ieeexplore.ieee.org/stamp/stamp.jsp?arnumber=814383[8] Liang Shangquan, Gao Minglun, Yin Yongsheng, et al. A 14-bit 320 MSPS segmented current-steering D/A converter for high-speed applications. 4th IEEE International Symposium on Electronic Design, Test and Applications, 2008:111 http://ieeexplore.ieee.org/document/4459521/[9] Wang Shaopeng. Design of current-steering digital-to-analog converters and corresponding calibration method. Tsinghua University, Beijing, 2013 -

Proportional views

DownLoad:

DownLoad: