| Citation: |

Kaiming Nie, Suying Yao, Jiangtao Xu, Zhaorui Jiang. A 10-bit ratio-independent cyclic ADC with offset canceling for a CMOS image sensor[J]. Journal of Semiconductors, 2014, 35(3): 035005. doi: 10.1088/1674-4926/35/3/035005

****

K M Nie, S Y Yao, J T Xu, Z R Jiang. A 10-bit ratio-independent cyclic ADC with offset canceling for a CMOS image sensor[J]. J. Semicond., 2014, 35(3): 035005. doi: 10.1088/1674-4926/35/3/035005.

|

A 10-bit ratio-independent cyclic ADC with offset canceling for a CMOS image sensor

DOI: 10.1088/1674-4926/35/3/035005

More Information

-

Abstract

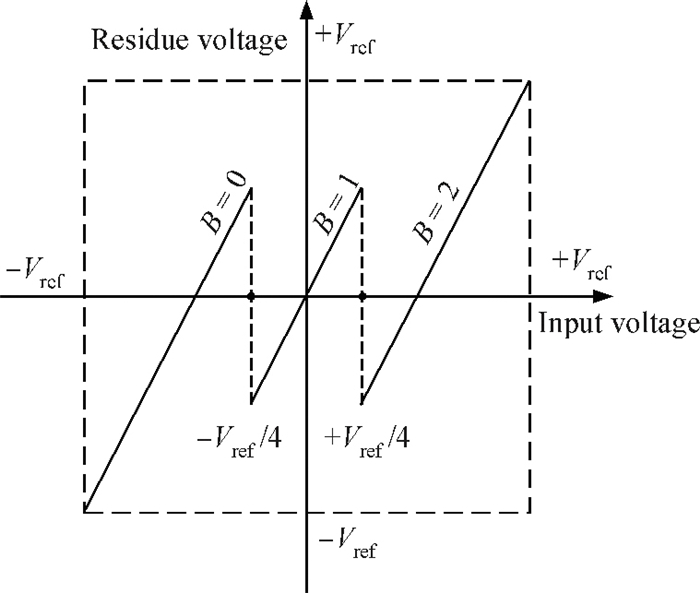

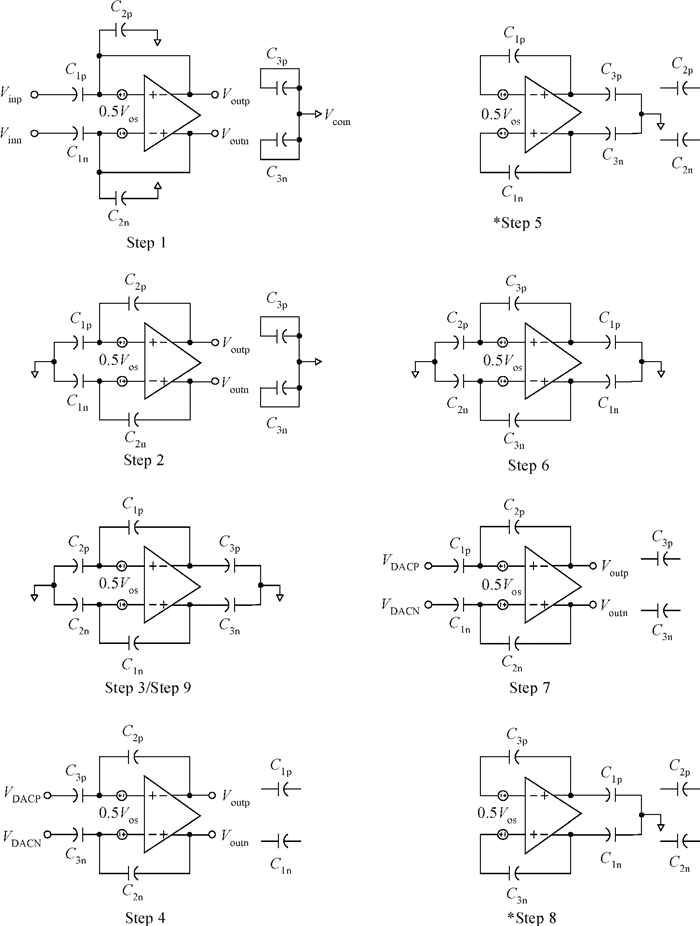

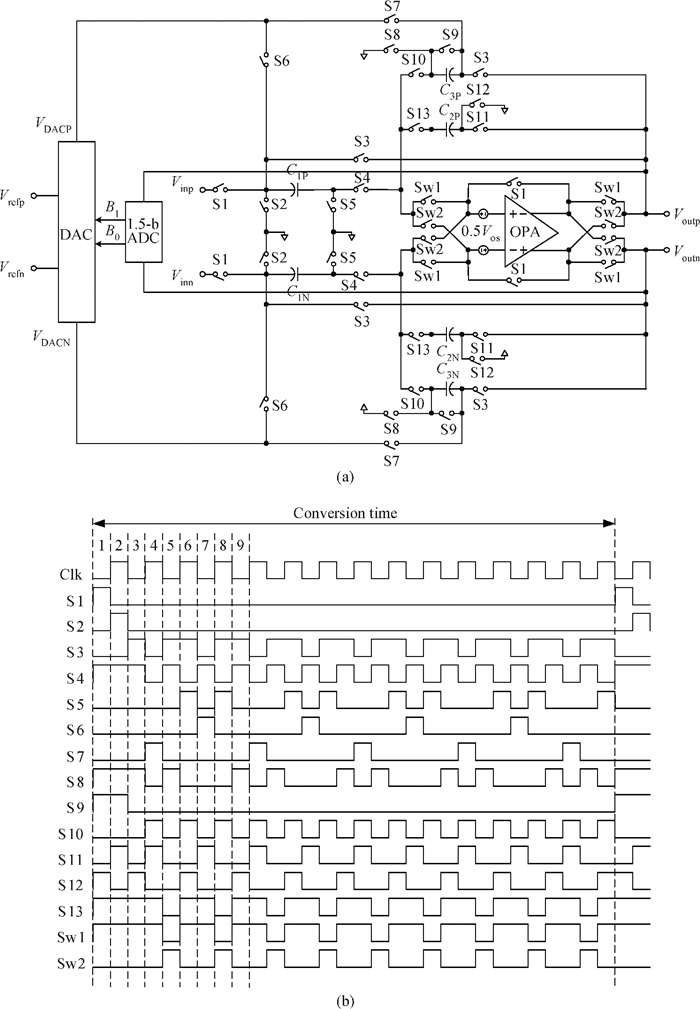

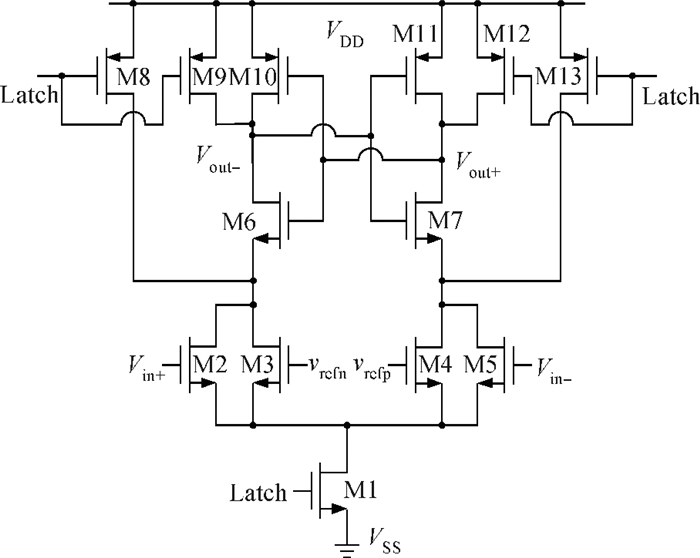

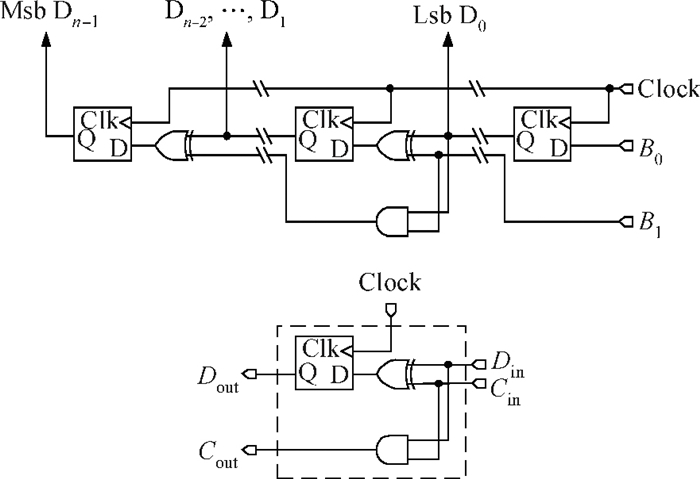

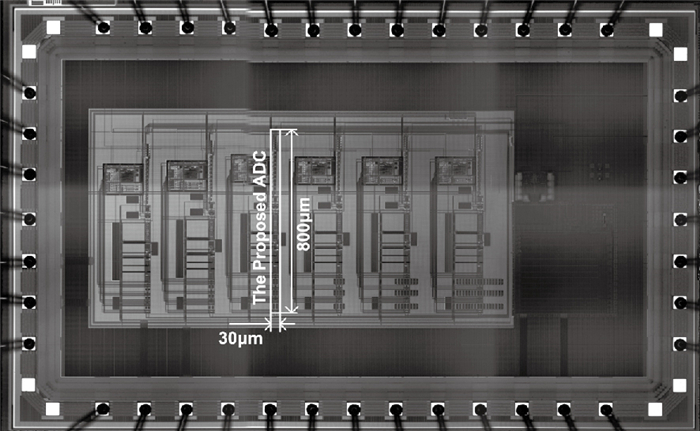

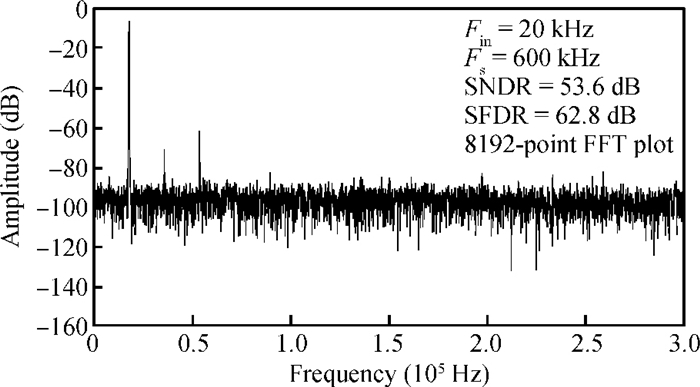

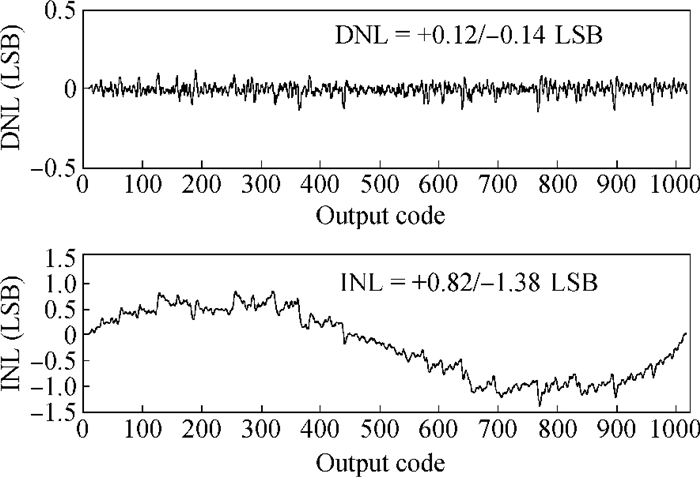

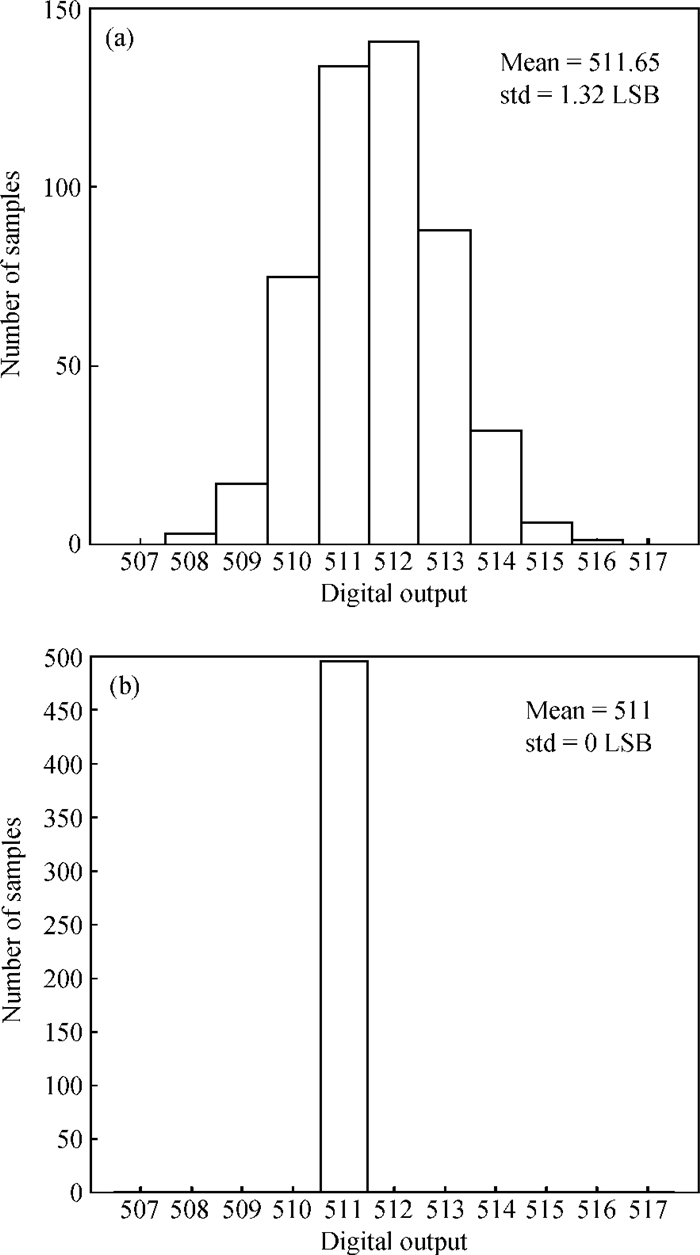

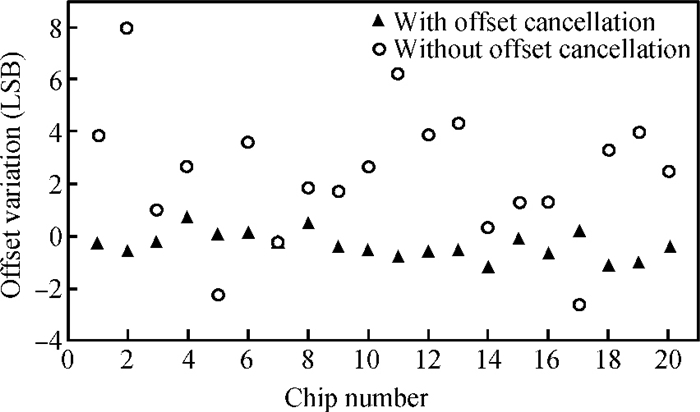

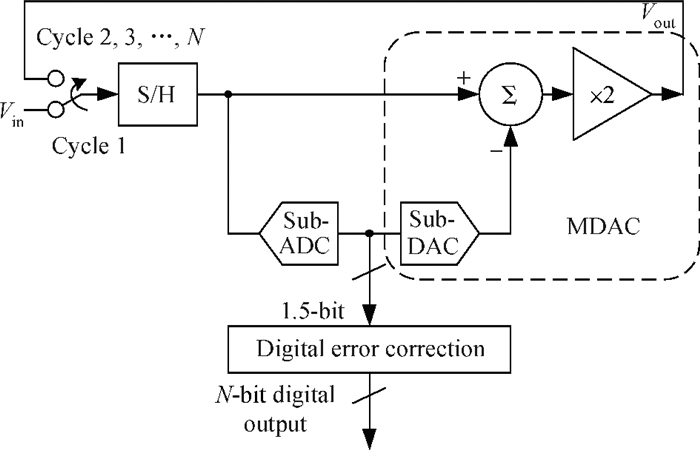

A 10-bit ratio-independent switch-capacitor (SC) cyclic analog-to-digital converter (ADC) with offset canceling for a CMOS image sensor is presented. The proposed ADC completes an N-bit conversion in 1.5N clock cycles with one operational amplifier. Combining ratio-independent and polarity swapping techniques, the conversion characteristic of the proposed cyclic ADC is inherently insensitive both to capacitor ratio and to amplifier offset voltage. Therefore, the circuit can be realized in a small die area and it is suitable to serve as the column-parallel ADC in CMOS image sensors. A prototype ADC is fabricated in 0.18-μm one-poly four-metal CMOS technology. The measured results indicate that the ADC has a signal-to-noise and distortion ratio (SNDR) of 53.6 dB and a DNL of +0.12/-0.14 LSB at a conversion rate of 600 kS/s. The standard deviation of the offset variation of the ADC is reduced from 2.5 LSB to 0.5 LSB. Its power dissipation is 250 μ W with a 1.8 V supply, and its area is 0.03×0.8 mm2. -

References

[1] Furuta M, Nishikawa Y, Inoue T, et al. A high-speed, high-sensitivity digital CMOS image sensor with a global shutter and 12-bit column-parallel cyclic A/D converters. IEEE J Solid-State Circuits, 2007, 42(4):766 doi: 10.1109/JSSC.2007.891655[2] Furuta M, Kawahito S, Inoue T, et al. A cyclic A/D converter with pixel noise and column-wise offset canceling for CMOS image sensors. IEEE Proceedings of the 31st European Solid-State Circuits Conference, 2005:411 http://ieeexplore.ieee.org/abstract/document/1541647[3] Park J H, Aoyama S, Watanabe T, et al. A high-speed low-noise CMOS image sensor with 13-b column-parallel single-ended cyclic ADCs. IEEE Trans Electron Devices, 2009, 56(11):2414 doi: 10.1109/TED.2009.2030635[4] Lim S, Cheon J, Chae Y, et al. A 240-frames/s 2.1-Mpixel CMOS image sensor with column-shared cyclic ADCs. IEEE J Solid-State Circuits, 2011, 46(9):2073 doi: 10.1109/JSSC.2011.2144010[5] Wang X, Hurst P J, Lewis S H. A 12-bit 20-Msample/s pipelined analog-to-digital converter with nested digital background calibration. IEEE J Solid-State Circuits, 2004, 39(11):1799 doi: 10.1109/JSSC.2004.835826[6] Chiu Y, Gray P R, Nikolic B. A 14-b 12-MS/s CMOS pipeline ADC with over 100-dB SFDR. IEEE J Solid-State Circuits, 2004, 39(12):2139 doi: 10.1109/JSSC.2004.836232[7] Li P W, Chin M J, Gray P R, et al. A ratio-independent algorithmic analog-to-digital conversion technique. IEEE J Solid-State Circuits, 1984, 19(6):828 doi: 10.1109/JSSC.1984.1052233[8] Hwang K. Computer arithmetic-principles, architecture and design. New York:Wiley Press, 1979[9] Bakker A, Thiele K, Huijsing J H. A CMOS nested-chopper instrumentation amplifier with 100-nV offset. IEEE J Solid-State Circuits, 2000, 35(12):1877 doi: 10.1109/4.890300[10] Lee B G, Yan S. A new ratio-independent A/D conversion technique for high-resolution pipeline A/D converters. IEEE International Symposium on Circuits and Systems, 2005:1960 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=1464998[11] Min B M, Kim P, Bowman Ⅲ F W, et al. A 69-mW 10-bit 80-MSample/s pipelined CMOS ADC. IEEE J Solid-State Circuits, 2003, 38(12):2031 doi: 10.1109/JSSC.2003.819166[12] Schreier R, Silva J, Steensgaard J, et al. Design-oriented estimation of thermal noise in switched-capacitor circuits. IEEE Trans Circuits Syst Ⅰ:Regular Papers, 2005, 52(11):2358 doi: 10.1109/TCSI.2005.853909[13] Razavi B. Design of analog CMOS integrated circuits. 1st ed. New York:McGraw-Hill Press, 2000[14] Jarvinen J A M, Saukoski M, Halonen K A I. A 12-bit ratio-independent algorithmic A/D converter for a capacitive sensor interface. IEEE Trans Circuits Syst Ⅰ:Regular Papers, 2008, 55(3):730 doi: 10.1109/TCSI.2008.919749[15] Lin J F, Chang S J, Chiu C F, et al. Low-power and wide-bandwidth cyclic ADC with capacitor and opamp reuse techniques for CMOS image sensor application. IEEE Sensors Journal, 2009, 9(12):2044 doi: 10.1109/JSEN.2009.2033198[16] Goodenough F. Analog technology of all varieties dominate ISSCC. Electron Design, 1996, 44(4):96 http://connection.ebscohost.com/c/articles/9603081836/analog-technology-all-varieties-dominate-isscc[17] Sauerbrey J, Tille T, Schmitt-Landsiedel D, et al. A 0.7-V MOSFET-only switched-opamp Σ Δ modulator in standard digital CMOS technology. IEEE J Solid-State Circuits, 2002, 37(12):1662 doi: 10.1109/JSSC.2002.804330[18] Chen H, Wu D, Shen Y, et al. A 13-bit, low-power, compact ADC suitable for sensor applications. IEEE International Symposium on Circuits and Systems, 2010:2414 http://ieeexplore.ieee.org/abstract/document/5537171[19] Froehlich T, Sharma V, Bingesser M. A 14 bit, 280 kS/s cyclic ADC with 100 dB SFDR. Proceedings of the Conference on Design, Automation and Test in Europe, 2010:706 https://www.date-conference.com/proceedings-archive/PAPERS/2010/DATE10/PDFFILES/06.4_3.PDF[20] Han Ye, Li Quanliang, Shi Cong, et al. A 10-bit column-parallel cyclic ADC for high-speed CMOS image sensors. Journal of Semiconductors, 2013, 34(8):085016 doi: 10.1088/1674-4926/34/8/085016[21] Esperanca B, Goes J, Tavares R, et al. Power-and-area efficient 14-bit 1.5 MSample/s two-stage algorithmic ADC based on a mismatch-insensitive MDAC. IEEE International Symposium on Circuits and Systems, 2008:220 http://ieeexplore.ieee.org/xpl/abstractAuthors.jsp?reload=true&arnumber=4541394 -

Proportional views

DownLoad:

DownLoad: