| Citation: |

P. A. Gowri Sankar, K. Udhayakumar. MOSFET-like CNFET based logic gate library for low-power application: a comparative study[J]. Journal of Semiconductors, 2014, 35(7): 075001. doi: 10.1088/1674-4926/35/7/075001

****

P. A. G. Sankar, K. Udhayakumar. MOSFET-like CNFET based logic gate library for low-power application: a comparative study[J]. J. Semicond., 2014, 35(7): 075001. doi: 10.1088/1674-4926/35/7/075001.

|

MOSFET-like CNFET based logic gate library for low-power application: a comparative study

DOI: 10.1088/1674-4926/35/7/075001

More Information

-

Abstract

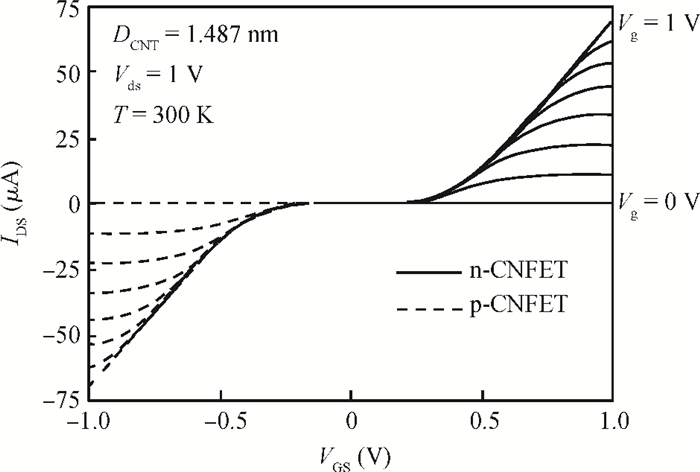

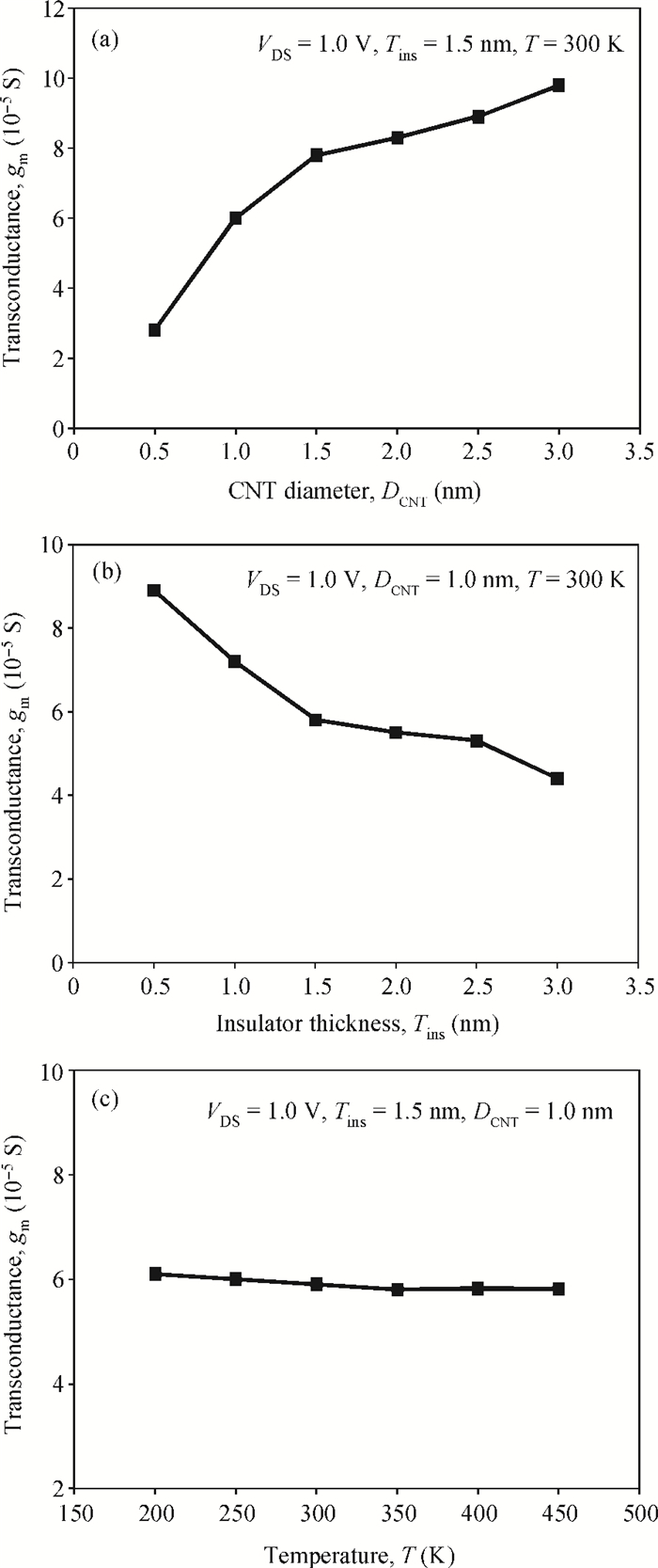

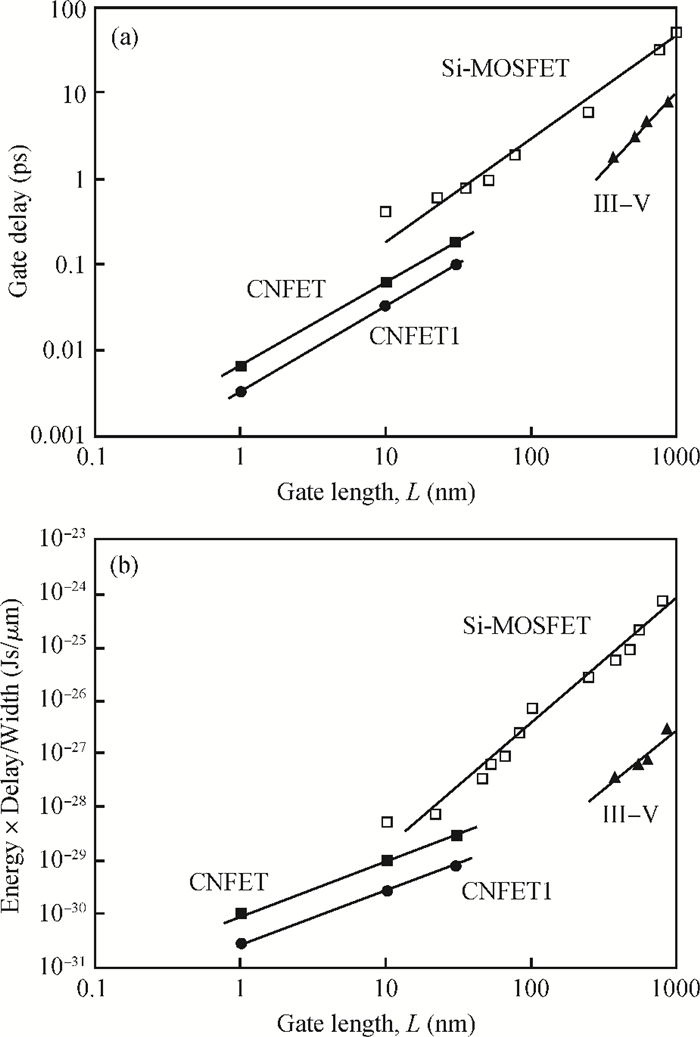

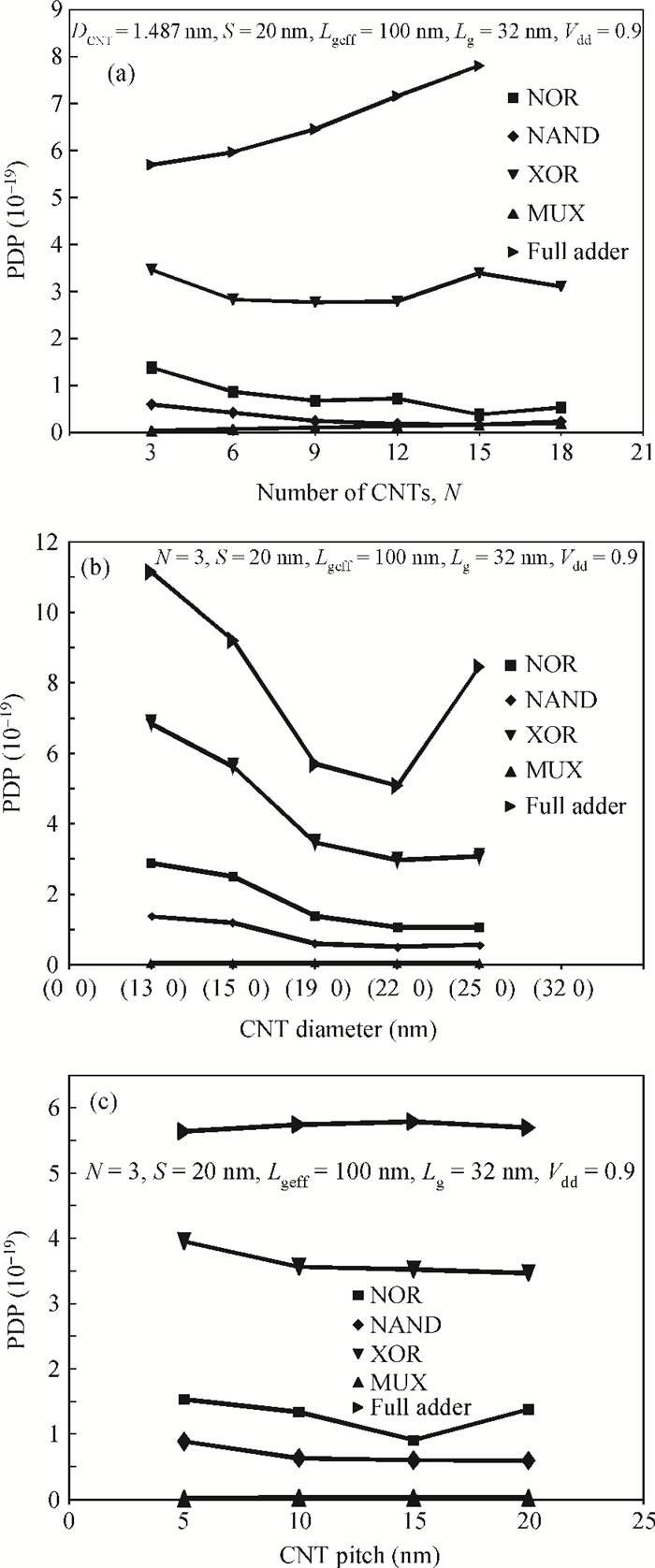

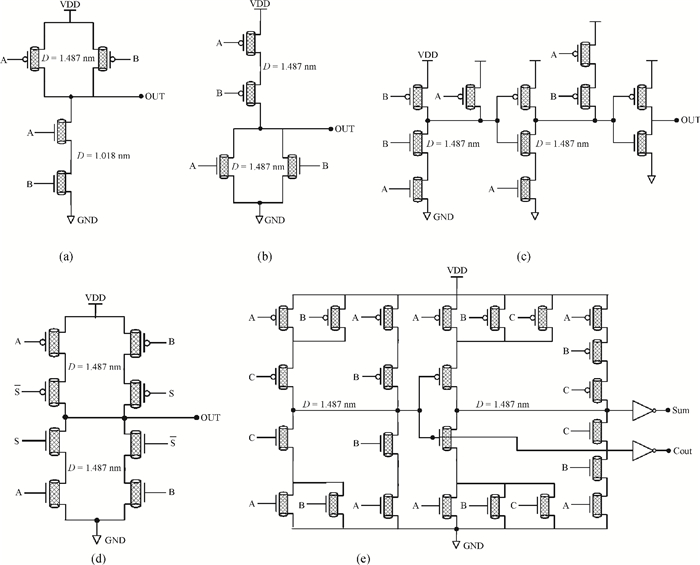

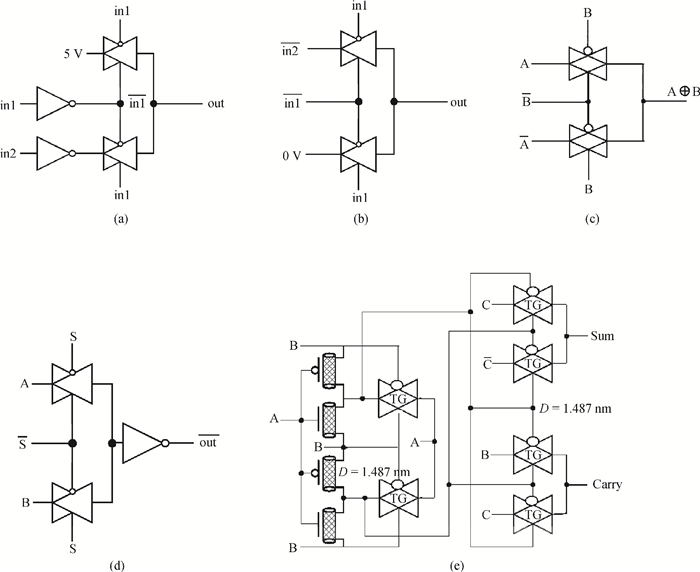

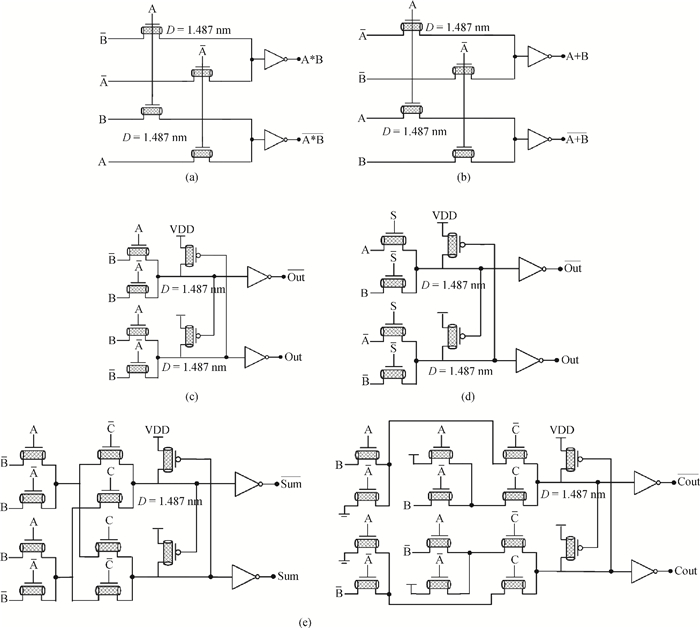

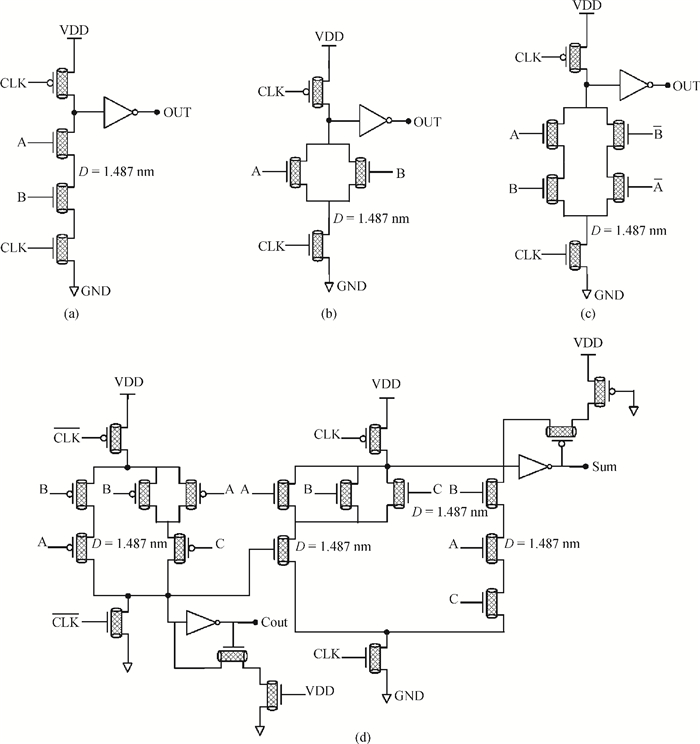

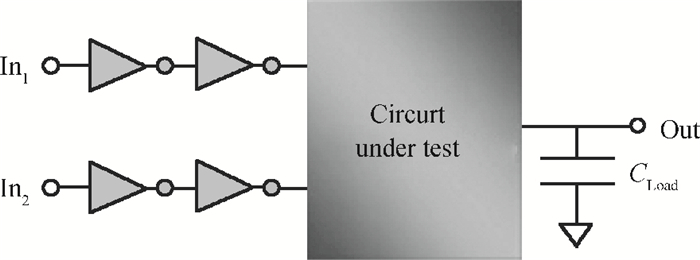

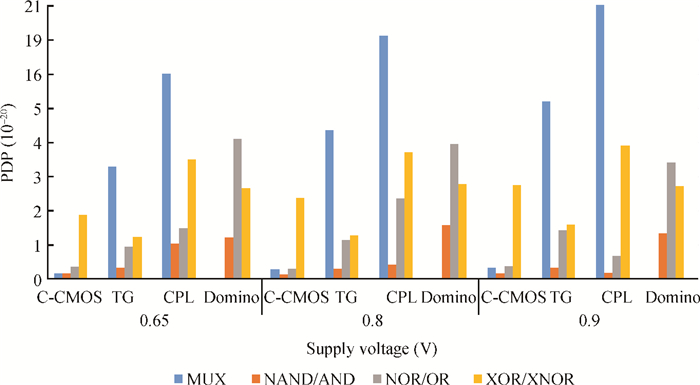

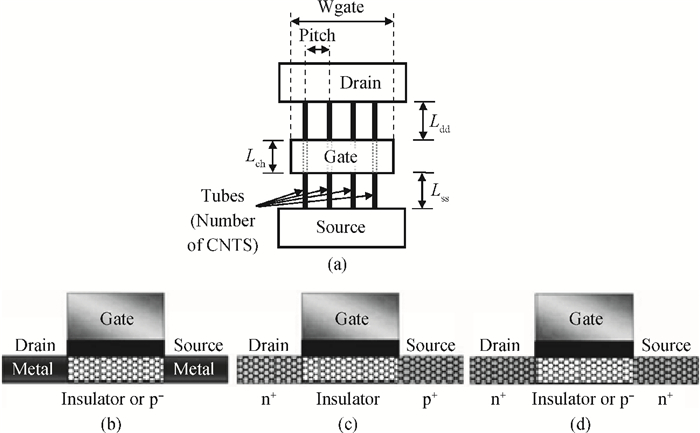

The next generation of logic gate devices are expected to depend upon radically new technologies mainly due to the increasing difficulties and limitations of existing CMOS technology. MOSFET like CNFETs should ideally be the best devices to work with for high-performance VLSI. This paper presents results of a comprehensive comparative study of MOSFET-like carbon nanotube field effect transistors (CNFETs) technology based logic gate library for high-speed, low-power operation than conventional bulk CMOS libraries. It focuses on comparing four promising logic families namely:complementary-CMOS (C-CMOS), transmission gate (TG), complementary pass logic (CPL) and Domino logic (DL) styles are presented. Based on these logic styles, the proposed library of static and dynamic NAND-NOR logic gates, XOR, multiplexer and full adder functions are implemented efficiently and carefully analyzed with a test bench to measure propagation delay and power dissipation as a function of supply voltage. This analysis provides the right choice of logic style for low-power, high-speed applications. Proposed logic gates libraries are simulated using Synopsys HSPICE based on the standard 32 nm CNFET model. The simulation results demonstrate that, it is best to use C-CMOS logic style gates that are implemented in CNFET technology which are superior in performance compared to other logic styles, because of their low average power-delay-product (PDP). The analysis also demonstrates how the optimum supply voltage varies with logic styles in ultra-low power systems. The robustness of the proposed logic gate library is also compared with conventional and state-art of CMOS logic gate libraries. -

References

[1] Pedram R. Low power design methodologies. Kluwer Academic Publishers, 1996: 367 doi: 10.1007%2F978-1-4615-2307-9[2] Chandrakasan R A, Nikolic B. Digital integrated circuits: a design perspective. Pearson Education, 2003: 761 http://ci.nii.ac.jp/ncid/BA6730502X[3] Durrani Z A K. Single-electron devices and circuits in silicon. World Scientific, 2009: 285 doi: 10.1142/p650[4] Kim J J, Roy K. Double gate-MOSFET subthreshold circuit for ultralow power applications. IEEE Trans Electron Devices, 2004, 51(9): 1468 doi: 10.1109/TED.2004.833965[5] McEuen P L, Fuhrer M S, Park H. Single-walled carbon nanotube electronics. IEEE Trans Nanotechnol, 2002, 1: 78 doi: 10.1109/TNANO.2002.1005429[6] Dragoman M, Dragoman D. Nano electronics-principles and devices. Artech House, London, 2010, 2: 2010 http://ci.nii.ac.jp/ncid/BB01349316[7] Chau R, Datta S, Doczy M, et al. Benchmarking nanotechnology for high-performance and low-power logic transistor applications. IEEE Trans Nanotechnol, 2005, 4(2): 153 doi: 10.1109/TNANO.2004.842073[8] Ben-Jamaa M H, Mohanram K, Micheli G D. An efficient gate library for ambipolar CNTFET logic. IEEE Trans Computer-Aided Design of Integrated Circuits and Systems, 2011, 30(2): 242 doi: 10.1109/TCAD.2010.2085250[9] Ben Jamaa M H. Novel library of logic gates with ambipolar CNTFETs: opportunities for multi-level logic synthesis. IEEE Design, Automation & Test in Europe Conference & Exhibition, Lausanne, 2009: 622 http://ieeexplore.ieee.org/document/5090742/[10] O'Connor I, Junchen L, Gaffiot F, et al. CNTFET modeling and reconfigurable logic-circuit design. IEEE Trans Circuits Syst I: Regular Papers, 2007, 54(11): 2365 doi: 10.1109/TCSI.2007.907835[11] Connell M J O. Carbon nanotubes: properties and applications. Taylor and Francis Group, Boca Raton, 2006: 360 http://ci.nii.ac.jp/ncid/BA77079357[12] Javey A, Guo J, Wang Q, et al. Ballistic carbon nanotube field-effect transistors. Nature, 2003, 4: 654 http://www.nature.com/nature/journal/v424/n6949/abs/nature01797.html?foxtrotcallback=true[13] Martel R, Derycke V, Lavoir C, et al. Ambipolar electrical transport in semiconducting single-wall carbon nanotubes. Phys Rev Lett, 2001, 87(4): 256805 http://www.adsabs.harvard.edu/abs/2001PhRvL..87y6805M[14] Javey A, Guo J, Farmer D, et al. Self-aligned ballistic molecular transistors and electrically parallel nanotube arrays. Nano Lett, 2004, 4: 1319 doi: 10.1021/nl049222b[15] Keshavarzi A, Raychowdhury A, Kurtin J. Carbon nanotube field-effect transistors for high-performance digital circuits-transient analysis, parasitics, and scalability. IEEE Trans Electron Devices, 2006, 53(11): 2718 doi: 10.1109/TED.2006.883813[16] Raychowdhury A, Keshavarzi A, Kurtin J, et al. CNFETs for high-performance digital circuits-DC analysis and modeling toward optimum transistor structure. IEEE Trans Electron Devices, 2006, 53(11): 2711 doi: 10.1109/TED.2006.883816[17] Raychowdhury A, Roy K. Carbon nanotube electronics: design of high-performance and low-power digital circuits. IEEE Trans Circuits Syst, 2007, 54: 2391 doi: 10.1109/TCSI.2007.907799[18] Javey A, Farmer D, Guo J, et al. High-performance n-type carbon nanotube field-effect transistors with chemically doped contacts. Nano Lett, 2005, 5: 345 doi: 10.1021/nl047931j[19] Duan Y, Juhala J L. Solution-based fabrication of p-channel and n-channel field-effect transistors using random and aligned carbon nanotube networks. Microelectron Eng, 2013, 103: 18 doi: 10.1016/j.mee.2012.09.016[20] Bok K Y, Lombardi F. Novel design methodology to optimize the speed and power of the CNTFET circuits. IEEE International Midwest Symposium On Circuits and Systems, Mexico, 2009: 1130[21] Javey A, Guo J, Farmer D B, et al. Self-Aligned ballistic molecular transistors and electrically parallel nanotube arrays. Nano Lett, 2004, 4: 1319 doi: 10.1021/nl049222b[22] Deng J, Wong H S P. A circuit-compatible spice model for enhancement mode carbon nanotube field effect transistors. International Conference on Simulation of Semiconductor Processes and Devices, 2006: 166 http://ieeexplore.ieee.org/document/4061607/keywords[23] Appenzeller J. Carbon nanotubes for high performance electronics. Proc IEEE, 2008, 96(2): 206[24] Deng J, Patil N, Ryu K, et al. Carbon nanotube transistor circuits: circuit-level performance benchmarking and design options for living with imperfections. International Solid State Circuits Conference (ISSCC), San Francisco, 2007: 70[25] Balijepalli A, Sinha S, Cao Y. Compact modeling of carbon nanotube transistor for early stage process-design exploration. International Symposium on Low Power Electronics and Design, Portland, 2007: 2 http://ieeexplore.ieee.org/document/5514278/?reload=true&arnumber=5514278&contentType=Conference%20Publications&sortType%3Dasc_p_Sequence%26filter%3DAND(p_IS_Number:5514251)[26] Deng J, Wong H S P. A compact SPICE model for carbon-nanotube field-effect transistors including non-idealities and its application-Part I: model of the intrinsic channel region. IEEE Trans Electron Devices, 2007, 54(12): 3186 doi: 10.1109/TED.2007.909030[27] Deng J, Wong H S P. A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application. Part Ⅱ: full device model and circuit performance benchmarking. IEEE Trans Electron Devices, 2007, 54(12): 3195 doi: 10.1109/TED.2007.909043[28] Stanford University CNFET model Website. https://nano.stanford.edu/stanford-cnfet-model[29] Anis M, Allam M, Elmasry M. Impact of technology scaling on CMOS logic styles. IEEE Trans Circuits Syst Ⅱ: Analog and Digital Signal Process, 2002, 49(8): 577 doi: 10.1109/TCSII.2002.805631[30] Vaddi R, Dasgupta S, Agarwal R P. Device and circuit co-design robustness studies in the subthreshold logic for ultralow-power applications for 32 nm CMOS. IEEE Trans Electron Devices, 2010, 57(3): 654 doi: 10.1109/TED.2009.2039529 -

Proportional views

DownLoad:

DownLoad: