| Citation: |

Jincan Zhang, Yuming Zhang, Hongliang Lü, Yimen Zhang, Guangxing Xiao, Guiping Ye. A 6-bit 3-Gsps ADC implemented in 1 μm GaAs HBT technology[J]. Journal of Semiconductors, 2014, 35(8): 085005. doi: 10.1088/1674-4926/35/8/085005

****

J C Zhang, Y M Zhang, H Lü, Y M Zhang, G X Xiao, G P Ye. A 6-bit 3-Gsps ADC implemented in 1 μm GaAs HBT technology[J]. J. Semicond., 2014, 35(8): 085005. doi: 10.1088/1674-4926/35/8/085005.

|

A 6-bit 3-Gsps ADC implemented in 1 μm GaAs HBT technology

DOI: 10.1088/1674-4926/35/8/085005

More Information

-

Abstract

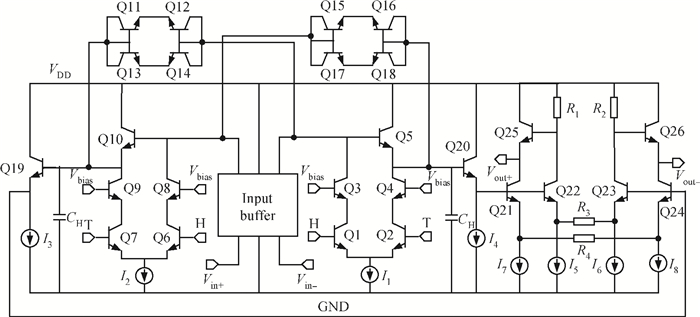

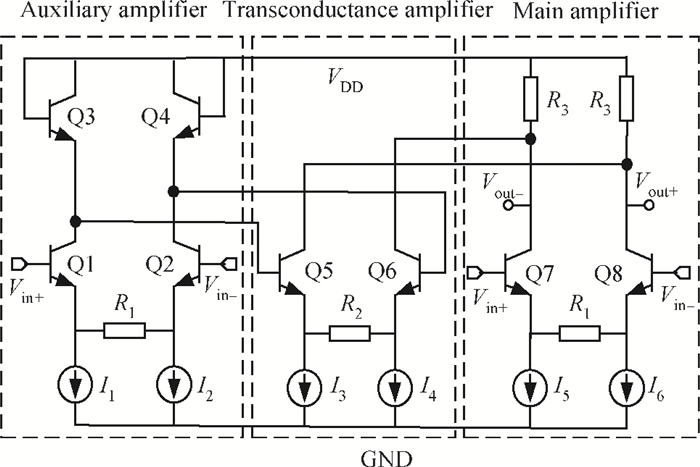

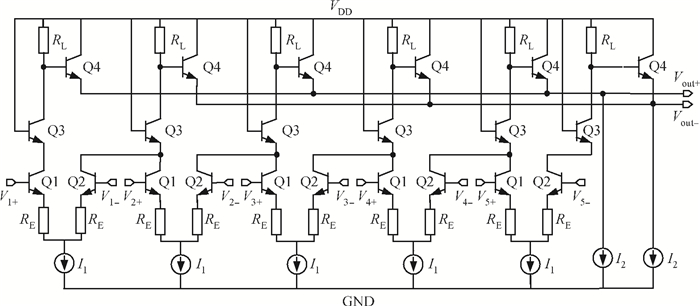

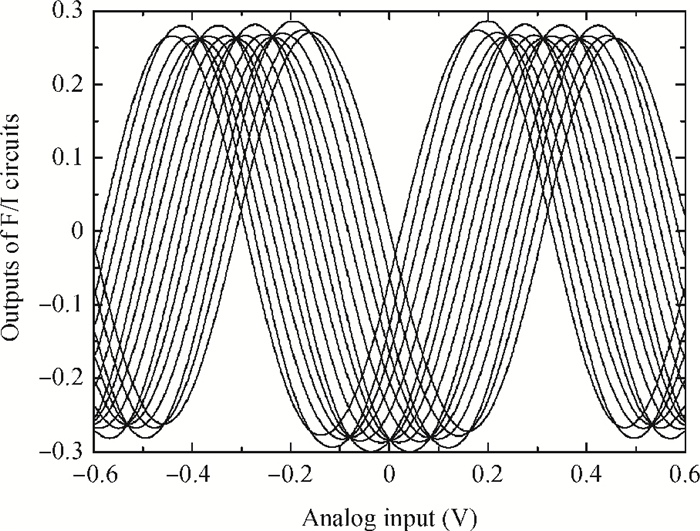

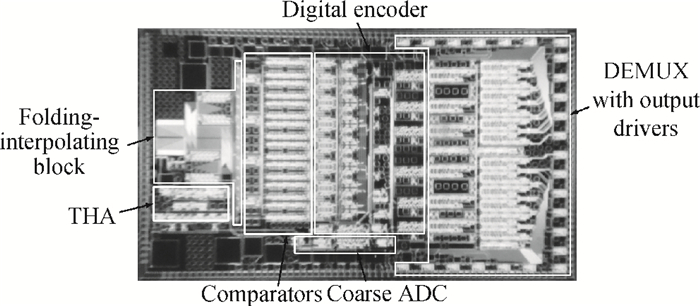

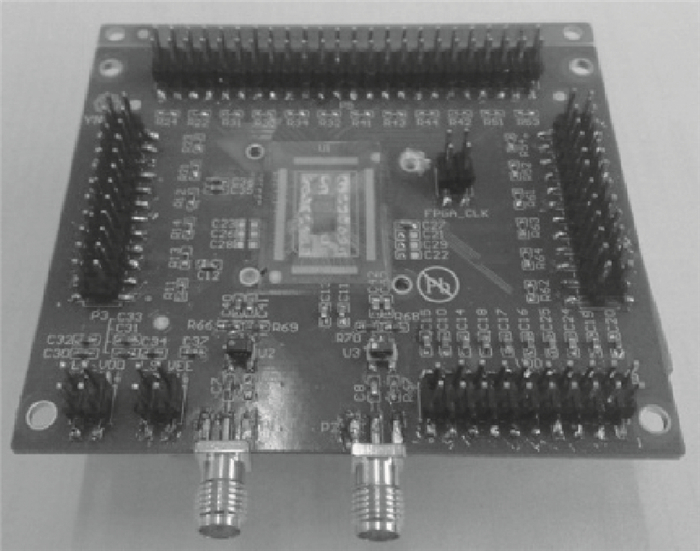

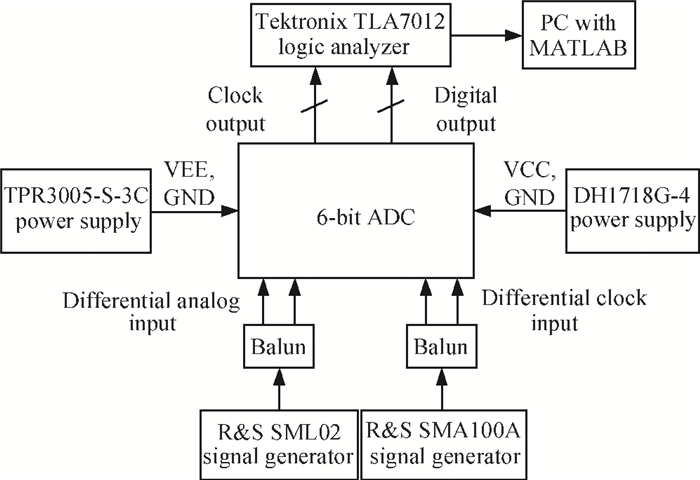

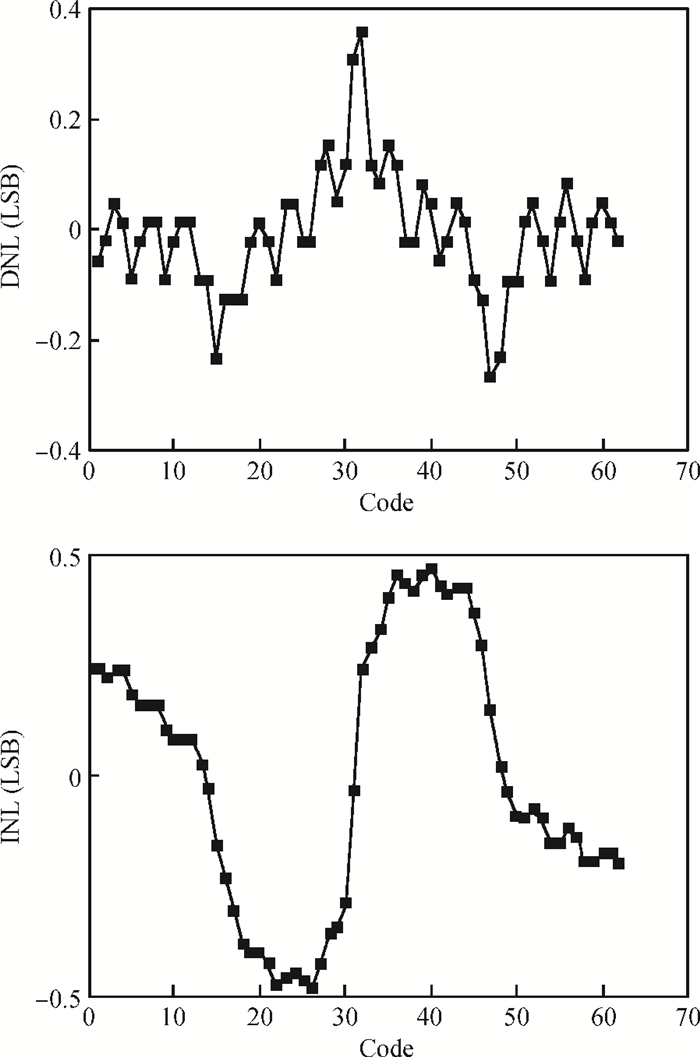

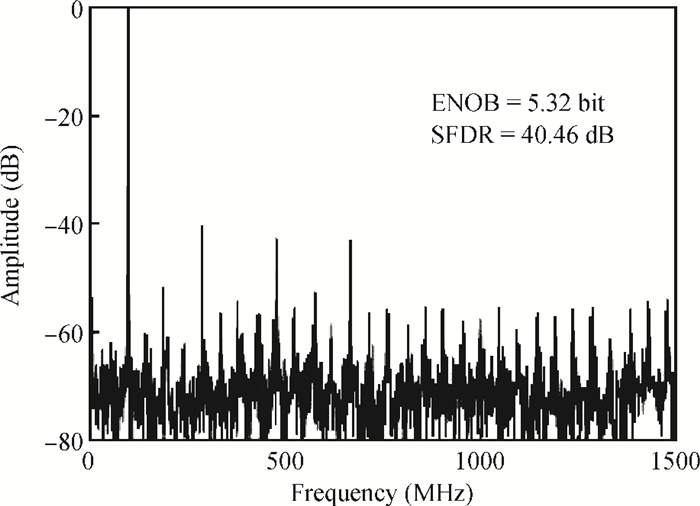

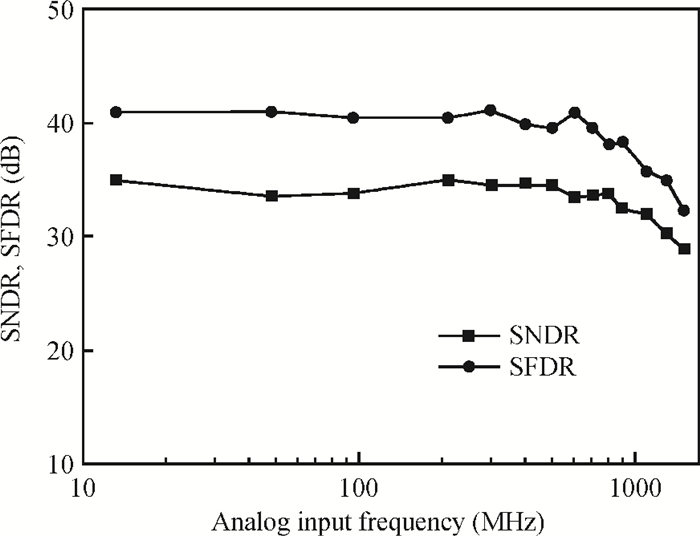

The design and test results of a 6-bit 3-Gsps analog-to-digital converter (ADC) using 1 μm GaAs heterojunction bipolar transistor (HBT) technology are presented. The monolithic folding-interpolating ADC makes use of a track-and-hold amplifier (THA) with a highly linear input buffer to maintain a highly effective number of bits (ENOB). The ADC occupies an area of 4.32×3.66 mm2 and achieves 5.53 ENOB with an effective resolution bandwidth of 1.1 GHz at a sampling rate of 3 Gsps. The maximum DNL and INL are 0.36 LSB and 0.48 LSB, respectively.-

Keywords:

- analog-to-digital converter,

- GaAs HBT,

- folding,

- interpolating

-

References

[1] Payne R, Sestok C, Bright W, et al. A 12 b 1 GS/s SiGe BiCMOS two-way time-interleaved pipeline ADC. IEEE International Solid-State Circuits Conference, 2011:182 doi: 10.1007/978-3-319-17680-2_4[2] Chu M, Jacob P, Kim J W, et al. A 40 Gs/s time interleaved ADC using SiGe BiCMOS technology. IEEE J Solid-State Circuits, 2010, 45(2):380 doi: 10.1109/JSSC.2009.2039375[3] Vessal F, Salama C A T. An 8-bit 2-Gsample/s folding-interpolating analog-to-digital converter in SiGe technology. IEEE J Solid-State Circuits, 2004, 39(1):238 doi: 10.1109/JSSC.2003.820867[4] Lee J, Weiner J, Chen Y K. A 20-GS/s 5-b SiGe ADC for 40-Gb/s coherent optical links. IEEE Trans Circuits Syst I:Regular Papers, 2010, 57(10):2665 doi: 10.1109/TCSI.2010.2048678[5] Zhao Yi, Wang Shenjie, Qin Yajie, et al. A sub-sampling 4-bit 1.056-GS/s flash ADC with a novel track and hold amplifier for an IR-UWB receiver. Journal of Semiconductors, 2011, 32(7):075001 doi: 10.1088/1674-4926/32/7/075001[6] Zhang Youtao, Li Xiaopeng, Zhang Min, et al. A 2-GS/s 6-bit self-calibrated flash ADC. Journal of Semiconductors, 2010, 31(9):095013 doi: 10.1088/1674-4926/31/9/095013[7] Jiang T, Liu W, Zhong F Y, et al. A single-channel, 1.25-GS/s, 6-bit, 6.08-mW asynchronous successive-approximation ADC with improved feedback delay in 40-nm CMOS. IEEE J Solid-State Circuits, 2012, 47(10):2444 doi: 10.1109/JSSC.2012.2204543[8] Varzaghani A, Kasapi A, Loizos D N, et al. A 10.3-GS/s, 6-Bit flash ADC for 10G ethernet applications. IEEE J Solid-State Circuits, 2013, 48(12):1 doi: 10.1109/JSSC.2013.2292111[9] Kim J I, Sung B R S, Kim W, et al. A 6-b 4.1-GS/s flash ADC with time-domain latch interpolation in 90-nm CMOS. IEEE J Solid-State Circuits, 2013, 48(6):1429 doi: 10.1109/JSSC.2013.2252516[10] Chan B, Oyama B, Monier C, et al. An ultra-wideband 7-Bit 5-Gsps ADC implemented in submicron InP HBT technology. IEEE J Solid-State Circuits, 2008, 43(10):2187 doi: 10.1109/JSSC.2008.2002932[11] Kraus S, Kallfass I, Makon R E, et al. A 10-GS/s multibit delta-sigma analog-to-digital converter in an InP HBT technology. IEEE International Conference on Microwaves, Communications, Antennas and Electronics Systems (COMCAS), 2011:1 http://ieeexplore.ieee.org/document/6105929/[12] Nosaka H, Nakamura M, Ida M, et al. A 24-Gsps 3-bit nyquist ADC using InP HBTs for electronic dispersion compensation. IEEE MTT-S Int Microwave Symp Dig, 2004:101 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=1335812[13] Guo Z, Amore M D, Gutierrez A. A 2-Bit 20 Gsps InP HBT A/D converter for optical communications. IEEE CSIC Dig, 2004:93 doi: 10.1109/CSICS.2004.1392500[14] Wu Danyu, Zhou Lei, Guo Jiannan, et al. A 4 GS/S 4 bit ADC with 3.8 analog bandwidth in GaAs HBT technology. Journal of Semiconductors, 2011, 32(6):065007 doi: 10.1088/1674-4926/32/6/065007[15] Yamanaka S, Sano K, Murata K. A 20-Gs/s track-and-hold amplifier in InP HBT technology. IEEE Trans Microw Theory Tech, 2010, 58(9):2334 doi: 10.1109/TMTT.2010.2057174[16] Karanicolas A N. A 2.7-V 300-MS/s track-and-hold amplifier. IEEE J Solid-State Circuits, 1997, 32(12):1961 doi: 10.1109/4.643654[17] Shahramian S, Voinigescu S P, Carusone A C. A 35-GS/s, 4-bit flash ADC with active data and clock distribution trees. IEEE J Solid-State Circuits, 2009, 44(6):1709 doi: 10.1109/JSSC.2009.2020657[18] Kobayashi H, Tobari T, Matsuura H, et al. System architecture and key components of a multi-giga-hertz A/D convert with HBT. IEEE Instrumentation and Measurement Technology Conference, 1996:1160 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=507554 -

Proportional views

DownLoad:

DownLoad: