| Citation: |

Jiaqi Dong, Keni Qiu, Weigong Zhang, Jing Wang, Zhenzhen Wang, Lihua Ding. Multi-bit upset aware hybrid error-correction for cache in embedded processors[J]. Journal of Semiconductors, 2015, 36(11): 114006. doi: 10.1088/1674-4926/36/11/114006

****

J Q Dong, K N Qiu, W G Zhang, J Wang, Z Z Wang, L H Ding. Multi-bit upset aware hybrid error-correction for cache in embedded processors[J]. J. Semicond., 2015, 36(11): 114006. doi: 10.1088/1674-4926/36/11/114006.

|

Multi-bit upset aware hybrid error-correction for cache in embedded processors

DOI: 10.1088/1674-4926/36/11/114006

More Information

-

Abstract

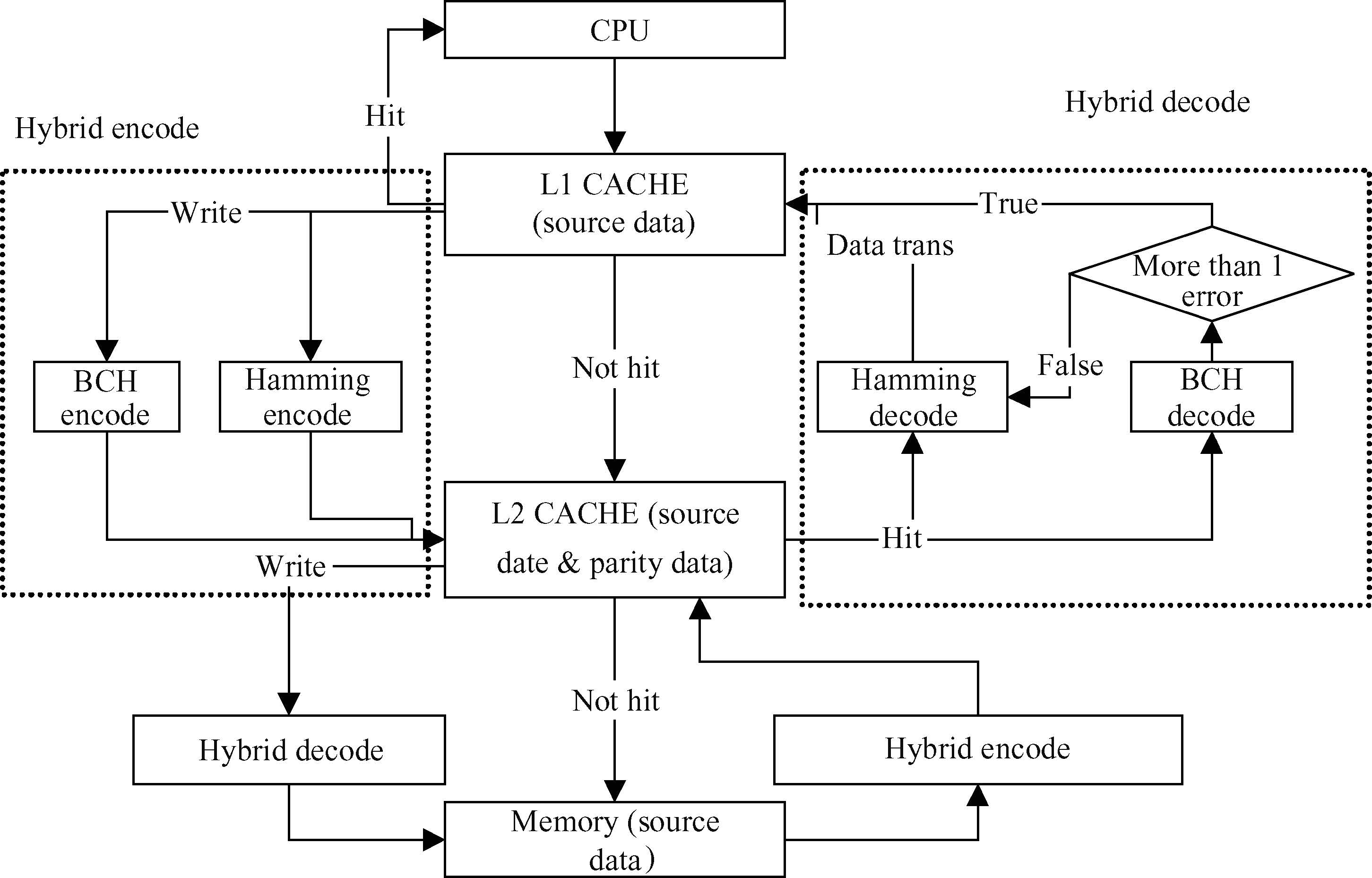

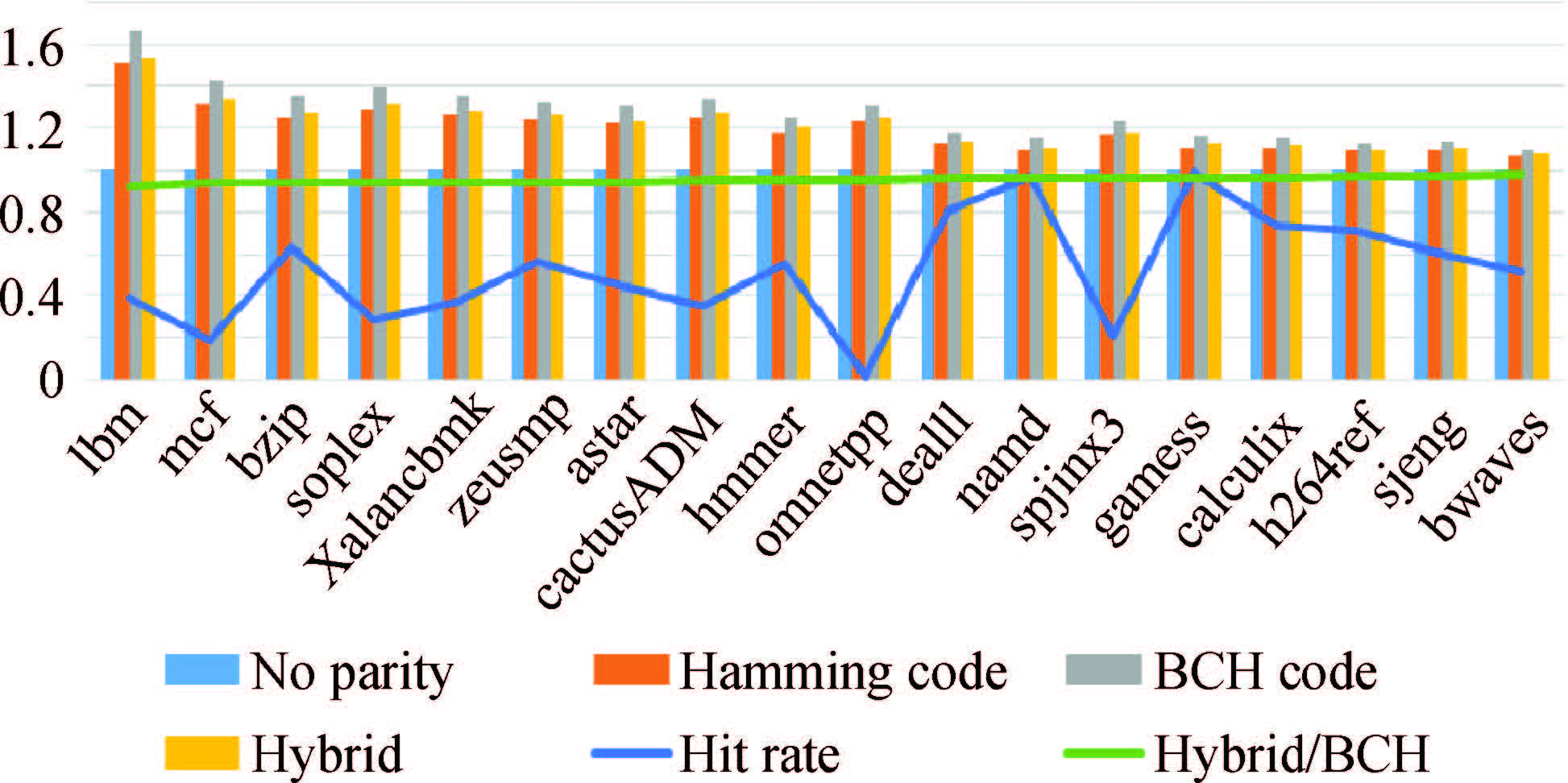

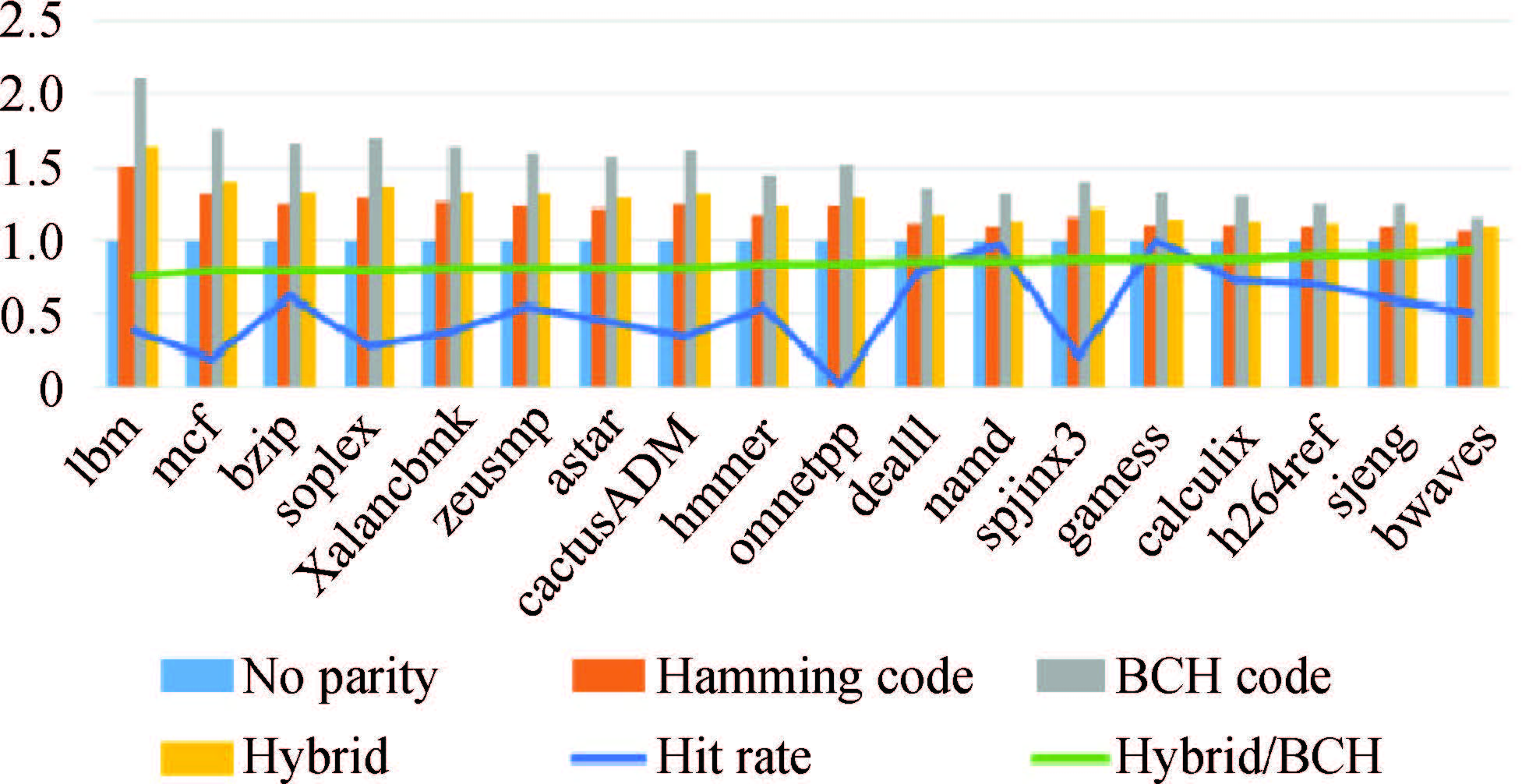

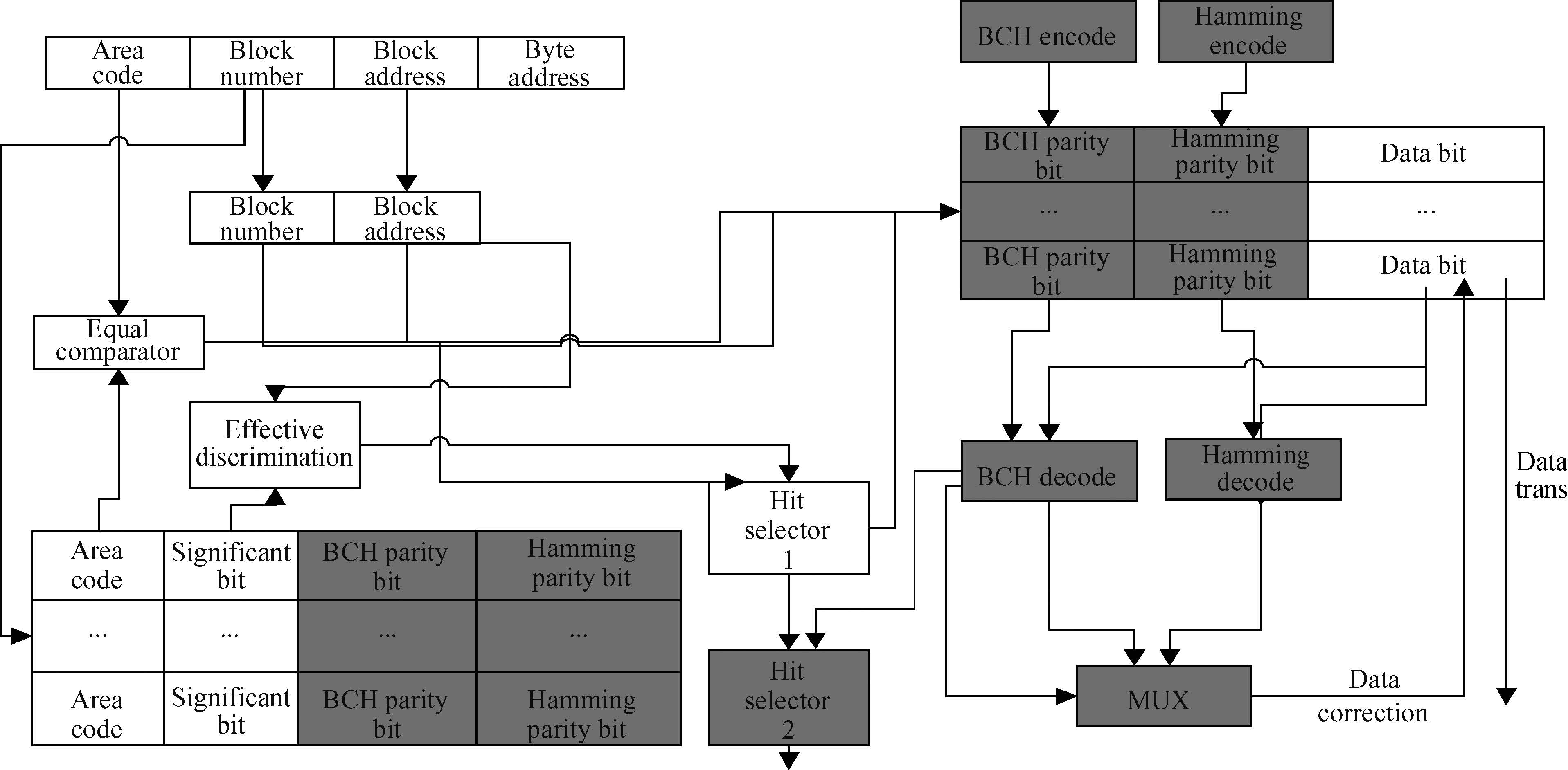

For the processor working in the radiation environment in space, it tends to suffer from the single event effect on circuits and system failures, due to cosmic rays and high energy particle radiation. Therefore, the reliability of the processor has become an increasingly serious issue. The BCH-based error correction code can correct multi-bit errors, but it introduces large latency overhead. This paper proposes a hybrid error correction approach that combines BCH and EDAC to correct both multi-bit and single-bit errors for caches with low cost. The proposed technique can correct up to four-bit error, and correct single-bit error in one cycle. Evaluation results show that, the proposed hybrid error-correction scheme can improve the performance of cache accesses up to 20% compared to the pure BCH scheme.-

Keywords:

- BCH,

- single event upset,

- cache,

- multi-bit error correction,

- embedded processor

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] -

Proportional views

DownLoad:

DownLoad: