| Citation: |

Xiaobao Yu, Siyang Han, Zongming Jin, Zhihua Wang, Baoyong Chi. A class-C VCO based Σ-Δ fraction-N frequency synthesizer with AFC for 802.11ah applications[J]. Journal of Semiconductors, 2015, 36(9): 095003. doi: 10.1088/1674-4926/36/9/095003

****

X B Yu, S Y Han, Z M Jin, Z H Wang, B Y Chi. A class-C VCO based Σ-Δ fraction-N frequency synthesizer with AFC for 802.11ah applications[J]. J. Semicond., 2015, 36(9): 095003. doi: 10.1088/1674-4926/36/9/095003.

|

A class-C VCO based Σ-Δ fraction-N frequency synthesizer with AFC for 802.11ah applications

DOI: 10.1088/1674-4926/36/9/095003

-

Abstract

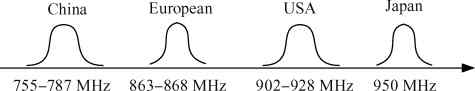

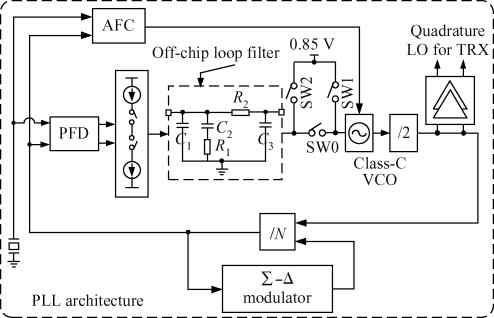

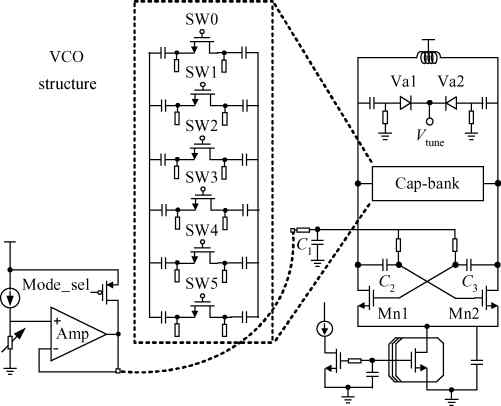

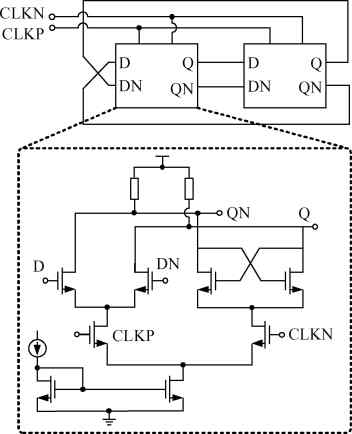

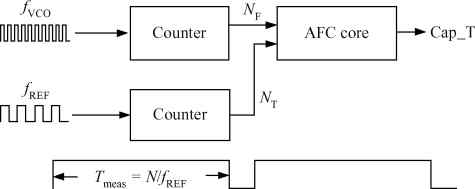

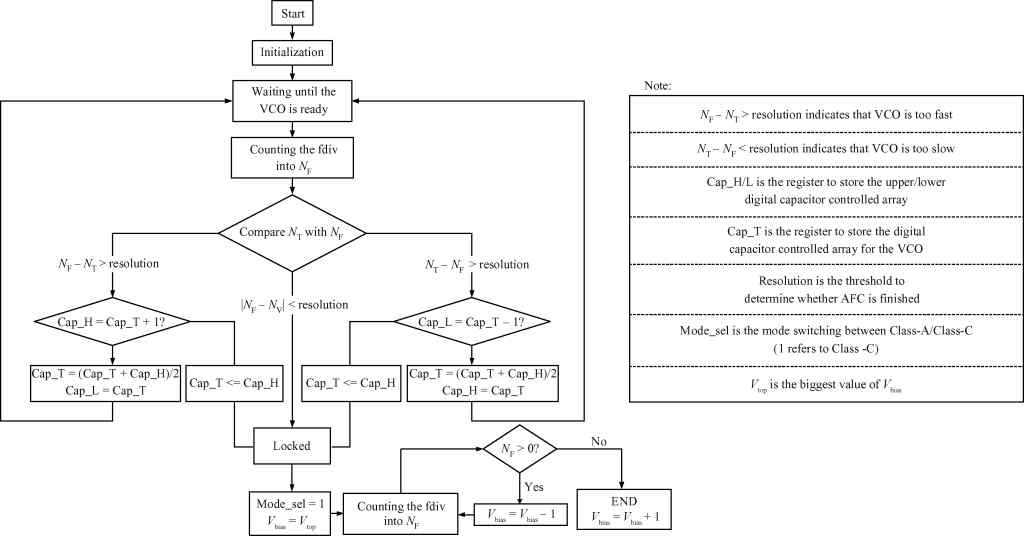

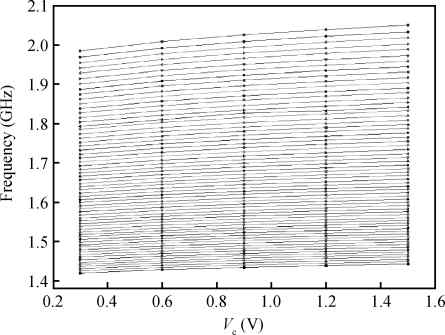

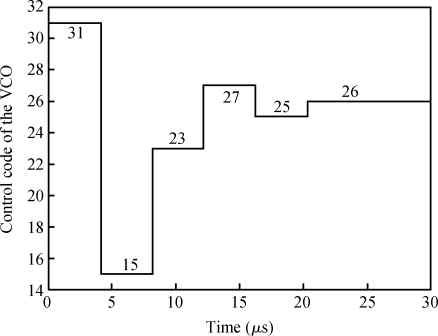

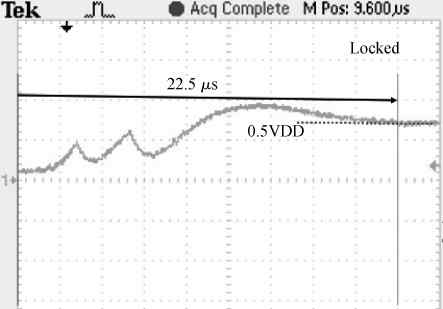

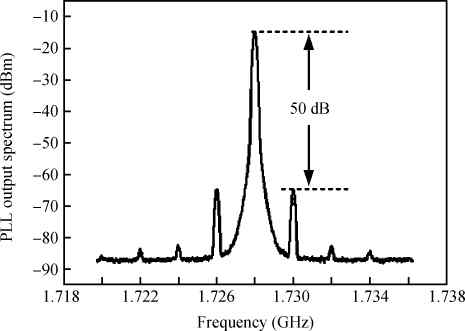

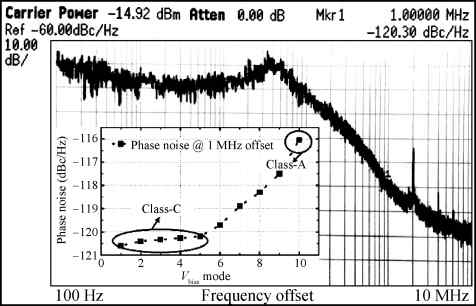

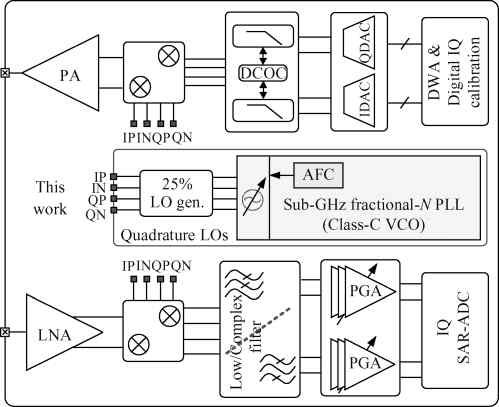

A 1.4-2 GHz phase-locked loop (PLL) Σ-Δ fraction-N frequency synthesizer with automatic frequency control (AFC) for 802.11ah applications is presented. A class-C voltage control oscillator (VCO) ranging from 1.4 to 2 GHz is integrated on-chip to save power for the sub-GHz band. A novel AFC algorithm is introduced to maintain the VCO oscillation at the start-up and automatically search for the appropriate control word of the switched-capacitor array to extend the PLL tuning range. A 20-bit third-order Σ-Δ modulator is utilized to reduce the fraction spurs while achieving a frequency resolution that is lower than 30 Hz. The measurement results show that the frequency synthesizer has achieved a phase noise of < -120 dBc/Hz at 1 MHz offset and consumes 11.1 mW from a 1.7 V supply. Moreover,compared with the traditional class-A counterparts,the phase noise in class-C mode has been improved by 5 dB under the same power consumption. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] -

Proportional views

DownLoad:

DownLoad: