| Citation: |

Yunchou Zhao, Hao Jia, Jianfeng Ding, Lei Zhang, Xin Fu, Lin Yang. Five-port silicon optical router based on Mach-Zehnder optical switches for photonic networks-on-chip[J]. Journal of Semiconductors, 2016, 37(11): 114008. doi: 10.1088/1674-4926/37/11/114008

****

Y C Zhao, H Jia, J F Ding, L Zhang, X Fu, L Yang. Five-port silicon optical router based on Mach-Zehnder optical switches for photonic networks-on-chip[J]. J. Semicond., 2016, 37(11): 114008. doi: 10.1088/1674-4926/37/11/114008.

|

Five-port silicon optical router based on Mach-Zehnder optical switches for photonic networks-on-chip

DOI: 10.1088/1674-4926/37/11/114008

More Information

-

Abstract

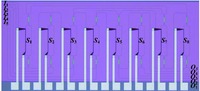

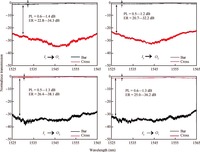

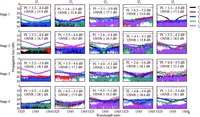

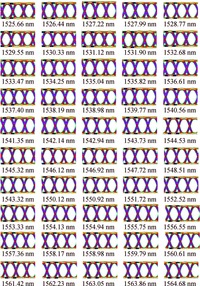

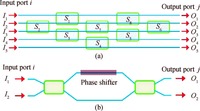

With the continuous development of integrated circuits, the performance of the processor has been improved steadily. To integrate more cores in one processor is an effective way to improve the performance of the processor, while it is impossible to further improve the property of the processor by only increasing the clock frequency. For a processor with integrated multiple cores, its performance is determined not only by the number of cores, but also by communication efficiency between them. With more processor cores integrated on a chip, larger bandwidths are required to establish the communication among them. The traditional electrical interconnect has gradually become a bottleneck for improving the performance of multiple-core processors due to its limited bandwidth, high power consumption, and long latency. The optical interconnect is considered as a potential way to solve this issue. The optical router is the key device for realizing the optical interconnect. Its basic function is to achieve the data routing and switching between the local node and the multi-node. In this paper we present a five-port optical router for Mesh photonics network-on-chip. A five-port optical router composed of eight thermally tuned silicon Mach-Zehnder optical switches is demonstrated. The experimental spectral responses indicate that the optical signal-to-noise ratios of the optical router are over 13 dB in the wavelength range of 1525-1565 nm for all of its 20 optical links. Each optical link can manipulate 50 wavelength channels with the channel spacing of 100 GHz and the data rate of 32 Gbps for each wavelength channel in the same wavelength range. The lowest energy efficiency of the optical router is 43.4 fJ/bit.-

Keywords:

- silicon photonics,

- optical router,

- optical waveguides

-

References

[1] Miller D A B. Device requirements for optical interconnects to silicon chips. Proc IEEE, 2009, 97:1166 doi: 10.1109/JPROC.2009.2014298[2] Joshi A, Batten C, Kwon Y J, et al. Silicon-photonic clos networks for global on-chip communication. 20093rd ACM/IEEE International Symposium on Networks-on-Chip, 2009:124[3] Fang A W, Park H, Cohen O, et al. Electrically pumped hybrid AlGaInAs-silicon evanescent laser. Opt Express, 2006, 14(20):9203 doi: 10.1364/OE.14.009203[4] Qi A Y, Wang Y F, Guo X J, et al. A novel lateral cavity surface emitting laser with top sub-wavelength grating. Chinese Journal of Semiconductors, 2015, 36(1):014012 doi: 10.1088/1674-4926/36/1/014012[5] Thomson D J, Gardes F Y, Hu Y, et al. High contrast 40 Gbit/s optical modulation in silicon. Opt Express, 2011, 19(12):11507 doi: 10.1364/OE.19.011507[6] Fang Q, Liow T Y, Song J F, et al. WDM multi-channel silicon photonic receiver with 320 Gbps data transmission capability. Opt Express, 2010, 18(5):5106 doi: 10.1364/OE.18.005106[7] Michel J, Liu J, Kimerling L C. High-performance Ge-on-Si photodetectors. Nat Photon, 2010, 4(8):527 doi: 10.1038/nphoton.2010.157[8] Shen Ning, Tang Zhen'an, Yu Jun, et al. A low-cost infrared absorbing structure for an uncooled infrared detector in a standard CMOS process. Journal of Semiconductors, 2014, 35(3):034013 doi: 10.1088/1674-4926/35/3/034013[9] Yao Yan, Liu Xiong, Yuan Li, et al. A novel PIN photodetector with double linear arrays for rainfall prediction. Journal of Semiconductors, 2015, 36(9):094011 doi: 10.1088/1674-4926/36/9/094011[10] Yang L, Xia Y H, Zhang F F, et al. Reconfigurable nonblocking 4-port silicon thermo-optic optical router based on Mach-Zehnder optical switches. Opt Lett, 2015, 40(7):1402 doi: 10.1364/OL.40.001402[11] Gu H X, Mo K H, Xu J, et al. A low-power low-cost optical router for optical networks-on-chip in multiprocessor systems-on-chip. Proc IEEE Comput Soc Annu Symp, 2009:19[12] Poon A W, Luo X, Xu F, et al. Cascaded microresonator-based matrix switch for silicon on-chip optical interconnection. Proc IEEE, 2009, 97:1216 doi: 10.1109/JPROC.2009.2014884[13] Ji R Q, Yang L, Zhang L, et al. Five-port optical router for photonic networks-on-chip. Opt Express, 2011, 19(21):20258 doi: 10.1364/OE.19.020258[14] Tan X, Yang M, Zhang L, et al. A generic optical router design for photonic network-on-chips. IEEE/OSA J Lightwave Technol, 2012, 30(3):368 doi: 10.1109/JLT.2011.2178019[15] Lee J H, Yoo J C, Han T H. System-level design framework for insertion-loss-minimized optical network-on-chip router architectures. IEEE/OSA J Lightwave Technol, 2014, 32(18):3161 doi: 10.1109/JLT.2014.2336234[16] Hu T, Shao H, Yang L, et al. Four-port silicon multi-wavelength optical router for photonic networks-on-chip. IEEE Photon Technol Lett, 2013, 25(23):2281 doi: 10.1109/LPT.2013.2285171[17] Sherwood-Droz H, Wang H, Chen L, et al. Optical 4×4 hitless silicon router for optical networks-on-chip (NoC). Opt Express, 2008, 16(20):15915 doi: 10.1364/OE.16.015915[18] Ji R Q, Yang L, Zhang L, et al. Microring-resonator-based fourport optical router for photonic networks-on-chip. Opt Express, 2011, 19(20):18945 doi: 10.1364/OE.19.018945[19] Gu H, Xu J, Wang Z. ODOR:a microresonator-based highperformance low-cost router for optical networks-on-chip. Proceedings of the 6th IEEE/ACM/IFIP international conference on Hardware/Software co-design and system synthesis. ACM, 2008:203[20] Min R, Ji R Q, Chen Q S, et al. A universal method for constructing N -port nonblocking optical router for photonic networks-onchip. IEEE/OSA J Lightwave Technol, 2012, 30(23):3736 doi: 10.1109/JLT.2012.2227945[21] Yang M, Green W M J, Assefa S, et al. Non-blocking 4×4 electro-optic silicon switch for on-chip photonic networks. Opt Express, 2011, 19(1):47 doi: 10.1364/OE.19.000047[22] Chen Q S, Zhang F F, Ji R Q, et al. Universal method for constructing N -port non-blocking optical router based on 2×2 optical switch for photonic networks-on-chip. Opt Express, 2014, 22(10):12614 doi: 10.1364/OE.22.012614[23] Biberman A, Lee B G, Sherwood-Droz N, et al. Broadband operation of nanophotonic router for silicon photonic networks-onchip. IEEE Photon Technol Lett, 2010, 22(10):926[24] Ji R Q, Xu J, Yang L. Five-port optical router based on microring and switches for photonic networks-on-chip. IEEE Photon Technol Lett, 2013, 25(5):492 doi: 10.1109/LPT.2013.2243427[25] Li X, Xiao X, Xu H, et al. Mach-Zehnder-based five-port silicon router for optical interconnects. Opt Lett, 2013, 38(10):1703 doi: 10.1364/OL.38.001703[26] Lee B G, Rylyakov A V, Green W M J, et al. Monolithic silicon integration of scaled photonic switch fabrics, CMOS logic, and device driver circuits. IEEE/OSA J Lightw Technol, 2014, 32(4):743 doi: 10.1109/JLT.2013.2280400[27] Chen L, Chen Y K. Compact, low-loss and low-power 8×8 broadband silicon optical switch. Opt Express, 2012, 20(17):18977 doi: 10.1364/OE.20.018977[28] Lu L, Zhou L, Zhang F, et al. Broadband 4×4 nonblocking silicon electrooptic switches based on Mach-Zehnder interferometers. IEEE Photon J, 2015, 7(1):1[29] Soldano L B, Pennings E C M. Optical multi-mode devices based on self-imaging:principles and applications. IEEE/OSA J Lightw Technol, 1995, 13(4):615 doi: 10.1109/50.372474 -

Proportional views

DownLoad:

DownLoad: