| Citation: |

Jingjing Wang, Zemin Feng, Rongjin Xu, Chixiao Chen, Fan Ye, Jun Xu, Junyan Ren. A 100 MS/s 9 bit 0.43 mW SAR ADC with custom capacitor array[J]. Journal of Semiconductors, 2016, 37(5): 055003. doi: 10.1088/1674-4926/37/5/055003

****

J J Wang, Z M Feng, R J Xu, C X Chen, F Ye, J Xu, J Y Ren. A 100 MS/s 9 bit 0.43 mW SAR ADC with custom capacitor array[J]. J. Semicond., 2016, 37(5): 055003. doi: 10.1088/1674-4926/37/5/055003.

|

A 100 MS/s 9 bit 0.43 mW SAR ADC with custom capacitor array

DOI: 10.1088/1674-4926/37/5/055003

More Information

-

Abstract

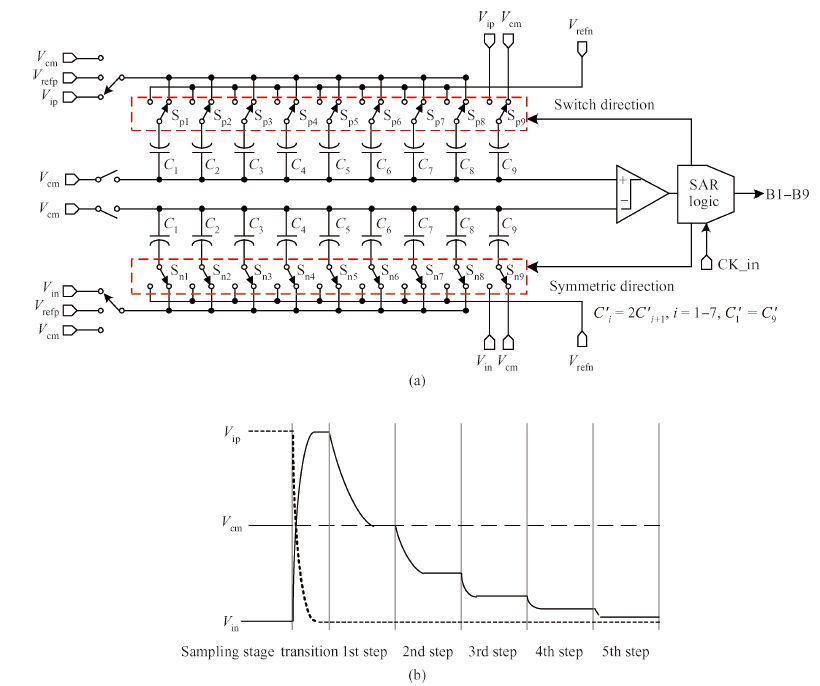

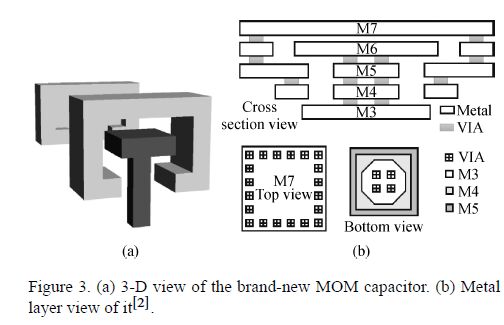

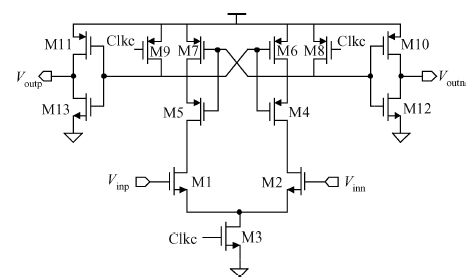

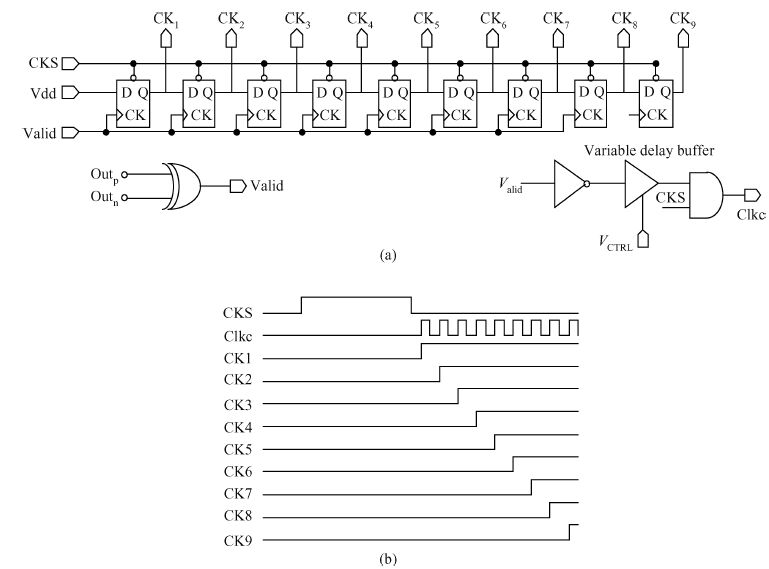

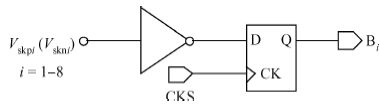

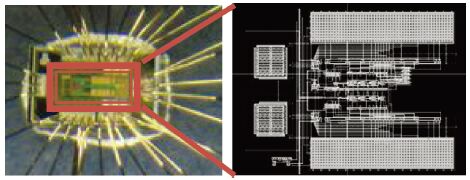

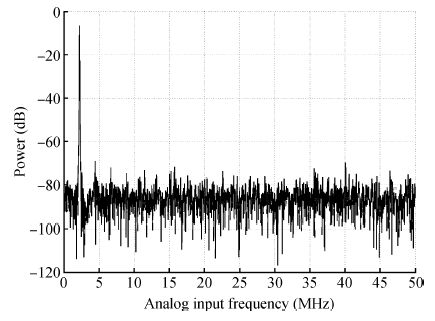

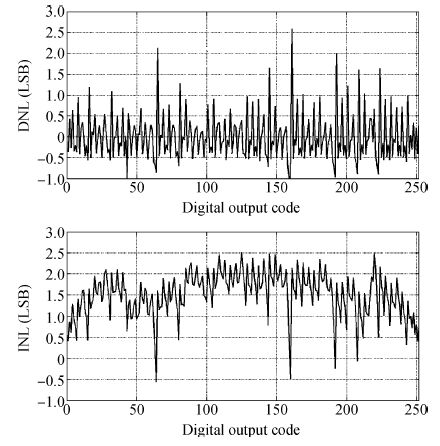

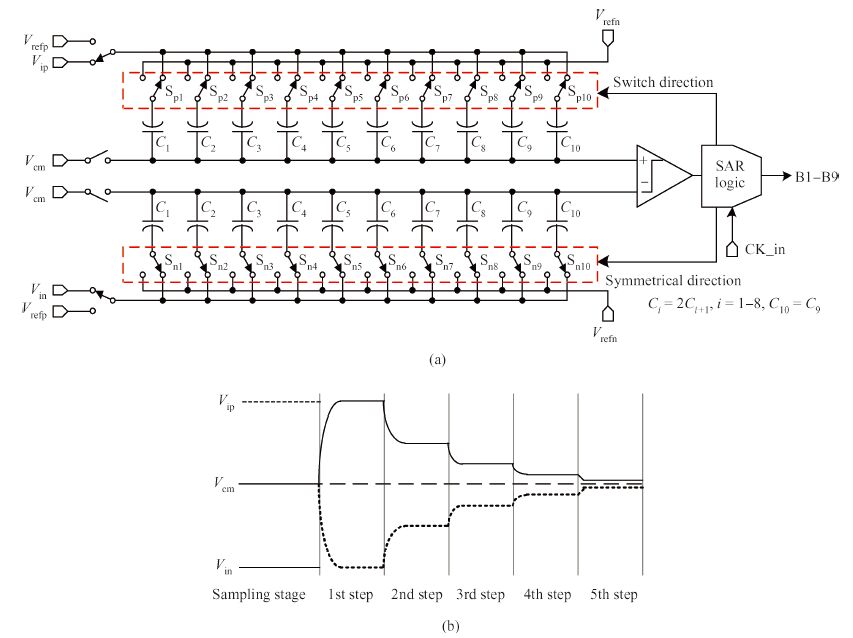

A low power 9 bit 100 MS/s successive approximation register analog-to-digital converter (SAR ADC) with custom capacitor array is presented. A brand-new 3-D MOM unit capacitor is used as the basic capacitor cell of this capacitor array. The unit capacitor has a capacitance of 1 fF. Besides, the advanced capacitor array structure and switch mode decrease the power consumption a lot. To verify the effectiveness of this low power design, the 9 bit 100 MS/s SAR ADC is implemented in TSMC IP9M 65 nm LP CMOS technology. The measurement results demonstrate that this design achieves an effective number of bits (ENOB) of 7.4 bit, a signal-to-noise plus distortion ratio (SNDR) of 46.40 dB and a spurious-free dynamic range (SFDR) of 62.31 dB at 100 MS/s with 1 MHz input. The SAR ADC core occupies an area of 0.030 mm2 and consumes 0.43 mW under a supply voltage of 1.2 V. The figure of merit (FOM) of the SAR ADC achieves 23.75 fJ/conv. -

References

[1] [2] [3] [4] [5] [6] [7] -

Proportional views

DownLoad:

DownLoad: