| Citation: |

Xuqiang Zheng, Fule Li, Zhijun Wang, Weitao Li, Wen Jia, Zhihua Wang, Shigang Yue. An S/H circuit with parasitics optimized for IF-sampling[J]. Journal of Semiconductors, 2016, 37(6): 065005. doi: 10.1088/1674-4926/37/6/065005

****

X Q Zheng, F L Li, Z J Wang, W T Li, W Jia, Z H Wang, S G Yue. An S/H circuit with parasitics optimized for IF-sampling[J]. J. Semicond., 2016, 37(6): 065005. doi: 10.1088/1674-4926/37/6/065005.

|

An S/H circuit with parasitics optimized for IF-sampling

DOI: 10.1088/1674-4926/37/6/065005

More Information

-

Abstract

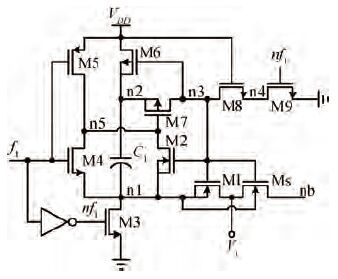

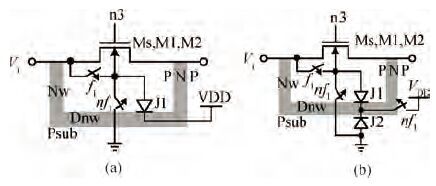

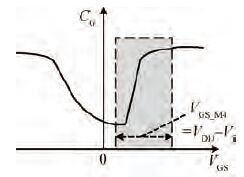

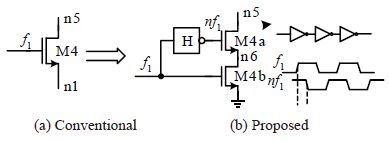

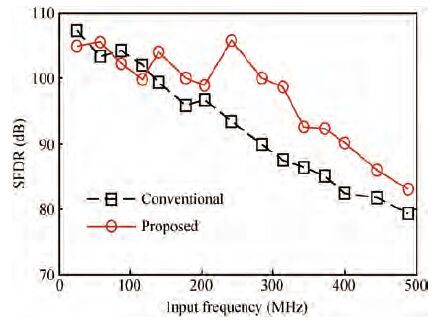

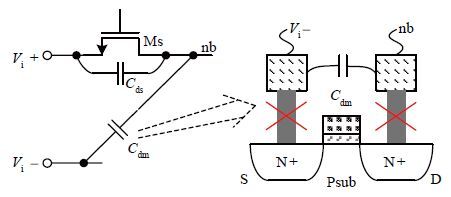

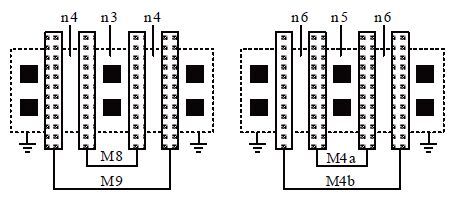

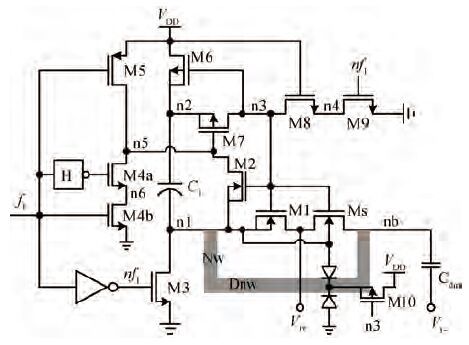

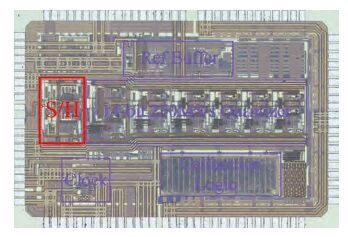

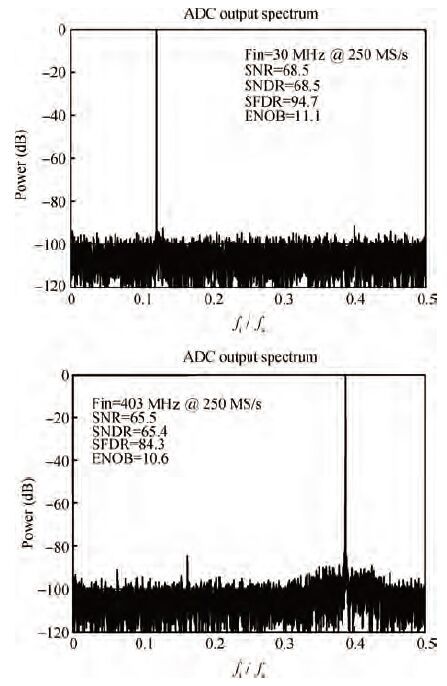

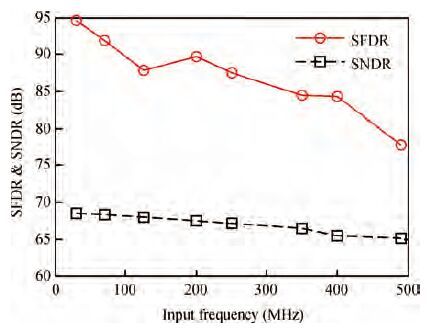

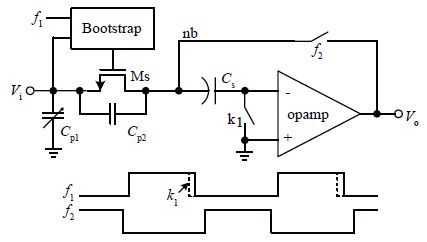

An IF-sampling S/H is presented, which adopts a flip-around structure, bottom-plate sampling technique and improved input bootstrapped switches. To achieve high sampling linearity over a wide input frequency range, the floating well technique is utilized to optimize the input switches. Besides, techniques of transistor load linearization and layout improvement are proposed to further reduce and linearize the parasitic capacitance. The S/H circuit has been fabricated in 0.18-μm CMOS process as the front-end of a 14 bit, 250 MS/s pipeline ADC. For 30 MHz input, the measured SFDR/SNDR of the ADC is 94.7 dB/68. 5dB, which can remain over 84.3 dB/65.4 dB for input frequency up to 400 MHz. The ADC presents excellent dynamic performance at high input frequency, which is mainly attributed to the parasitics optimized S/H circuit. -

References

[1] Chu M, Kim B, Lee B G. A 10-bit 200-MS/s zero-crossing-based pipeline ADC in 0.13-μm CMOS technology. IEEE Trans Very Large Scale Integration Systems, 2015, 23(11):2671[2] Sehgal R, van der Goes F, Bult K. A 12 b 53 mW 195 MS/s pipeline ADC with 82 dB SFDR using split-ADC calibration. IEEE J Solid-State Circuits, 2015, 50(7):1592[3] Yin Xiumei, Wei Qi, Xu Lai, et al. A low power 12-b 40-MS/s pipeline ADC. Journal of Semiconductors, 2012, 31(3):035006[4] Chen Zhenhai, Qian Hongwen, Huang Songren, et al. A low power time-interleaved 10-bit 250-MSPS charge domain pipelined ADC for IF sampling. Journal of Semiconductors, 2013, 34(6):065005[5] Dessouky M, Kaiser A. Input switch configuration for rail-to-rail operation of switched opamp circuits. Electron Lett, 1999, 35(1):8[6] Zhao Nan, Luo Hua, Wei Qi, et al. A 14-bit 100-MS/s 85.2-dB SFDR pipelined ADC without calibration. Journal of Semiconductors, 2014, 35(7):075006[7] Luo L Lin K, Cheng L, et al. A digitally calibrated 14-bit linear 100-MS/s pipelined ADC with wideband sampling front end. IEEE European Solid-State Circuits Conference, 2009:472[8] Cheng C, Chang S J, Huang G Y, et al. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J Solid-State Circuits, 2010, 45(4):731[9] Jing Xin, Zhuang Yiqi, Tang Hualian, et al. A power-efficient 12-bit analog-to-digital converter with a novel constant-resistance CMOS input sampling switch. Journal of Semiconductors, 2014, 35(2):025002[10] Ali A, Morgan A, Dillon C, et al. A 16-bit 250-MS/s IF sampling pipelined ADC with background calibration. IEEE J Solid-State Circuits, 2010, 45(12):2602[11] Wang Z, Wang M, Gu W, et al. A high-linearity pipelined ADC with opamp split-sharing in a combined front-end of S/H and MDAC1. IEEE Trans Circuits Syst I:Regular Papers, 2013, 60(11):2834[12] Yang C, Li L, Li W, et al. An 85 mW 14-bit 150 MS/s pipelined ADC with 71.3 dB peak SNDR in 130 nm CMOS. IEEE Asian Solid-State Circuits Conference, 2013:85 -

Proportional views

DownLoad:

DownLoad: