| Citation: |

Changjun Liao, Jizhi Liu, Zhiwei Liu. A novel HBT trigger SCR in 0.35 μm SiGe BiCMOS technology[J]. Journal of Semiconductors, 2016, 37(9): 094004. doi: 10.1088/1674-4926/37/9/094004

****

C J Liao, J Z Liu, Z W Liu. A novel HBT trigger SCR in 0.35 μm SiGe BiCMOS technology[J]. J. Semicond., 2016, 37(9): 094004. doi: 10.1088/1674-4926/37/9/094004.

|

A novel HBT trigger SCR in 0.35 μm SiGe BiCMOS technology

DOI: 10.1088/1674-4926/37/9/094004

More Information

-

Abstract

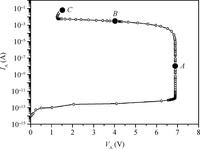

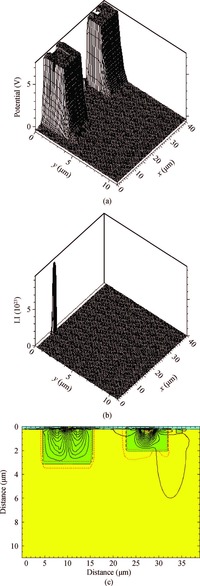

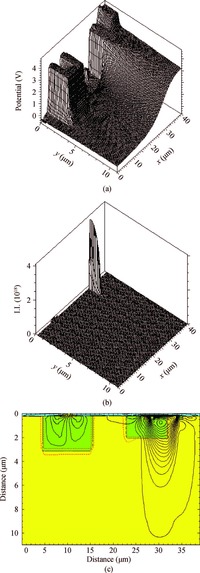

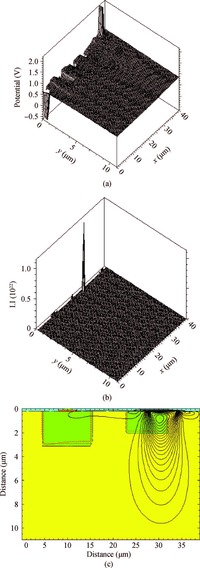

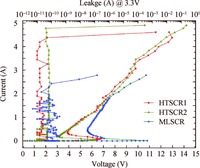

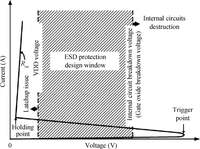

The silicon-controlled rectifier (SCR) device is known as an efficient electrostatic discharge (ESD) protection device due to the highest ESD robustness in the smallest layout area. However, SCR has some drawbacks, such as high trigger voltage and low holding voltage. In order to reduce the trigger voltage of the SCR device for ESD protection, a new heterojunction bipolar transistor (HBT) trigger silicon controlled rectifier (HTSCR) device in 0.35 μm SiGe BiCMOS technology are proposed. The underlying physical mechanisms critical to the trigger voltage are demonstrated based on transmission line pulsing (TLP) measurement and physics-based simulation results. The simulation results prove that the trigger voltage of the HTSCR is decided by the collector-to-emitter breakdown voltage of the HBT structure in floating base configuration. The ESD experiment test results demonstrate the HTSCR can offer superior performance with a small trigger voltage, an adjustable holding voltage and a high ESD robustness. In comparison to the conventional MLSCR, the trigger voltage of the fabricated HTSCR can reduce to less than 50% of that of the MLSCR, and the It2 of the HBT trigger SCR is 80% more than that of the MLSCR. -

References

[1] Gotsfried R, Beisswanger F, Gerlach S, et al. RFIC's for mobile communication systems using SiGe bipolar technology. IEEE Trans Microw Theory Tech, 1998, 46(5): 661 doi: 10.1109/22.668679[2] Voldman S, Juliano P, Botula A, et al. ESD robustness of BiCMOS SiGe technology. Proc IEEE Bipolar/BiCMOS Circuits and Technology Meeting, 2000[3] Voldman S, Botula A, Hui D, et al. Silicon germanium heterojunction bipolar transistor ESD power clamps and the Johnson limit. Proc EOS/ESD Symp, 2001[4] Ker M D, Hsu K C. Overview of on-chip electrostatic discharge protection design with SCR-based devices in CMOS integrated circuits. IEEE Trans Device Mater Reliab, 2005, 5(1): 235[5] Bi Xiuwen, Liang Hailian, Gu Xiaofeng, et al. Design of novel DDSCR with embedded PNP structure for ESD protection. Journal of Semiconductors, 2015, 36(12): 124007 doi: 10.1088/1674-4926/36/12/124007[6] Liu Jizhi, Liu Zhiwei, Jia Ze, et al. A novel DTSCR with a variation lateral base doping structure to improve turn-on speed for ESD protection. Journal of Semiconductors, 2014, 35(6): 064010 doi: 10.1088/1674-4926/35/6/064010[7] Dong Shurong, Jin Hao, Miao Meng, et al. Novel capacitance coupling complementary dual-direction SCR for high-voltage ESD. IEEE Electron Device Lett, 2012, 33(5): 640 doi: 10.1109/LED.2012.2188015[8] Pan Hongwei, Liu Siyang, Sun Weifeng. A novel latch-up free SCR-LDMOS with high holding voltage for a power-rail ESD clamp. Journal of Semiconductors, 2013, 34(1): 014007 doi: 10.1088/1674-4926/34/1/014007[9] Lin Chunyu, Chu Liwei, Ker Mingdou. ESD protection design for 60-GHz LNA with inductor-triggered SCR in 65-nm CMOS process. IEEE Trans Microw Theory Tech, 2012, 60(3): 714 doi: 10.1109/TMTT.2011.2178425[10] Li Li, Liu Hongxia. A novel double-trench LVTSCR used in the ESD protection of a RFIC. Journal of Semiconductors, 2011, 32(10): 104005 doi: 10.1088/1674-4926/32/10/104005[11] Liu Z W, He J, Liou J J, et al. Segmented SCR for high voltage ESD protection. 2012 IEEE 11th International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2012[12] Yeh Chihting, Liang Yungchih, Ker Mingdou. PMOS-based power-rail ESD clamp circuit with adjustable holding voltage controlled by ESD detection circuit. Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), 2011[13] Ker Mingdou, Lin Wanyen. New design of transient-noise detection circuit with SCR device for system-level ESD protection. 2012 IEEE 10th International New Circuits and Systems Conference (NEWCAS), 2012 http://cn.bing.com/academic/profile?id=2028291497&encoded=0&v=paper_preview&mkt=zh-cn[14] Zhang Shuai, Dong Shurong, Wu Xiaojing, et al. An improved GGNMOS triggered SCR for high holding voltage ESD protection applications. Chin Phys B, 2015, 24(10): 108502 doi: 10.1088/1674-1056/24/10/108502[15] Ker Mingdou, Chen Shihhung. Implementation of initial-on ESD protection concept with PMOS-triggered SCR devices in deep-submicron CMOS technology. IEEE J Solid-State Circuits, 2007, 42(5):1158 doi: 10.1109/JSSC.2007.894823[16] Harame D, Comfort F, Cressler J, et al. Si/SiGe epitaxial base transistors-Part I: materials, physics, and circuits. IEEE Trans Electron Devices, 1995, 42(3): 455 doi: 10.1109/16.368039[17] Harame D, Comfort F, Cressler J, et al. Si/SiGe epitaxial base transistors-Part Ⅱ: process integration and analog applications. IEEE Trans Electron Devices, 1995, 42(3): 469 doi: 10.1109/16.368043[18] Duvvury C, Rountree R. A synthesis of ESD input protection scheme. Proc EOS/ESD Symp, 1991 -

Proportional views

DownLoad:

DownLoad: