| Citation: |

Chi-Hang Chan, Lin Cheng, Wei Deng, Peng Feng, Li Geng, Mo Huang, Haikun Jia, Lu Jie, Ka-Meng Lei, Xihao Liu, Xun Liu, Yongpan Liu, Yan Lu, Kaiming Nie, Dongfang Pan, Nan Qi, Sai-Weng Sin, Nan Sun, Wenyu Sun, Jiangtao Xu, Jinshan Yue, Milin Zhang, Zhao Zhang. Trending IC design directions in 2022[J]. Journal of Semiconductors, 2022, 43(7): 071401. doi: 10.1088/1674-4926/43/7/071401

****

C H Chan, L Cheng, W Deng, P Feng, L Geng, M Huang, H K Jia, L Jie, K M Lei, X H Liu, X Liu, Y P Liu, Y Lu, K M Nie, D F Pan, N Qi, S W Sin, N Sun, W Y Sun, J T Xu, J S Yue, M L Zhang, Z Zhang. Trending IC design directions in 2022[J]. J. Semicond, 2022, 43(7): 071401. doi: 10.1088/1674-4926/43/7/071401

|

-

Abstract

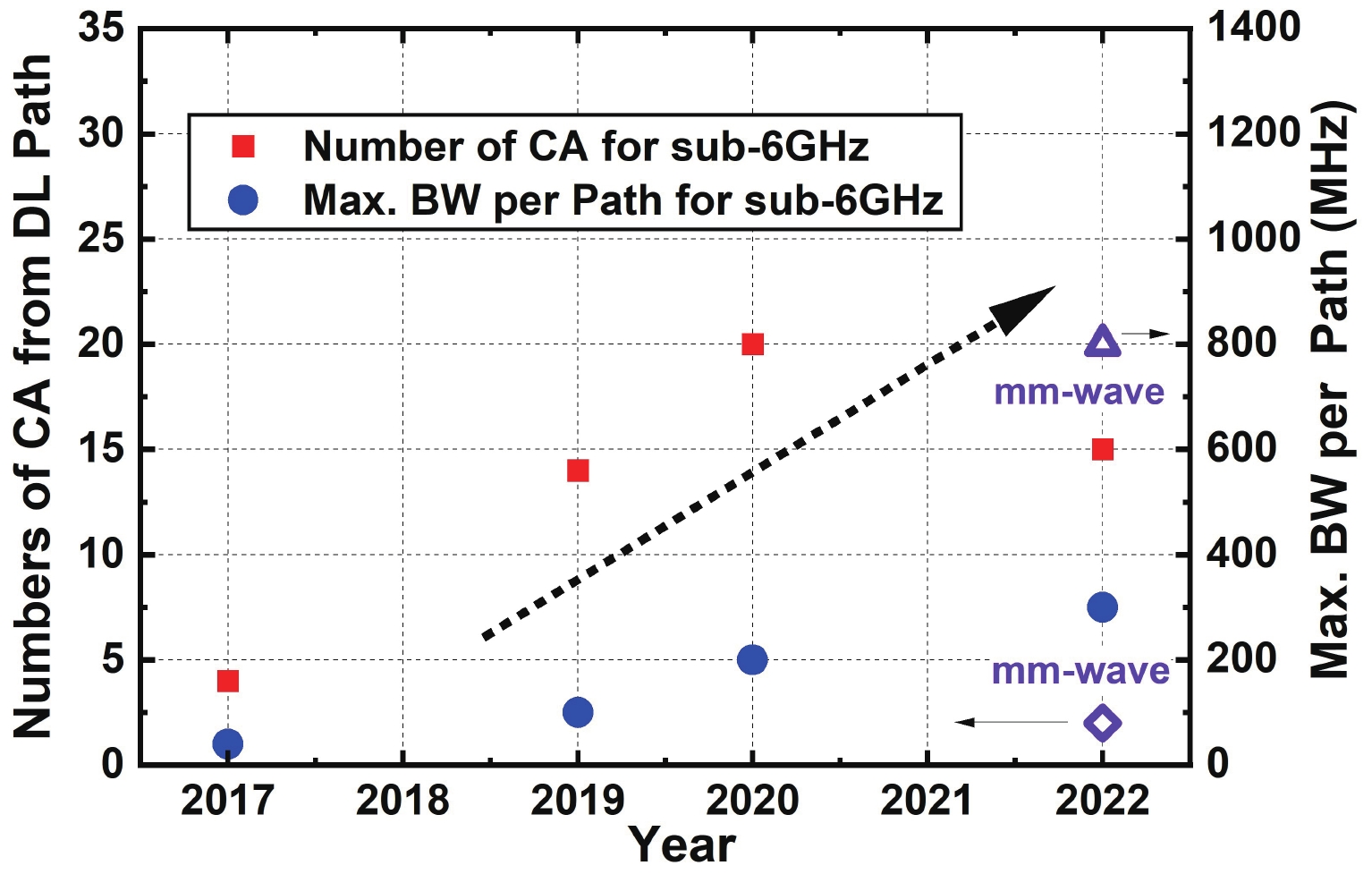

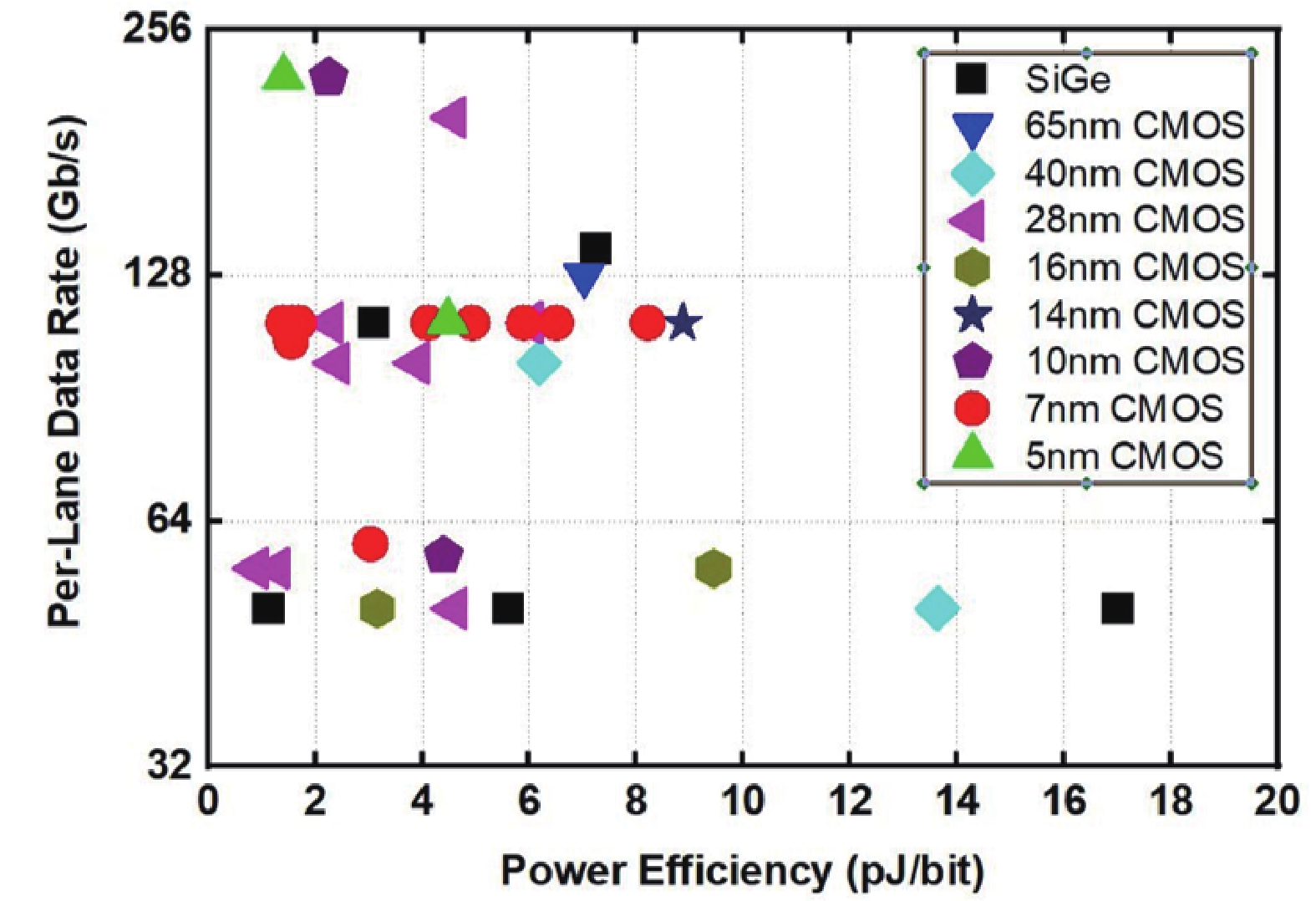

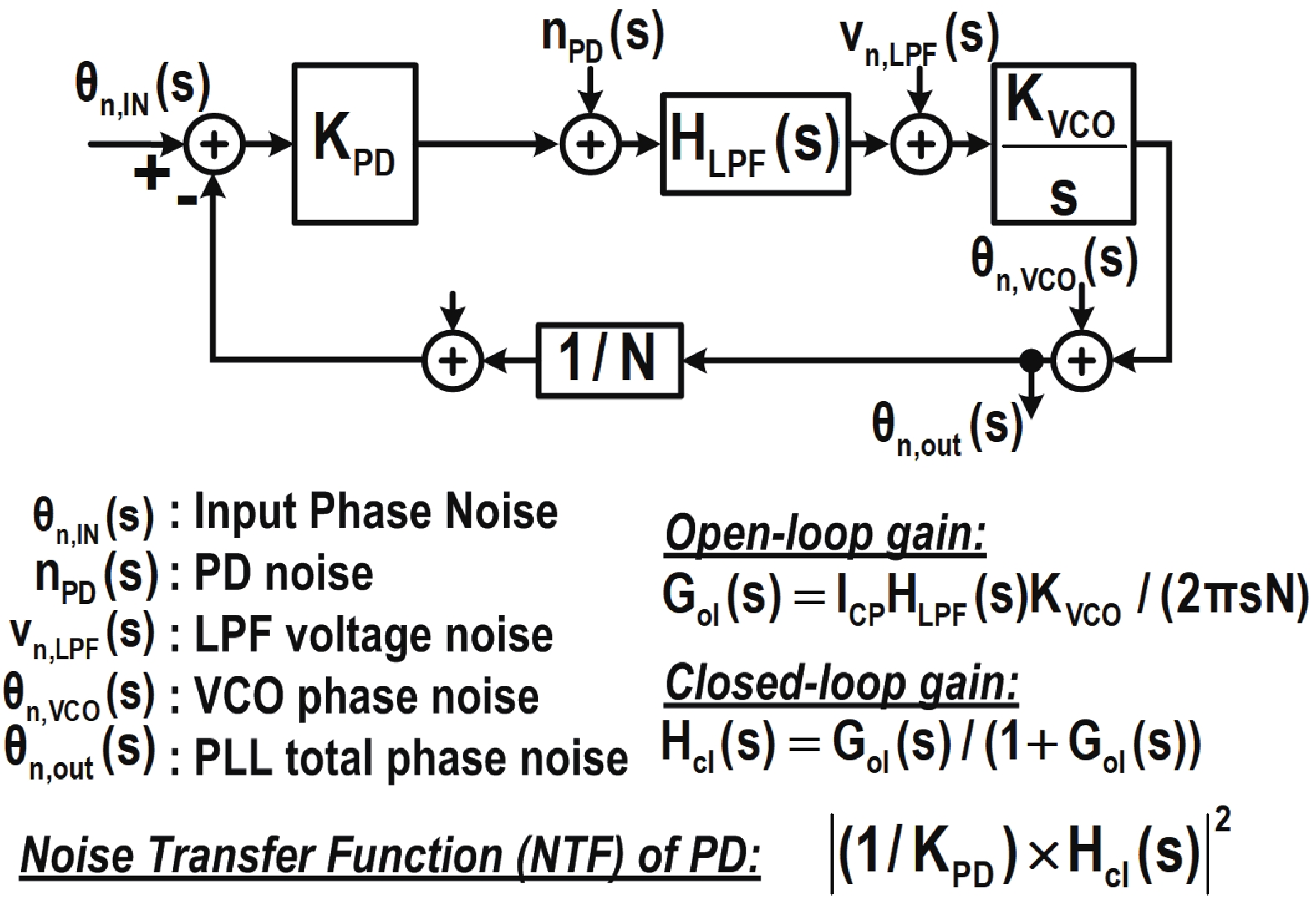

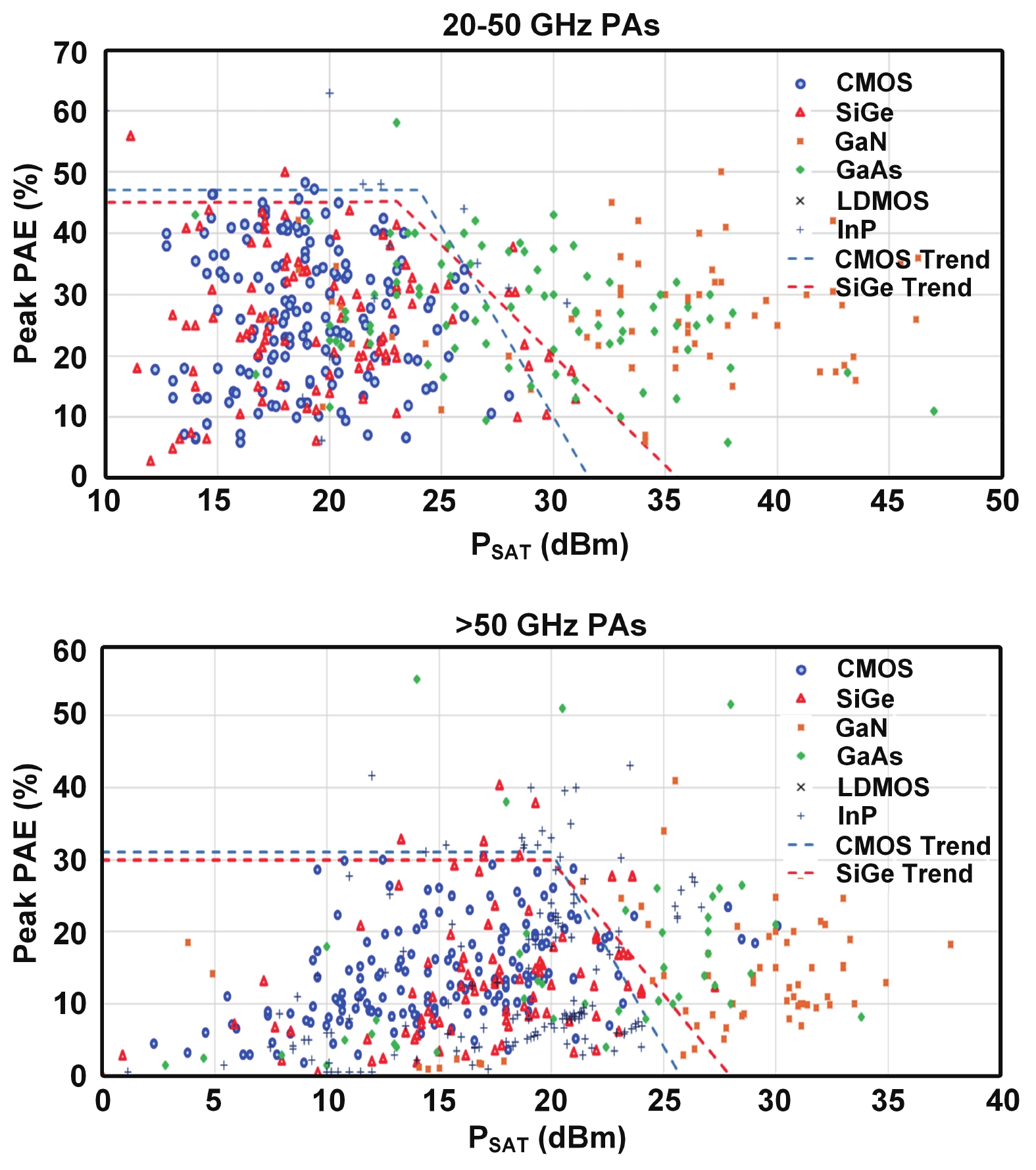

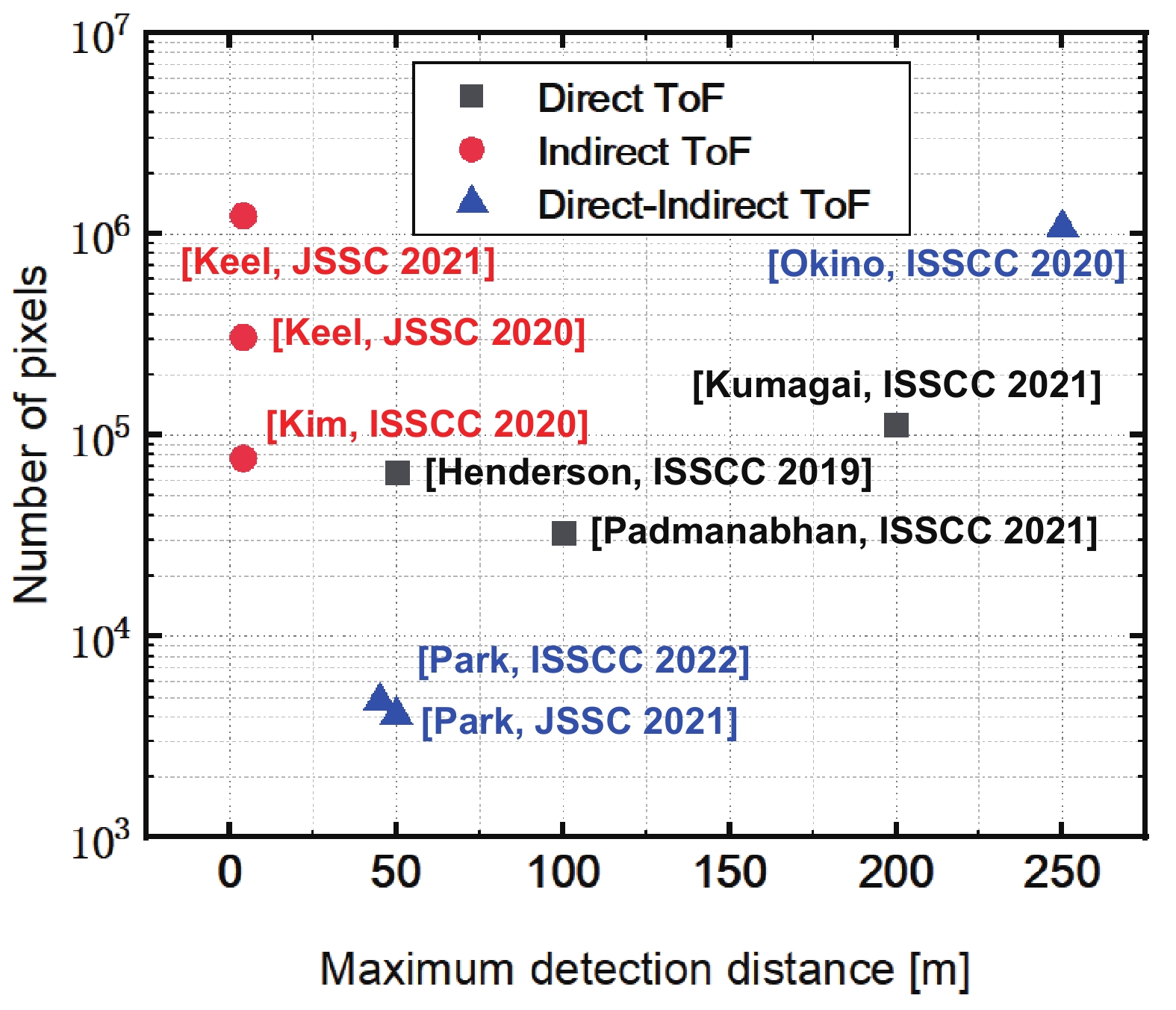

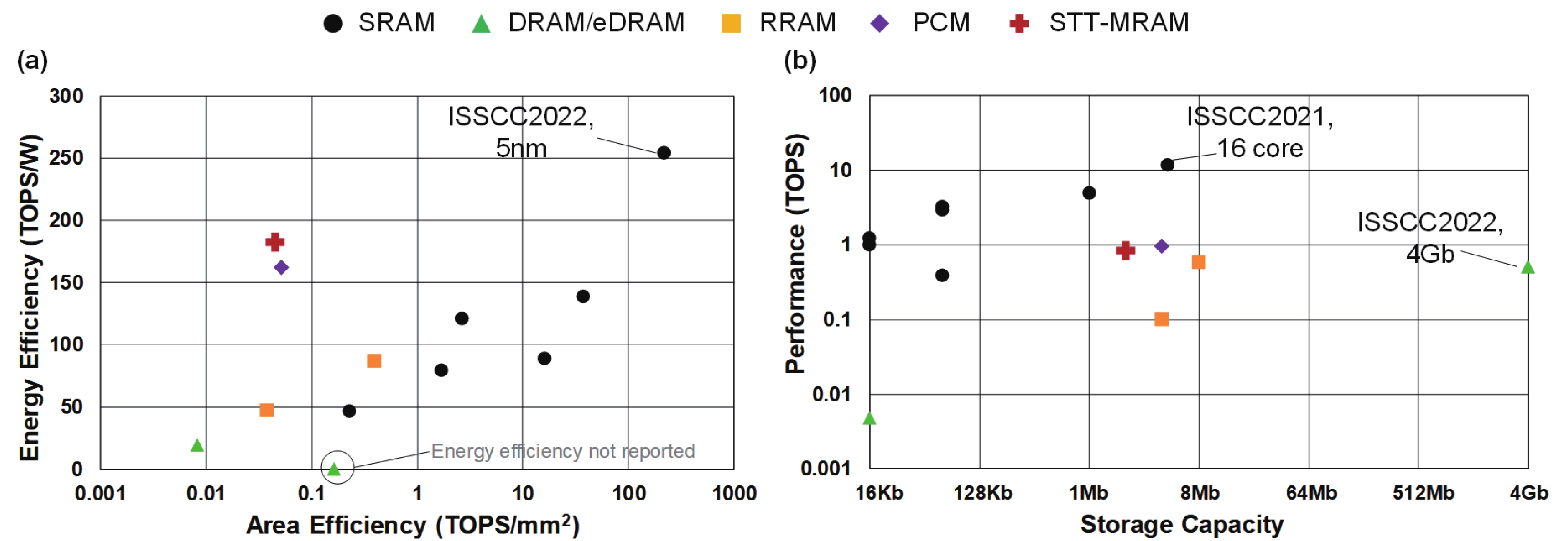

For the non-stop demands for a better and smarter society, the number of electronic devices keeps increasing exponentially; and the computation power, communication data rate, smart sensing capability and intelligence are always not enough. Hardware supports software, while the integrated circuit (IC) is the core of hardware. In this long review paper, we summarize and discuss recent trending IC design directions and challenges, and try to give the readers big/cool pictures on each selected small/hot topics. We divide the trends into the following six categories, namely, 1) machine learning and artificial intelligence (AI) chips, 2) communication ICs, 3) data converters, 4) power converters, 5) imagers and range sensors, 6) emerging directions. Hope you find this paper useful for your future research and works. -

References

[1] Shan W W, Yang M H, Xu J M, et al. A 510nW 0.41V low-memory low-computation keyword-spotting chip using serial FFT-based MFCC and binarized depthwise separable convolutional neural network in 28nm CMOS. 2020 IEEE International Solid-State Circuits Conference, 2020, 230[2] Wang D W, Kim S J, Yang M H, et al. A background-noise and process-variation-tolerant 109nW acoustic feature extractor based on spike-domain divisive-energy normalization for an always-on keyword spotting device. 2021 IEEE International Solid-State Circuits Conference, 2021, 64, 160[3] Tambe T, Yang E Y, Ko G G, et al. A 25mm2 SoC for IoT devices with 18ms noise-robust speech-to-text latency via Bayesian speech denoising and attention-based sequence-to-sequence DNN speech recognition in 16nm FinFET. 2021 IEEE International Solid-State Circuits Conference, 2021, 64, 158[4] Cho M, Oh S, Shi Z, et al. A 142nW voice and acoustic activity detection chip for mm-scale sensor nodes using time-interleaved mixer-based frequency scanning. 2019 IEEE International Solid-State Circuits Conference, 2019, 278[5] Chen F F, Un K F, Yu W H, et al. A 108nW 0.8mm2 analog voice activity detector (VAD) featuring a time-domain CNN as a programmable feature extractor and a sparsity-aware computational scheme in 28nm CMOS. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[6] Lu Y C, le V L, Kim T T H. A 184µW real-time hand-gesture recognition system with hybrid tiny classifiers for smart wearable devices. 2021 IEEE International Solid-State Circuits Conference, 2021, 64, 156[7] Im D, Park G, Li Z Y, et al. DSPU: A 281.6mW real-time depth signal processing unit for deep learning-based dense RGB-D data acquisition with depth fusion and 3D bounding box extraction in mobile platforms. 2022 IEEE International Solid-State Circuits Conference, 2022, 33.4[8] Yuan Z, Yang Y X, Yue J S, et al. A 65nm 24.7µJ/frame 12.3mW activation-similarity-aware convolutional neural network video processor using hybrid precision, inter-frame data reuse and mixed-bit-width difference-frame data codec. 2020 IEEE International Solid-State Circuits Conference, 2020, 232[9] Wang Y, Qin Y B, Deng D Z, et al. A 28nm 27.5TOPS/W approximate-computing-based transformer processor with asymptotic sparsity speculating and out-of-order computing. 2022 IEEE International Solid-State Circuits Conference, 2022, 29.2[10] Tu F B, Wu Z H, Wang Y Q, et al. A 28nm 15.59µJ/token full-digital bitline-transpose CIM-based sparse transformer accelerator with pipeline/parallel reconfigurable modes. 2022 IEEE International Solid-State Circuits Conference, 2022, 29.3[11] Eki R, Yamada S, Ozawa H, et al. A 1/2.3inch 12.3Mpixel with on-chip 4.97TOPS/W CNN processor back-illuminated stacked CMOS image sensor. 2021 IEEE International Solid-State Circuits Conference, 2021, 9.6[12] Niu D M, Li S C, Wang Y H, et al. 184QPS/W 64Mb/mm2 3D logic-to-DRAM hybrid bonding with process-near-memory engine for recommendation system. 2022 IEEE International Solid-State Circuits Conference, 2022, 29.1[13] Si X, Tu Y N, Huang W H, et al. A 28nm 64Kb 6T SRAM computing-in-memory macro with 8b MAC operation for AI edge chips. 2020 IEEE International Solid-State Circuits Conference, 2020, 246[14] Yue J S, Yuan Z, Feng X Y, et al. A 65nm computing-in-memory-based CNN processor with 2.9-to-35.8 TOPS/W system energy efficiency using dynamic-sparsity performance-scaling architecture and energy-efficient inter/intra-macro data reuse. 2020 IEEE International Solid-State Circuits Conference, 2020, 234[15] Yue J S, Feng X Y, He Y F, et al. A 2.75-to-75.9 TOPS/W computing-in-memory NN processor supporting set-associate block-wise zero skipping and Ping-pong CIM with simultaneous computation and weight updating. 2021 IEEE International Solid-State Circuits Conference, 2021, 238[16] Chih Y D, Lee P H, Fujiwara H, et al. An 89TOPS/W and 16.3 TOPS/mm2 all-digital SRAM-based full-precision compute-in memory macro in 22nm for machine-learning edge applications. 2021 IEEE International Solid-State Circuits Conference, 2021, 64, 252[17] Yan B N, Hsu J L, Yu P C, et al. A 1.041-Mb/mm2 27.38-TOPS/W signed-INT8 dynamic-logic-based ADC-less SRAM compute-in-memory macro in 28nm with reconfigurable bitwise operation for AI and embedded applications. 2022 IEEE International Solid-State Circuits Conference, 2022, 188[18] Wu P C, Su J W, Chung Y L, et al. A 28nm 1Mb time-domain computing-in-memory 6T-SRAM macro with a 6.6ns latency, 1241GOPS and 37.01 TOPS/W for 8 b-MAC operations for edge-AI devices. 2022 IEEE International Solid-State Circuits Conference, 2022, 190[19] Hung J M, Huang Y H, Huang S P, et al. An 8-Mb DC-current-free binary-to-8b precision ReRAM nonvolatile computing-in-memory macro using time-space-readout with 1286.4 TOPS/W-21.6 TOPS/W for edge-AI devices. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[20] Fujiwara H, Mori H, Zhao W C, et al. A 5-nm 254-TOPS/W 221-TOPS/mm2 fully-digital computing-in-memory macro supporting wide-range dynamic-voltage-frequency scaling and simultaneous MAC and write operations. 2022 IEEE International Solid-State Circuits Conference, 2022, 186[21] Wang D W, Lin C T, Chen G K, et al. DIMC: 2219TOPS/W 2569F2/b digital in-memory computing macro in 28nm based on approximate arithmetic hardware. 2022 IEEE International Solid-State Circuits Conference, 2022, 266[22] Su J W, Chou Y C, Liu R H, et al. A 28nm 384kb 6T-SRAM computation-in-memory macro with 8b precision for AI edge chips. 2021 IEEE International Solid-State Circuits Conference, 2021, 250[23] Jia H Y, Ozatay M, Tang Y Q, et al. A programmable neural-network inference accelerator based on scalable in-memory computing. 2021 IEEE International Solid-State Circuits Conference, 2021, 236[24] Su J W, Si X, Chou Y C, et al. A 28nm 64Kb inference-training two-way transpose multibit 6T SRAM compute-in-memory macro for AI edge chips. 2020 IEEE International Solid-State Circuits Conference, 2020, 240[25] Ueyoshi K, Papistas I A, Houshmand P, et al. DIANA: an end-to-end energy-efficient digital and ANAlog hybrid neural network SoC. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[26] Guo R Q, Yue Z H, Si X, et al. A 5.99-to-691.1 TOPS/W tensor-train in-memory-computing processor using bit-level-sparsity-based optimization and variable-precision quantization. 2021 IEEE International Solid-State Circuits Conference, 2021, 242[27] Tu F B, Wang Y Q, Wu Z H, et al. A 28nm 29.2TFLOPS/W BF16 and 36.5TOPS/W INT8 reconfigurable digital CIM processor with unified FP/INT pipeline and bitwise in-memory booth multiplication for cloud deep learning acceleration. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[28] Xie S S, Ni C, Sayal A, et al. eDRAM-CIM: Compute-in-memory design with reconfigurable embedded-dynamic-memory array realizing adaptive data converters and charge-domain computing. 2021 IEEE International Solid-State Circuits Conference, 2021, 248[29] Lee S, Kim K, Oh S, et al. A 1nm 1.25V 8Gb, 16Gb/s/pin GDDR6-based accelerator-in-memory supporting 1TFLOPS MAC operation and various activation functions for deep-learning applications. 2022 IEEE International Solid-State Circuits Conference, 2022, 178[30] Chen Z Y, Chen X, Gu J. A 65nm 3T dynamic analog RAM-based computing-in-memory macro and CNN accelerator with retention enhancement, adaptive analog sparsity and 44 TOPS/W system energy efficiency. 2021 IEEE International Solid-State Circuits Conference, 2021, 240[31] Xue C X, Huang T Y, Liu J S, et al. A 22nm 2Mb ReRAM compute-in-memory macro with 121-28 TOPS/W for multibit MAC computing for tiny AI edge devices. 2020 IEEE International Solid-State Circuits Conference, 2020, 244[32] Xue C X, Hung J M, Kao H Y, et al. A 22nm 4Mb 8b-precision ReRAM computing-in-memory macro with 11.91 to 195.7 TOPS/W for tiny AI edge devices. 2021 IEEE International Solid-State Circuits Conference, 2021, 245[33] Liu Q, Gao B, Yao P, et al. A fully integrated analog ReRAM based 78.4 TOPS/W compute-in-memory chip with fully parallel MAC computing. 2020 IEEE International Solid-State Circuits Conference, 2020, 500[34] Chiu Y C, Yang C S, Teng S H, et al. A 22nm 4Mb STT-MRAM data-encrypted near-memory computation macro with a 192GB/s read-and-decryption bandwidth and 25.1-55.1 TOPS/W 8b MAC for AI operations. 2022 IEEE International Solid-State Circuits Conference, 2022, 178[35] Khwa W S, Chiu Y C, Jhang C J, et al. A 40-nm, 2M-cell, 8b-precision, hybrid SLC-MLC PCM computing-in-memory macro with 20.5-65.0 TOPS/W for tiny-Al edge devices. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[36] Tsai M D, Yang S Y, Yu C Y, et al. A 12nm CMOS RF transceiver supporting 4G/5G UL MIMO. 2020 IEEE International Solid-State Circuits Conference, 2020, 176[37] Lee J, Kang B, Joo S, et al. A low-power and low-cost 14nm FinFET RFIC supporting legacy cellular and 5G FR1. 2021 IEEE International Solid-State Circuits Conference, 2021, 90[38] Sung B, Seok H G, Kim J, et al. A single-path digital-IF receiver supporting inter/intra 5-CA with a single integer LO-PLL in 14nm CMOS FinFET. 2022 IEEE International Solid-State Circuits Conference, 2022, 440[39] Sowlati T, Sarkar S, Perumana B, et al. A 60GHz 144-element phased-array transceiver with 51dBm maximum EIRP and ±60° beam steering for backhaul application. 2018 IEEE International Solid-State Circuits Conference, 2018, 66[40] Verma A, Bhagavatula V, Singh A, et al. A 16-channel, 28/39GHz dual-polarized 5G FR2 phased-array transceiver IC with a quad-stream IF transceiver supporting non-contiguous carrier aggregation up to 1.6GHz BW. 2022 IEEE International Solid-State Circuits Conference, 2022[41] Naviasky E, Iotti L, LaCaille G, et al. A 71-to-86 GHz packaged 16-element by 16-beam multi-user beamforming integrated receiver in 28nm CMOS. 2021 IEEE International Solid-State Circuits Conference, 2021, 218[42] Giannini V, Goldenberg M, Eshraghi A, et al. A 192-virtual-receiver 77/79GHz GMSK code-domain MIMO radar system-on-chip. 2019 IEEE International Solid-State Circuits Conference, 2019, 164[43] Duan Z M, Wu B W, Zhu C M, et al. A 76-to-81 GHz 2×8 FMCW MIMO radar transceiver with fast chirp generation and multi-feed antenna-in-package array. 2021 IEEE International Solid-State Circuits Conference, 2021, 228[44] Ma T K, Deng W, Chen Z P, et al. A CMOS 76–81-GHz 2-TX 3-RX FMCW radar transceiver based on mixed-mode PLL chirp generator. IEEE J Solid State Circuits, 2020, 55, 233 doi: 10.1109/JSSC.2019.2950184[45] Saeidi H, Venkatesh S, Lu X, et al. THz prism: One-shot simultaneous multi-node angular localization using spectrum-to-space mapping with 360-to-400 GHz broadband transceiver and dual-port integrated leaky-wave antennas. 2021 IEEE International Solid-State Circuits Conference, 2021, 314[46] Abdo I, da Gomez C, Wang C, et al. A 300GHz-band phased-array transceiver using Bi-directional outphasing and hartley architecture in 65nm CMOS. 2021 IEEE International Solid-State Circuits Conference, 2021, 316[47] Mangal V, Kinget P R. A 0.42nW 434MHz -79.1dBm wake-up receiver with a time-domain integrator. 2019 IEEE International Solid-State Circuits Conference, 2019, 438[48] Lee G, Lee S, Kim J H, et al. A 1.125Gb/s 28mW 2m-radio-range IR-UWB CMOS transceiver. 2021 IEEE International Solid-State Circuits Conference, 2021, 302[49] Im J, Zheng K, Chou C H A, et al. A 112-Gb/s PAM-4 long-reach wireline transceiver using a 36-way time-interleaved SAR ADC and inverter-based RX analog front-end in 7-nm FinFET. IEEE J Solid State Circuits, 2021, 56, 7 doi: 10.1109/JSSC.2020.3024261[50] Kossel M A, Khatri V, Braendli M, et al. An 8b DAC-based SST TX using metal gate resistors with 1.4pJ/b efficiency at 112Gb/s PAM-4 and 8-tap FFE in 7nm CMOS. 2021 IEEE International Solid-State Circuits Conference, 2021, 130[51] Kocaman N, Singh U, Raghavan B, et al. An 182mW 1-60Gb/s configurable PAM-4/NRZ transceiver for large scale ASIC integration in 7nm FinFET technology. 2022 IEEE International Solid-State Circuits Conference, 2022, 120[52] Seual Y, Laufer A, Khairj A, et al. A 1.41 pJ/b 224Gb/s PAM-4 SerDes receiver with 31dB loss compensation. 2022 IEEE International Solid-State Circuits Conference, 2022, 114[53] Kim J, Kundu S, Balankutty A, et al. A 224Gb/s DAC-based PAM-4 transmitter with 8-tap FFE in 10nm CMOS. 2021 IEEE International Solid-State Circuits Conference, 2021, 126[54] Guo Z, Mostafa A, Elshazly A, et al. A 112.5Gb/s ADC-DSP-based PAM-4 long-reach transceiver with >50dB channel loss in 5nm FinFET. 2022 IEEE International Solid-State Circuits Conference, 2022[55] Ye B Y, Sheng K, Gai W X, et al. A 2.29 pJ/b 112Gb/s wireline transceiver with RX 4-tap FFE for medium-reach applications in 28nm CMOS. 2022 IEEE International Solid-State Circuits Conference, 2022, 118[56] Yousry R, Chen E, Ying Y M, et al. A 1.7pJ/b 112Gb/s XSR transceiver for intra-package communication in 7nm FinFET technology. 2021 IEEE International Solid-State Circuits Conference, 2021, 180[57] Li H, Balamurugan G, Sakib M, et al. A 3D-integrated microring-based 112Gb/s PAM-4 silicon-photonic transmitter with integrated nonlinear equalization and thermal control. 2020 IEEE International Solid-State Circuits Conference, 2020[58] Sentieri E, Copani T, Paganini A, et al. A 4-channel 200Gb/s PAM-4 BiCMOS transceiver with silicon photonics front-ends for gigabit Ethernet applications. 2020 IEEE International Solid-State Circuits Conference, 2020, 210[59] Li H, Sharma J, Hsu C M, et al. A 100Gb/s-8.3dBm-sensitivity PAM-4 optical receiver with integrated TIA, FFE and direct-feedback DFE in 28nm CMOS. 2021 IEEE International Solid-State Circuits Conference, 2021, 190[60] Jyo T, Nagatani M, Ozaki J, et al. A 48GHz BW 22mW/ch linear driver IC with stacked current-reuse architecture in 65nm CMOS for beyond-400Gb/s coherent optical transmitters. 2020 IEEE International Solid-State Circuits Conference, 2020, 212[61] Turker D, Bekele A, Upadhyaya P, et al. A 7.4-to-14 GHz PLL with 54fsrms jitter in 16nm FinFET for integrated RF-data-converter SoCs. 2018 IEEE Int Solid State Circuits Conference, 2018, 378[62] Song F, Zhao Y, Wu B, et al. A fractional-N synthesizer with 110fsrms jitter and a reference quadrupler for wideband 802.11ax. 2019 IEEE Int Solid State Circuits Conference, 2019, 264[63] Geng X L, Tian Y B, Xiao Y, et al. A 25.8GHz integer-N PLL with time-amplifying phase-frequency detector achieving 60fsrms jitter, -252.8 dB FoMJ, and robust lock acquisition performance. 2022 IEEE International Solid-State Circuits Conference, 2022, 65, 388[64] Gong J, Charbon E, Sebastiano F, et al. A low-jitter and low-spur charge-sampling PLL. IEEE J Solid State Circuits, 2022, 57, 492 doi: 10.1109/JSSC.2021.3105335[65] Yang Z S, Chen Y, Yang S H, et al. A 25.4-to-29.5GHz 10.2mW isolated sub-sampling PLL achieving -252.9dB jitter-power FoM and -63 dBc reference spur. 2019 IEEE International Solid-State Circuits Conference, 2019, 270[66] Zhang Z, Zhu G, Patrick Yue C. A 0.65-V 12–16-GHz sub-sampling PLL with 56.4-fsrms integrated jitter and –256.4-dB FoM. IEEE J Solid State Circuits, 2020, 55, 1665 doi: 10.1109/JSSC.2020.2967562[67] Lee D G, Mercier P P. A sub-mW 2.4-GHz active-mixer-adopted sub-sampling PLL achieving an FoM of −256 dB. IEEE J Solid-State Circuits, 2020, 55(6), 1542 doi: 10.1109/JSSC.2019.2951377[68] Seol J H, Choo K, Blaauw D, et al. Reference oversampling PLL achieving −256-dB FoM and −78-dBc reference spur. IEEE J Solid State Circuits, 2021, 56, 2993 doi: 10.1109/JSSC.2021.3089930[69] Yang X F, Chan C H, Zhu Y, et al. A -246dB jitter-FoM 2.4GHz calibration-free ring-oscillator PLL achieving 9% jitter variation over PVT. 2019 IEEE International Solid-State Circuits Conference, 2019, 260[70] Wu W H, Yao C W, Guo C K, et al. A 14-nm ultra-low jitter fractional-N PLL using a DTC range reduction technique and a reconfigurable dual-core VCO. IEEE J Solid State Circuits, 2021, 56, 3756 doi: 10.1109/JSSC.2021.3111134[71] Mercandelli M, Santiccioli A, Parisi A, et al. A 12.5-GHz fractional-N type-I sampling PLL achieving 58-fs integrated jitter. IEEE J Solid State Circuits, 2022, 57, 505 doi: 10.1109/JSSC.2021.3123827[72] Thaller E, Levinger R, Shumaker E, et al. A K-band 12.1-to-16.6GHz subsampling ADPLL with 47.3fsrms jitter based on a stochastic flash TDC and coupled dual-core DCO in 16nm FinFET CMOS. 2021 IEEE International Solid-State Circuits Conference, 2021, 64, 451[73] Hwang C, Park H, Seong T, et al. A 188fsrms-jitter -243dB-FoMjitter 5.2GHz-ring-DCO-based fractional-N digital PLL with a 1/8 DTC-range-reduction technique using a quadruple-timing-margin phase selector. 2022 IEEE International Solid-State Circuits Conference, 2022, 378[74] Santiccioli A, Mercandelli M, Bertulessi L, et al. A 66-fs-rms jitter 12.8-to-15.2-GHz fractional-N Bang-bang PLL with digital frequency-error recovery for fast locking. IEEE J Solid State Circuits, 2020, 55, 3349 doi: 10.1109/JSSC.2020.3019344[75] Kim J, Jo Y, Lim Y, et al. A 104fsrms-jitter and-61 dBc-fractional spur 15GHz fractional-N subsampling PLL using a voltage-domain quantization-error cancelation technique. 2021 IEEE International Solid-State Circuits Conference, 2021, 448[76] Dartizio S M, Buccoleri F, Tesolin F, et al. A 68.6fsrms-total-integrated-jitter and 1.56μs-locking-time fractional-N Bang-Bang PLL based on type-II gear shifting and adaptive frequency switching. 2022 IEEE International Solid-State Circuits Conference, 2022, 65, 1[77] Hu Y Z, Chen X, Siriburanon T, et al. A charge-sharing locking technique with a general phase noise theory of injection locking. IEEE J Solid State Circuits, 2021, 57, 518 doi: 10.1109/JSSC.2021.3106237[78] Zhang Z, Yang J C, Liu L Y, et al. An 18–23 GHz 57.4-fs RMS jitter −253.5-dB FoM sub-harmonically injection-locked all-digital PLL with single-ended injection technique and ILFD aided adaptive injection timing alignment technique. IEEE Trans Circuits Syst I, 2019, 66, 3733 doi: 10.1109/TCSI.2019.2911531[79] Xu R J, Ye D W, Li S R, et al. A 0.021mm2 65nm CMOS 2.5GHz digital injection-locked clock multiplier with injection pulse shaping achieving −79 dBc reference spur and 0.496 mW/GHz power efficiency. 2022 IEEE International Solid-State Circuits Conference, 2022, 214[80] Zhang Z. CMOS analog and mixed-signal phase-locked loops: An overview. J Semicond, 2020, 41, 111402 doi: 10.1088/1674-4926/41/11/111402[81] Wang F, Li T W, Wang H. A highly linear super-resolution mixed-signal Doherty power amplifier for high-efficiency mm-wave 5G multi-Gb/s communications. 2019 IEEE International Solid-State Circuits Conference, 2019, 88[82] Ma Z L, Ma K X, Wang K P, et al. A 28GHz compact 3-way transformer-based parallel-series Doherty power amplifier with 20.4%/14.2% PAE at 6-/12-dB power back-off and 25.5dBm PSAT in 55 nm bulk CMOS. 2022 IEEE International Solid-State Circuits Conference, 2022, 320[83] Huang T Y, Mannem N S, Li S S, et al. A 26-to-60 GHz continuous coupler-Doherty linear power amplifier for over-an-octave back-off efficiency enhancement. 2021 IEEE International Solid-State Circuits Conference, 2021, 354[84] Li X C, Chen W H, Li S Y, et al. A 110-to-130GHz SiGe BiCMOS Doherty power amplifier with slotline-based power-combining technique achieving >22dBm saturated output power and >10% power back-off efficiency. 2022 IEEE International Solid-State Circuits Conference, 2022, 316[85] Qunaj V, Reynaert P. A Doherty-like load-modulated balanced power amplifier achieving 15.5dBm average pout and 20% average PAE at a data rate of 18 Gb/s in 28nm CMOS. 2021 IEEE International Solid-State Circuits Conference, 2021, 356[86] Zhu W, Wang J W, Wang R T, et al. A 1V 32.1dBm 92-to-102GHz power amplifier with a scalable 128-to-1 power combiner achieving 15% peak PAE in a 65nm bulk CMOS process. 2022 IEEE International Solid-State Circuits Conference, 2022, 318[87] Xiong L, Li T, Yin Y, et al. A broadband switched-transformer digital power amplifier for deep back-off efficiency enhancement. 2019 IEEE International Solid-State Circuits Conference, 2019, 76[88] Zhang A Y, Chen M S W. A watt-level phase-interleaved multi-subharmonic switching digital power amplifier achieving 31.4% average drain efficiency. 2019 IEEE International Solid-State Circuits Conference, 2019, 74[89] Yang B, Qian H J, Luo X. A Watt-level quadrature switched/floated-capacitor power amplifier with back-off efficiency enhancement in complex domain using reconfigurable self-coupling canceling transformer. 2021 IEEE International Solid-State Circuits Conference, 2021, 64, 362[90] Wang H, Huang T, Mannem N S, et al. Power amplifiers performance survey 2000-present. [Online]. Available: https://gems.ece.gatech.edu/PA_survey.html[91] Iotti L, Mazzanti A, Svelto F. Insights into phase-noise scaling in switch-coupled multi-core LC VCOs for E-band adaptive modulation links. IEEE J Solid State Circuits, 2017, 52, 1703 doi: 10.1109/JSSC.2017.2697442[92] Guo H, Chen Y, Mak P I, et al. A 0.08mm2 25.5-to-29.9 GHz multi-resonant-RLCM-tank VCO using a single-turn multi-tap inductor and CM-only capacitors achieving 191.6dBc/Hz FoM and 130kHz 1/f3 PN corner. 2019 IEEE International Solid-State Circuits Conference, 2019, 410[93] Guo H, Chen Y, Mak P I, et al. A 5.0-to-6.36GHz wideband-harmonic-shaping VCO achieving 196.9dBc/Hz peak FoM and 90-to-180kHz 1/f3 PN corner without harmonic tuning. 2021 IEEE International Solid-State Circuits Conference, 2021, 294[94] Shu Y Y, Qian H J, Gao X, et al. A 3.09-to-4.04GHz distributed-boosting and harmonic-impedance-expanding multi-core oscillator with-138.9dBc/Hz at 1MHz offset and 195.1dBc/Hz FoM. 2021 IEEE International Solid-State Circuits Conference, 2021, 296[95] Jia H K, Deng W, Guan P D, et al. A 60GHz 186.5dBc/Hz FoM quad-core fundamental VCO using circular triple-coupled transformer with no mode ambiguity in 65nm CMOS. 2021 IEEE International Solid-State Circuits Conference, 2021, 1[96] Jia H K, Ma R C, Deng W, et al. A 53.6-to-60.2GHz many-core fundamental oscillator with scalable mesh topology achieving −136.0dBc/Hz phase noise at 10MHz offset and 190.3dBc/Hz peak FoM in 65nm CMOS. 2022 IEEE International Solid-State Circuits Conference, 2022, 154[97] Franceschin A, Riccardi D, Mazzanti A. Series-resonance BiCMOS VCO with phase noise of −138dBc/Hz at 1MHz offset from 10 GHz and −190dBc/Hz FoM. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[98] Bhat A, Krishnapura N. A 25-to-38GHz, 195dB FoMT LC QVCO in 65nm LP CMOS using a 4-port dual-mode resonator for 5G radios. 2019 IEEE International Solid-State Circuits Conference, 2019, 412[99] Shu Y Y, Qian H J, Luo X. A 18.6-to-40.1GHz 201.7dBc/Hz FoMT multi-core oscillator using E-M mixed-coupling resonance boosting. 2020 IEEE International Solid-State Circuits Conference, 2020, 272[100] Gong J, Patra B, Enthoven L, et al. A 0.049mm2 7.1-to-16.8GHz dual-core triple-mode VCO achieving 200dB FoMA in 22nm FinFET. 2022 IEEE International Solid-State Circuits Conference, 2022, 152[101] Lei K M, Mak P I, Martins R P. Startup time and energy-reduction techniques for crystal oscillators in the IoT era. IEEE Trans Circuits Syst II, 2021, 68, 30 doi: 10.1109/TCSII.2020.3040419[102] Iguchi S, Fuketa H, Sakurai T, et al. Variation-tolerant quick-start-up CMOS crystal oscillator with chirp injection and negative resistance booster. IEEE J Solid State Circuits, 2016, 51, 496 doi: 10.1109/JSSC.2015.2499240[103] Ding M, Liu Y H, Zhang Y, et al. A 95µW 24MHz digitally controlled crystal oscillator for IoT applications with 36 nJ start-up energy and >13× start-up time reduction using a fully-autonomous dynamically-adjusted load. 2017 IEEE International Solid-State Circuits Conference, 2017, 90[104] Lei K M, Mak P I, Martins R P. A 0.4V 4.8μW 16MHz CMOS crystal oscillator achieving 74-fold startup-time reduction using momentary detuning. 2017 IEEE International Symposium on Circuits and Systems, 2017, 1[105] Lei K M, Mak P I, Law M K, et al. A regulation-free sub-0.5V 16/24MHz crystal oscillator for energy-harvesting BLE radios with 14.2nJ startup energy and 31.8pW steady-state power. 2018 IEEE International Solid-State Circuits Conference, 2018, 52[106] Miyahara M, Endo Y, Okada K, et al. A 64μs start-up 26/40MHz crystal oscillator with negative resistance boosting technique using reconfigurable multi-stage amplifier. 2018 IEEE Symposium on VLSI Circuits, 2018, 115[107] Lei K M, Mak P I, Law M K, et al. A regulation-free sub-0.5-V 16-/24-MHz crystal oscillator with 14.2-nJ startup energy and 31.8-μW steady-state power. IEEE J Solid State Circuits, 2018, 53, 2624 doi: 10.1109/JSSC.2018.2849012[108] Ding M, Liu Y H, Harpe P, et al. A low-power fast start-up crystal oscillator with an autonomous dynamically adjusted load. IEEE Trans Circuits Syst I, 2019, 66, 1382 doi: 10.1109/TCSI.2018.2880282[109] Abdelatty O, Bishop H, Shi Y, et al. A low power bluetooth low-energy transmitter with a 10.5nJ startup-energy crystal oscillator. ESSCIRC 2019 IEEE 45th Eur Solid State Circuits Conference, 2019, 377[110] Scholl M, Saalfeld T, Beyerstedt C, et al. A 32MHz crystal oscillator with fast start-up using dithered injection and negative resistance boost. 2019 IEEE 45th Eur Solid State Circuits Conference, 2019, 49[111] Wang X, Mercier P. An 11.1nJ-start-up 16/20MHz crystal oscillator with multi-path feedforward negative resistance boosting and optional dynamic pulse width injection. IEEE Custom Integrated Circuits Conference, 2020[112] Griffith D, Murdock J, Røine P T. A 24MHz crystal oscillator with robust fast start-up using dithered injection. 2016 IEEE International Solid-State Circuits Conference, 2016, 104[113] Esmaeelzadeh H, Pamarti S. A quick startup technique for high-Q oscillators using precisely timed energy injection. IEEE J Solid State Circuits, 2018, 53, 692 doi: 10.1109/JSSC.2017.2766208[114] Verhoef B, Prummel J, Kruiskamp W, et al. A 32MHz crystal oscillator with fast start-up using synchronized signal injection. 2019 IEEE International Solid-State Circuits Conference, 2019, 304[115] Megawer K M, Pal N, Elkholy A, et al. A 54MHz crystal oscillator with 30 × start-up time reduction using 2-step injection in 65nm CMOS. 2019 IEEE International Solid-State Circuits Conference, 2019, 302[116] Lechevallier J B, van der Zee R A R, Nauta B. Fast & energy efficient start-up of crystal oscillators by self-timed energy injection. IEEE J Solid State Circuits, 2019, 54, 3107 doi: 10.1109/JSSC.2019.2933143[117] Karimi-Bidhendi A, Heydari P. A study of multi-phase injection on accelerating crystal oscillator start-up. IEEE Trans Circuits Syst II, 2020, 67, 2868 doi: 10.1109/TCSII.2020.2978097[118] Lechevallier J B, Bindra H S, van der Zee R A R, et al. Energy efficient startup of crystal oscillators using stepwise charging. IEEE J Solid State Circuits, 2021, 56, 2427 doi: 10.1109/JSSC.2021.3061032[119] Jung J, Oh S, Kim J, et al. A single-crystal-oscillator-based clock-management IC with 18× start-up time reduction and 0.68ppm/ºC duty-cycled machine-learning-based RCO calibration. 2022 IEEE International Solid-State Circuits Conference, 2022, 58[120] Luo H, Kundu S, Huusari T, et al. A fast startup crystal oscillator using impedance guided chirp injection in 22nm FinFET CMOS. IEEE J Solid State Circuits, 2022, 57, 688 doi: 10.1109/JSSC.2021.3136237[121] Lei K M, Mak P I, Martins R P. A 0.35-V 5,200-μm2 2.1-MHz temperature-resilient relaxation oscillator with 667fJ/cycle energy efficiency using an asymmetric swing-boosted RC network and a dual-path comparator. IEEE J Solid State Circuits, 2021, 56, 2701 doi: 10.1109/JSSC.2021.3067051[122] Ji Y, Liao J W, Arjmandpour S, et al. A second-order temperature-compensated on-chip R-RC oscillator achieving 7.93ppm/°C and 3.3pJ/Hz in −40°C to 125°C temperature range. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[123] Murmann B. ADC Performance survey 1997–2021. [Online] Available: http://web.stanford.edu/~murmann/adcsurvey.html[124] Jie L, Tang X Y, Liu J X, et al. An overview of noise-shaping SAR ADC: From fundamentals to the frontier. IEEE Open J Solid State Circuits Soc, 2021, 1, 149 doi: 10.1109/OJSSCS.2021.3119910[125] Fredenburg J A, Flynn M P. A 90-MS/s 11-MHz-bandwidth 62-dB SNDR noise-shaping SAR ADC. IEEE J Solid State Circuits, 2012, 47, 2898 doi: 10.1109/JSSC.2012.2217874[126] Li S L, Qiao B, Gandara M, et al. A 13-ENOB second-order noise-shaping SAR ADC realizing optimized NTF zeros using the error-feedback structure. IEEE J Solid State Circuits, 2018, 53, 3484 doi: 10.1109/JSSC.2018.2871081[127] Guo W J, Zhuang H Y, Sun N. A 13b-ENOB 173dB-FOM 2nd-order NS SAR ADC with passive integrators. 2017 Symposium on VLSI Circuits, 2017, C236[128] Lin Y Z, Lin C, Tsou S C, et al. A 40MHz-BW 320MS/s passive noise-shaping SAR ADC with passive signal-residue summation in 14nm FinFET. 2019 IEEE International Solid-State Circuits Conference, 2019, 330[129] Liu J X, Li D Q, Zhong Y, et al. A 250kHz-BW 93dB-SNDR 4th-order noise-shaping SAR using capacitor stacking and dynamic buffering. 2021 IEEE International Solid-State Circuits Conference, 2021, 369[130] Liu C C, Huang M C. A 0.46mW 5MHz-BW 79.7dB-SNDR noise-shaping SAR ADC with dynamic-amplifier-based FIR-IIR filter. 2017 IEEE International Solid-State Circuits Conference, 2017, 466[131] Jie L, Zheng B Y, Chen H W, et al. A cascaded noise-shaping SAR architecture for robust order extension. IEEE J Solid State Circuits, 2020, 55, 3236 doi: 10.1109/JSSC.2020.3019487[132] Tang X Y, Yang X X, Zhao W D, et al. A 13.5-ENOB, 107-μW noise-shaping SAR ADC with PVT-robust closed-loop dynamic amplifier. IEEE J Solid State Circuits, 2020, 55, 3248 doi: 10.1109/JSSC.2020.3020194[133] Shu Y S, Kuo L T, Lo T Y. An oversampling SAR ADC with dac mismatch error shaping achieving 105 dB SFDR and 101 dB SFDR over 1 kHz BW in 55 nm cmos. IEEE J Solid State Circuits, 2016, 51, 2928 doi: 10.1109/JSSC.2016.2592623[134] Nan S. High-order mismatch-shaping in multibit DACs. IEEE Trans Circuits Syst II, 2011, 58, 346 doi: 10.1109/TCSII.2011.2158163[135] Liu J X, Wang X, Gao Z J, et al. A 40kHz-BW 90dB-SNDR noise-shaping SAR with 4 × passive gain and 2nd-order mismatch error shaping. 2020 IEEE International Solid-State Circuits Conference, 2020, 158[136] Shen Y T, Li H Y, Xin H M, et al. A 103-dB SFDR calibration-free oversampled SAR ADC with mismatch error shaping and pre-comparison techniques. IEEE J Solid State Circuits, 2022, 57, 734 doi: 10.1109/JSSC.2021.3135559[137] Lee K, Chae J, Aniya M, et al. A noise-coupled time-interleaved delta-sigma ADC with 4.2 MHz bandwidth, −98 dB THD, and 79 dB SNDR. IEEE J Solid State Circuits, 2008, 43, 2601 doi: 10.1109/JSSC.2008.2006311[138] Jie L, Zheng B Y, Flynn M P. A calibration-free time-interleaved fourth-order noise-shaping SAR ADC. IEEE J Solid State Circuits, 2019, 54, 3386 doi: 10.1109/JSSC.2019.2938626[139] Zhuang H Y, Liu J X, Sun N. A fully-dynamic time-interleaved noise-shaping SAR ADC based on CIFF architecture. 2020 IEEE Custom Integrated Circuits Conference, 2020, 1[140] Lin C, Lin Y Z, Tsai C H, et al. An 80MHz-BW 640MS/s time-interleaved passive noise-shaping SAR ADC in 22nm FDSOI process. 2021 IEEE International Solid-State Circuits Conference, 2021, 378[141] Kapusta R, Zhu H Y, Lyden C. Sampling circuits that break the kT/C thermal noise limit. IEEE J Solid State Circuits, 2014, 49, 1694 doi: 10.1109/JSSC.2014.2320465[142] Li Z L, Dutta A, Mukherjee A, et al. A SAR ADC with reduced kT/C noise by decoupling noise PSD and BW. 2020 IEEE Symposium on VLSI Circuits, 2020, 1[143] Wang T H, Wu R W, Gupta V, et al. A 13.8-ENOB 0.4pF-CIN 3rd-order noise-shaping SAR in a single-amplifier EF-CIFF structure with fully dynamic hardware-reusing kT/C noise cancelation. 2021 IEEE International Solid-State Circuits Conference, 2021, 374[144] Jie L, Chen H W, Zheng B Y, et al. A 100MHz-BW 68dB-SNDR tuning-free hybrid-loop DSM with an interleaved bandpass noise-shaping SAR quantizer. 2021 IEEE International Solid-State Circuits Conference, 2021, 167[145] Nam J W, Hassanpourghadi M, Zhang A Y, et al. A 12-bit 1.6, 3.2, and 6.4 GS/s 4-b/cycle time-interleaved SAR ADC with dual reference shifting and interpolation. IEEE J Solid State Circuits, 2018, 53, 1765 doi: 10.1109/JSSC.2018.2808244[146] Jiang T, Liu W, Zhong F Y, et al. A single-channel, 1.25-GS/s, 6-bit, 6.08-mW asynchronous successive-approximation ADC with improved feedback delay in 40-nm CMOS. IEEE J Solid State Circuits, 2012, 47, 2444 doi: 10.1109/JSSC.2012.2204543[147] Song Y, Zhu Y, Chan C H, et al. A 77dB SNDR 12.5MHz bandwidth 0–1 MASH ΣΔ ADC based on the pipelined-SAR structure. 2018 IEEE Symposium on VLSI Circuits, 2018, 203[148] Liu J X, Li S L, Guo W J, et al. A 0.029mm2 17-FJ/conv.-step CT ΔΣ ADC with 2nd-order noise-shaping SAR quantizer. 2018 IEEE Symposium on VLSI Circuits, 2018, 201[149] Shi W, Liu J X, Mukherjee A, et al. A 3.7mW 12.5MHz 81dB-SNDR 4th-order CTDSM with single-OTA and 2nd-order NS-SAR. 2021 IEEE International Solid-State Circuits Conference, 2021, 170[150] Vogelmann P, Haas M, Ortmanns M. A 1.1mW 200kS/s incremental ΔΣ ADC with a DR of 91.5dB using integrator slicing for dynamic power reduction. 2018 IEEE International Solid-State Circuits Conference, 2018, 236[151] Mohamad S, Yuan J, Bermak A. A 102.2-DB, 181.1-dB FoM extended counting analog-to-digital converter with capacitor scaling. IEEE J Solid State Circuits, 2020, 55, 1351 doi: 10.1109/JSSC.2019.2950180[152] Wang B, Sin S W, Seng-Pan U, et al. A 550-μW 20-kHz BW 100.8-dB SNDR linear- exponential multi-bit incremental sigma-delta ADC with 256 clock cycles in 65-nm CMOS. IEEE J Solid State Circuits, 2019, 54, 1161 doi: 10.1109/JSSC.2018.2888872[153] Zhang Y, Chen C H, He T, et al. A 16 b multi-step incremental analog-to-digital converter with single-opamp multi-slope extended counting. IEEE J Solid State Circuits, 2017, 52, 1066 doi: 10.1109/JSSC.2016.2641466[154] Chae Y, Souri K, Makinwa K A A. A 6.3µW 20b incremental zoom-ADC with 6ppm INL and 1µV offset. 2013 IEEE International Solid-State Circuits Conference, 2013, 276[155] Liu Y Y, Zhao M L, Zhao Y B, et al. A 4.96μW 15b self-timed dynamic-amplifier-based incremental zoom ADC. 2022 IEEE International Solid-State Circuits Conference, 2022, 170[156] Jie L, Zhan M T, Tang X Y, et al. A 0.014mm2 10kHz-BW zoom-incremental-counting ADC achieving 103dB SNDR and 100dB full-scale CMRR. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[157] Mokhtar M A, Vogelmann P, Haas M, et al. A 94.3-dB SFDR, 91.5-dB DR, and 200-kS/s CT incremental delta–sigma modulator with differentially reset FIR feedback. ESSCIRC 2019 - IEEE 45th European Solid State Circuits Conference, 2019, 87[158] Wu S H, Shu Y S, Chiou A Y C, et al. A current-sensing front-end realized by A continuous-time incremental ADC with 12b SAR quantizer and reset-then-open resistive DAC achieving 140dB DR and 8ppm INL at 4kS/s. 2020 IEEE International Solid-State Circuits Conference, 2020, 154[159] Mokhtar M A, Abdelaal A, Sporer M, et al. A 0.9-V calibration-free 97dB-SFDR 2-MS/s continuous time incremental delta-sigma ADC utilizing variable bit width quantizer in 28 nm CMOS. 2021 IEEE Custom Integrated Circuits Conference, 2021, 1[160] Qi L, Jain A, Jiang D Y, et al. A 76.6-dB-SNDR 50-MHz-BW 29.2-mW multi-bit CT sturdy MASH with DAC non-linearity tolerance. IEEE J Solid State Circuits, 2020, 55, 344 doi: 10.1109/JSSC.2019.2942359[161] Vogelmann P, Luo Y, Mokhtar M A, et al. Efficient high-resolution nyquist ADCs. In: Next-Generation ADCs, High-Performance Power Management, and Technology Considerations for Advanced Integrated Circuits. Cham: Springer International Publishing, 2019, 41[162] Severin J A. High-speed analog-to-digital conversion. Amsterdam: Elsevier, 1991[163] Hershberg B, Dermit D, van Liempd B, et al. A 3.2GS/s 10ENOB 61mW ringamp ADC in 16nm with background monitoring of distortion. 2019 IEEE International Solid-State Circuits Conference, 2019, 58[164] Devarajan S, Singer L, Kelly D, et al. A 12b 10GS/s interleaved pipeline ADC in 28nm CMOS technology. 2017 IEEE International Solid-State Circuits Conference, 2017, 288[165] Ali A M A, Dinc H, Bhoraskar P, et al. A 12b 18GS/s RF sampling ADC with an integrated wideband track-and-hold amplifier and background calibration. 2020 IEEE International Solid-State Circuits Conference, 2020, 250[166] Zheng Z H, Wei L, Lagos J, et al. A single-channel 5.5mW 3.3GS/s 6b fully dynamic pipelined ADC with post-amplification residue generation. 2020 IEEE International Solid-State Circuits Conference, 2020, 254[167] Shibata H, Kozlov V, Ji Z X, et al. A 9GS/s 1GHz-BW oversampled continuous-time pipeline ADC achieving −161 dBFS/Hz NSD. 2017 IEEE International Solid-State Circuits Conference, 2017, 278[168] Shibata H, Taylor G, Schell B, et al. An 800MHz-BW VCO-based continuous-time pipelined ADC with inherent anti-aliasing and on-chip digital reconstruction filter. 2020 IEEE International Solid-State Circuits Conference, 2020, 260[169] Jiang W N, Zhu Y, Zhang M L, et al. A 7.6mW 1GS/s 60dB SNDR single-channel SAR-assisted pipelined ADC with temperature-compensated dynamic gm-R-based amplifier. 2019 IEEE International Solid-State Circuits Conference, 2019, 60[170] ElShater A, Lee C Y, Venkatachala P K, et al. A 10mW 16b 15MS/s two-step SAR ADC with 95dB DR using dual-deadzone ring-amplifier. 2019 IEEE International Solid-State Circuits Conference, 2019, 70[171] Hung T C, Wang J C, Kuo T H. A calibration-free 71.7dB SNDR 100MS/s 0.7mW weighted-averaging correlated level shifting pipelined SAR ADC with speed-enhancement scheme. 2020 IEEE International Solid-State Circuits Conference, 2020, 256[172] Wang J C, Kuo T H. A 0.82mW 14b 130MS/S pipelined-SAR ADC with a distributed averaging correlated level shifting (DACLS) ringamp and bypass-window backend. 2022 IEEE International Solid-State Circuits Conference, 2022, 162[173] Tang X Y, Yang X X, Liu J X, et al. A 0.4-to-40 MS/s 75.7 dB-SNDR fully dynamic event-driven pipelined ADC with 3-stage cascoded floating inverter amplifier. 2021 IEEE International Solid-State Circuits Conference, 2021, 376[174] Zhang M L, Chan C H, Zhu Y, et al. A 0.6V 13b 20MS/s two-step TDC-assisted SAR ADC with PVT tracking and speed-enhanced techniques. 2019 IEEE International Solid-State Circuits Conference, 2019, 66[175] Zhao H Y, Dai F F. A 0.97mW 260MS/s 12b pipelined-SAR ADC with ring-TDC-based fine quantizer for PVT robust automatic cross-domain scale alignment. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[176] Song Y, Zhu Y, Chan C H, et al. A 2.56mW 40MHz-bandwidth 75dB-SNDR partial-interleaving SAR-assisted NS pipeline ADC with background inter-stage offset calibration. 2020 IEEE International Solid-State Circuits Conference, 2020, 164[177] Baek S, Jang I, Choi M, et al. A 12b 600MS/s pipelined SAR and 2x-interleaved incremental delta-sigma ADC with source-follower-based residue-transfer scheme in 7nm FinFET. 2021 IEEE International Solid-State Circuits Conference, 2021, 172[178] Zhang H S, Zhu Y, Chan C H, et al. A 25MHz-BW 75dB-SNDR inherent gain error tolerance noise-shaping SAR-assisted pipeline ADC with background offset calibration. 2021 IEEE International Solid-State Circuits Conference, 2021, 380[179] Shen L X, Shen Y, Tang X Y, et al. A 0.01mm2 25µW 2MS/s 74dB-SNDR continuous-time pipelined-SAR ADC with 120fF input capacitor. 2019 IEEE International Solid-State Circuits Conference, 2019, 64[180] Zhan M T, Jie L, Tang X Y, et al. A 0.004mm2 200MS/S pipelined SAR ADC with kT/C noise cancellation and robust ring-amp. 2022 IEEE International Solid-State Circuits Conference, 2022, 164[181] Zhang M L, Zhu Y, Chan C H, et al. A 4× interleaved 10GS/s 8b time-domain ADC with 16 × interpolation-based inter-stage gain achieving >37.5dB SNDR at 18GHz input. 2020 IEEE International Solid-State Circuits Conference, 2020, 252[182] Liu J Z, Hassanpourghadi M, Chen M S W. A 10GS/s 8b 25fJ/c-s 2850μm2 two-step time-domain ADC using delay-tracking pipelined-SAR TDC with 500fs time step in 14nm CMOS technology. 2022 IEEE International Solid-State Circuits Conference, 2022, 160[183] Schaef C, Weng S, Choi B, et al. A 93.8% peak efficiency, 5V-input, 10A max ILOAD flying capacitor multilevel converter in 22nm CMOS featuring wide output voltage range and flying capacitor precharging. 2019 IEEE International Solid-State Circuits Conference, 2019, 146[184] Amin S S, Mercier P P. A fully integrated Li-ion-compatible hybrid four-level DC-DC converter in 28-nm FDSOI. IEEE J Solid State Circuits, 2019, 54, 720 doi: 10.1109/JSSC.2018.2880183[185] Abdulslam A, Mercier P P. A symmetric modified multilevel ladder PMIC for battery-connected applications. IEEE J Solid State Circuits, 2020, 55, 767 doi: 10.1109/JSSC.2019.2957658[186] Xia Z Y, Stauth J. A two-stage cascaded hybrid switched-capacitor DC-DC converter with 96.9% peak efficiency tolerating 0.6V/μs input slew rate during startup. 2021 IEEE International Solid-State Circuits Conference, 2021, 256[187] Liu W C, Ng P H, Pilawa-Podgurski R. A three-level boost converter with full-range auto-capacitor-compensation pulse frequency modulation. IEEE J Solid State Circuits, 2020, 55, 744 doi: 10.1109/JSSC.2019.2959509[188] Baek J, Nomiyama T, Park S, et al. A voltage-tolerant three-level buck-boost DC-DC converter with continuous transfer current and flying capacitor soft charger achieving 96.8% power efficiency and 0.87µs/V DVS rate. 2020 IEEE International Solid-State Circuits Conference, 2020, 202[189] Choi M, Jeong D K. A 92.8%-peak-efficiency 60A 48V-to-1V 3-level half-bridge DC-DC converter with balanced voltage on a flying capacitor. 2020 IEEE International Solid-State Circuits Conference, 2020, 296[190] Assem P, Liu W C, Lei Y T, et al. Hybrid dickson switched-capacitor converter with wide conversion ratio in 65-nm CMOS. IEEE J Solid State Circuits, 2020, 55, 2513 doi: 10.1109/JSSC.2020.3004256[191] Ashourloo M, Namburi V R, Piqué G V, et al. A masterless fault-tolerant hybrid dickson converter with 95.3% peak efficiency 20V-to-60V input and 3.3V output for 48V multi-phase automotive applications. 2021 IEEE International Solid-State Circuits Conference, 2021, 258[192] Yamauchi Y, Sai T, Hata K, et al. 0.55 W, 88%, 78 kHz, 48 V-to-5 V fibonacci hybrid DC–DC converter IC using 66 mm3 of passive components with automatic change of converter topology and duty ratio for cold-crank transient. IEEE Trans Power Electron, 2021, 36, 9273 doi: 10.1109/TPEL.2021.3058207[193] Yang X, Zhao L H, Zhao M L, et al. A 5V input 98.4% peak efficiency reconfigurable capacitive-sigma converter with greater than 90% peak efficiency for the entire 0.4~1.2V output range. 2022 IEEE International Solid-State Circuits Conference, 2022, 108[194] Abdulslam A, Mercier P P. A continuous-input-current passive-stacked third-order buck converter achieving 0.7W/mm2 power density and 94% peak efficiency. 2019 IEEE International Solid-State Circuits Conference, 2019, 148[195] Abdulslam A, Mercier P P. A 98.2%-efficiency reciprocal direct charge recycling inductor-first DC-DC converter. 2021 IEEE International Solid-State Circuits Conference, 2021, 264[196] Abdulslam A, Mercier P P. A battery-connected inductor-first flying capacitor multilevel converter achieving 0.77W/mm2 and 97.1% peak efficiency. 2021 IEEE Custom Integrated Circuits Conference, 2021, 1[197] Hardy C, Le H P. A 10.9W 93.4%-efficient (27W 97%-efficient) flying-inductor hybrid DC-DC converter suitable for 1-cell (2-cell) battery charging applications. 2019 IEEE International Solid-State Circuits Conference, 2019, 150[198] Tang N, Nguyen B, Tang Y Y, et al. Fully integrated buck converter with 78% efficiency at 365mW output power enabled by switched-inductor capacitor topology and inductor current reduction technique. 2019 IEEE International Solid-State Circuits Conference, 2019, 152[199] Huh Y, Hong S W, Cho G H. A hybrid structure dual-path step-down converter with 96.2% peak efficiency using 250-mΩ large-DCR inductor. IEEE J Solid State Circuits, 2019, 54, 959 doi: 10.1109/JSSC.2018.2882526[200] Ko J Y, Huh Y, Ko M W, et al. A 4.5V-input 0.3-to-1.7V-output step-down always-dual-path DC-DC converter achieving 91.5%-efficiency with 250mΩ-DCR inductor for low-voltage SoCs. 2021 Symposium on VLSI Circuits, 2021, 1[201] Cai G G, Lu Y, Martins R. A battery-input sub-1V output 92.9% peak efficiency 0.3A/mm2 current density hybrid SC-parallel-inductor buck converter with reduced inductor current in 65nm CMOS. 2022 IEEE International Solid-State Circuits Conference, 2022, 312[202] Zhen S, Yang R, Wu D, et al. Design of hybrid dual-path DC-DC converter with wide input voltage efficiency improvement. 2021 IEEE International Symposium on Circuits and Systems, 2021, 1[203] Hata K, Yamauchi Y, Sai T, et al. 48V-to-12V dual-path hybrid DC-DC converter. 2020 IEEE Applied Power Electronics Conference and Exposition, 2020, 2279[204] Yan D, Ke X G, Ma D B. Direct 48-/ 1-V GaN-based DC–DC power converter with double step-down architecture and master–slave AO2T control. IEEE J Solid State Circuits, 2020, 55, 988 doi: 10.1109/JSSC.2019.2957237[205] Wei K, Ramadass Y, Ma D B. Direct 12 V/24 V-to-1 V tri-state double step-down power converter with online VCF rebalancing and in situ precharge rate regulation. IEEE J Solid State Circuits, 2021, 56, 2416 doi: 10.1109/JSSC.2021.3053457[206] Hu T X, Huang M, Lu Y, et al. A 4A 12-to-1 flying capacitor cross-connected DC-DC converter with inserted D>0.5 control achieving >2× transient inductor current slew rate and 0.73× theoretical minimum output undershoot of DSD. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[207] Cao H X, Yang X, Xue C K, et al. A 12-level series-capacitor 48-1 V DC–DC converter with on-chip switch and GaN hybrid power conversion. IEEE J Solid State Circuits, 2021, 56, 3628 doi: 10.1109/JSSC.2021.3104328[208] Cheng L, Tang K, Ki W H, et al. Fast-transient techniques for high-frequency DC–DC converters. J Semicond, 2020, 41, 112402 doi: 10.1088/1674-4926/41/11/112402[209] Wei K, Ma D B. A 10-MHz DAB hysteretic control switching power converter for 5G IoT power delivery. IEEE J Solid State Circuits, 2021, 56, 2113 doi: 10.1109/JSSC.2020.3042755[210] Kuo T H, Huang Y W, Wang P Y. Background capacitor-current-sensor calibration of DC-DC buck converter with DVS for accurately accelerating load-transient response. 2019 IEEE International Solid-State Circuits Conference, 2019, 430[211] Choi M, Kye C H, Oh J, et al. A synthesizable digital AOT 4-phase buck voltage regulator for digital systems with 0.0054mm2 controller and 80 ns recovery time. 2019 IEEE International Solid-State Circuits Conference, 2019, 432[212] Lee B, Song M K, Maity A, et al. A 25-MHz four-phase SAW hysteretic control DC–DC converter with 1-cycle active phase count. IEEE J Solid State Circuits, 2019, 54, 1755 doi: 10.1109/JSSC.2019.2895240[213] Cho J H, Kim D K, Bae H H, et al. A 1.23W/mm 83.7%-efficiency 400MHz 6-phase fully integrated buck converter in 28nm CMOS with on-chip capacitor dynamic re-allocation for inter-inductor current balancing and fast DVS of 75mV/ns. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[214] Schaef C, Salus T, Rayess R, et al. A Imax, fully integrated multi-phase voltage regulator with 91.5% peak efficiency at 1.8 to 1V, operating at 50MHz and featuring a digitally assisted controller with automatic phase shedding and soft switching in 4nm class FinFET CMOS. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[215] Yuan J Y, Liu Z G, Wu F, et al. A 12V/24V-to-1V DSD power converter with 56mV droop and 0.9μs 1% settling time for a 3A/20ns load transient. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[216] Huang M, Lu Y, Hu T X, et al. A hybrid boost converter with cross-connected flying capacitors. IEEE J Solid State Circuits, 2021, 56, 2102 doi: 10.1109/JSSC.2020.3044062[217] Nishijima K, Harada K, Nakano T, et al. Analysis of double step-down two-phase buck converter for VRM. INTELEC 05 - Twenty-Seventh International Telecommunications Conference, 2005, 497[218] Chen L, Sankman J, Mukhopadhyay R, et al. A 50.7% peak efficiency subharmonic resonant isolated capacitive power transfer system with 62mW output power for low-power industrial sensor interfaces. 2017 IEEE International Solid-State Circuits Conference, 2017, 428[219] Tang J, Zhao L, Huang C. A 68.3% efficiency reconfigurable 400-/800-mW capacitive isolated DC-DC converter with common-mode transient immunity and fast dynamic response by through-powerlink hysteretic control. IEEE International Solid-State Circuits Conference, 2022, 242[220] Lombardo P, Fiore V, Ragonese E, et al. A fully-integrated half-duplex data/power transfer system with up to 40Mb/s data rate, 23mW output power and on-chip 5kV galvanic isolation. 2016 IEEE International Solid-State Circuits Conference, 2016, 300[221] Ragonese E, Spina N, Castorina A, et al. A fully integrated galvanically isolated DC-DC converter with data communication. IEEE Trans Circuits Syst I, 2018, 65, 1432 doi: 10.1109/TCSI.2017.2742021[222] Fiore V, Ragonese E, Palmisano G. A fully integrated Watt-level power transfer system with on-chip galvanic isolation in silicon technology. IEEE Trans Power Electron, 2017, 32, 1984 doi: 10.1109/TPEL.2016.2556939[223] Qin W H, Yang X, Ma S Y, et al. An 800mW fully integrated galvanic isolated power transfer system meeting CISPR 22 class-B emission levels with 6dB margin. 2019 IEEE International Solid-State Circuits Conference, 2019, 246[224] Zhuo Y, Ma S Y, Zhao T T, et al. A 52% peak-efficiency >1W isolated power transfer system using fully integrated magnetic-core transformer. 2019 IEEE International Solid-State Circuits Conference, 2019, 244[225] Li L S, Fang X M, Wu R X. An 11MHz fully integrated 5kV isolated DC-DC converter without cross-isolation-barrier feedback. 2020 IEEE International Solid-State Circuits Conference, 2020, 292[226] Pan D F, Li G L, Miao F T, et al. A 1.25W 46.5%-peak-efficiency transformer-in-package isolated DC-DC converter using glass-based fan-out wafer-level packaging achieving 50mW/mm2 power density. 2021 IEEE International Solid-State Circuits Conference, 2021, 468[227] Pan D F, Li G L, Miao F T, et al. A 1.2W 51%-peak-efficiency isolated DC-DC converter with a cross-coupled shoot-through-free class-D oscillator meeting the CISPR-32 class-B EMI standard. 2022 IEEE International Solid-State Circuits Conference, 2022, 240[228] Analog Devices, AN-0971. Recommendations for Control of Radiated Emissions with isoPower Devices. Rev. C, Accessed on Jan. 1, 2014, https://www.analog.com/media/en/technical-documentation/application-notes/AN-0971.pdf[229] Ho C Y, Lin S M, Meng C H, et al. An 87.1% efficiency RF-PA envelope-tracking modulator for 80MHz LTE-Advanced transmitter and 31dBm PA output power for HPUE in 0.153μm CMOS. 2018 IEEE International Solid-State Circuits Conference, 2018, 432[230] Paek J S, Kim D, Bang J S, et al. An 88%-efficiency supply modulator achieving 1.08μs/V fast transition and 100MHz envelope-tracking bandwidth for 5G new radio RF power amplifier. 2019 IEEE International Solid-State Circuits Conference, 2019, 238[231] Nomiyama T, Youn Y, Choo Y, et al. A 2TX supply modulator for envelope-tracking power amplifier supporting intra- and inter-band uplink carrier aggregation and power class-2 high-power user equipment. 2018 IEEE International Solid-State Circuits Conference, 2018, 434[232] Mahmoudidaryan P, Mandal D, Bakkaloglu B, et al. Wideband hybrid envelope tracking modulator with hysteretic-controlled three-level switching converter and slew-rate enhanced linear amplifier. IEEE J Solid State Circuits, 2019, 54, 3336 doi: 10.1109/JSSC.2019.2941014[233] Mahmoudidaryan P, Mandal D, Bakkaloglu B, et al. A 91%-efficiency envelope-tracking modulator using hysteresis-controlled three-level switching regulator and slew-rate-enhanced linear amplifier for LTE-80 MHz applications. 2019 IEEE International Solid-State Circuits Conference, 2019, 428[234] Liu X, Zhang H, Mok P K T, et al. A multi-loop-controlled AC-coupling supply modulator with a mode-switching CMOS PA in an EER system with envelope shaping. IEEE J Solid State Circuits, 2019, 54, 1553 doi: 10.1109/JSSC.2019.2892555[235] Liu X, Zhang H, Zhao M, et al. A 2.4V 23.9dBm 35.7%-PAE-32.1dBc-ACLR LTE-20MHz envelope-shaping-and-tracking system with a multiloop-controlled AC-coupling supply modulator and a mode-switching PA. 2017 IEEE International Solid-State Circuits Conference, 2017, 38[236] Baek J, Nomiyama T, Park S, et al. A voltage-tolerant three-level buck-boost DC-DC converter with continuous transfer current and flying capacitor soft charger achieving 96.8% power efficiency and 0.87µs/V DVS rate. 2020 IEEE International Solid-State Circuits Conference, 2020, 202[237] Kim D, Bang J S, Baek J, et al. A hybrid switching supply modulator achieving 130MHz envelope-tracking bandwidth and 10W output power for 2G/3G/LTE/NR RF power amplifiers. 2021 IEEE International Solid-State Circuits Conference, 2021, 476[238] Bang J S, Kim D, Lee J, et al. 2-Tx digital envelope-tracking supply modulator achieving 200MHz channel bandwidth and 93.6% efficiency for 2G/3G/LTE/NR RF power amplifiers. 2022 IEEE International Solid-State Circuits Conference, 2022, 1[239] Lichtsteiner P, Posch C, Delbruck T. A 128×128 120 dB 15 μs latency asynchronous temporal contrast vision sensor. IEEE J Solid State Circuits, 2008, 43, 566 doi: 10.1109/JSSC.2007.914337[240] Yang M H, Liu S C, Delbruck T. A dynamic vision sensor with 1% temporal contrast sensitivity and in-pixel asynchronous delta modulator for event encoding. IEEE J Solid State Circuits, 2015, 50, 2149 doi: 10.1109/JSSC.2015.2425886[241] Son B, Suh Y, Kim S, et al. A 640×480 dynamic vision sensor with a 9µm pixel and 300Meps address-event representation. 2017 IEEE International Solid-State Circuits Conference, 2017, 66[242] Suh Y, Choi S, Ito M, et al. A 1280×960 dynamic vision sensor with a 4.95-μm pixel pitch and motion artifact minimization. 2020 IEEE International Symposium on Circuits and Systems, 2020, 1[243] Finateu T, Niwa A, Matolin D, et al. A 1280×720 back-illuminated stacked temporal contrast event-based vision sensor with 4.86µm pixels, 1.066GEPS readout, programmable event-rate controller and compressive data-formatting pipeline. 2020 IEEE International Solid-State Circuits Conference, 2020, 112[244] Li C H, Longinotti L, Corradi F, et al. A 132 by 104 10μm-Pixel 250μW 1kefps dynamic vision sensor with pixel-parallel noise and spatial redundancy suppression. 2019 Symposium on VLSI Circuits, 2019, C216[245] Akrarai M, Margotat N, Sicard G, et al. A novel event based image sensor with spacial and temporal redundancy suppression. 2020 18th IEEE International New Circuits and Systems Conference, 2020, 238[246] Brandli C, Berner R, Yang M H, et al. A 240 × 180 130 dB 3 µs latency global shutter spatiotemporal vision sensor. IEEE J Solid State Circuits, 2014, 49, 2333 doi: 10.1109/JSSC.2014.2342715[247] Posch C, Matolin D, Wohlgenannt R. A QVGA 143 dB dynamic range frame-free PWM image sensor with lossless pixel-level video compression and time-domain CDS. IEEE J Solid State Circuits, 2011, 46, 259 doi: 10.1109/JSSC.2010.2085952[248] Chen S S, Guo M H. Live demonstration: CeleX-V: A 1M pixel multi-mode event-based sensor. 2019 IEEE/CVF Conference on Computer Vision and Pattern Recognition Workshops, 2019, 1682[249] Taverni G, Paul Moeys D, Li C H, et al. Front and back illuminated dynamic and active pixel vision sensors comparison. IEEE Trans Circuits Syst II, 2018, 65, 677 doi: 10.1109/TCSII.2018.2824899[250] Park D, Lee S W, Han J, et al. A 0.8µm smart dual conversion gain pixel for 64 megapixels CMOS image sensor with 12k e- full-well capacitance and low dark noise. 2019 IEEE Int Electron Devices Meet, 2019, 16.2.1[251] Miyauchi K, Mori K, Isozaki T, et al. 4.0µm stacked voltage mode global shutter pixels with a BSI LOFIC and a PDAF capability. 2021 International Image Sensor Workshop, 2020, R49[252] Hirata T, Murata H, Matsuda H, et al. A 1-inch 17Mpixel 1000fps block-controlled coded-exposure back-illuminated stacked CMOS image sensor for computational imaging and adaptive dynamic range control. 2021 IEEE International Solid-State Circuits Conference, 2021, 120[253] Sakano Y, Toyoshima T, Nakamura R, et al. A 132dB single-exposure-dynamic-range CMOS image sensor with high temperature tolerance. 2020 IEEE International Solid-State Circuits Conference, 2020, 106[254] Blair S, Cui N, Garcia M, et al. A 120dB dynamic range logarithmic multispectral imager for near-infrared fluorescence image-guided surgery. 2020 IEEE International Symposium on Circuits and Systems, 2020, 1[255] Finateu T, Niwa A, Matolin D, et al. A 1280 × 720 back-illuminated stacked temporal contrast event-based vision sensor with 4.86µm pixels, 1.066GEPS readout, programmable event-rate controller and compressive data-formatting pipeline. 2020 IEEE International Solid-State Circuits Conference, 2020, 112[256] Boukhayma A, Caizzone A, Enz C. A CMOS image sensor pixel combining deep sub-electron noise with wide dynamic range. IEEE Electron Device Lett, 2020, 41, 880 doi: 10.1109/LED.2020.2988378[257] Sato M, Yorikado Y, Matsumura Y, et al. A 0.50e-rms Noise 1.45µm-pitch CMOS image sensor with reference-shared in-pixel differential amplifier at 8.3Mpixel 35fps. 2020 IEEE International Solid-State Circuits Conference, 2020, 108[258] Yeh S F, Chou K Y, Tu H Y, et al. A 0.66 erms− temporal-readout-noise 3-D-stacked CMOS image sensor with conditional correlated multiple sampling technique. IEEE J Solid State Circuits, 2018, 53, 527 doi: 10.1109/JSSC.2017.2765927[259] Ma J J, Zhang D X, Elgendy O, et al. A photon-counting 4Mpixel stacked BSI quanta image sensor with 0.3e- read noise and 100 dB single-exposure dynamic range. 2021 Symposium on VLSI Circuits, 2021, 1[260] Ota Y, Morimoto K, Sasago T, et al. A 0.37W 143dB-dynamic-range 1Mpixel backside-illuminated charge-focusing SPAD image sensor with pixel-wise exposure control and adaptive clocked recharging. 2022 IEEE International Solid-State Circuits Conference, 2022, 65, 94[261] Padmanabhan P, Zhang C, Cazzaniga M, et al. A 256×128 3D-stacked (45nm) SPAD FLASH LiDAR with 7-level coincidence detection and progressive gating for 100m range and 10klux background light. 2021 IEEE International Solid-State Circuits Conference, 2021, 64, 111[262] Kumagai O, Ohmachi J, Matsumura M, et al. A 189×600 back-illuminated stacked SPAD direct time-of-flight depth sensor for automotive LiDAR systems. 2021 IEEE International Solid-State Circuits Conference, 2021, 64, 110[263] Niclass C, Soga M, Matsubara H, et al. A 100-m range 10-frame/s 340×96-pixel time-of-flight depth sensor in 0.18-μm CMOS. IEEE J Solid State Circuits, 2013, 48, 559 doi: 10.1109/JSSC.2012.2227607[264] Perenzoni M, Perenzoni D, Stoppa D. A 64×64-pixel digital silicon photomultiplier direct ToF sensor with 100Mphotons/s/pixel background rejection and imaging/altimeter mode with 0.14% precision up to 6km for spacecraft navigation and landing. 2016 IEEE International Solid-State Circuits Conference, 2016, 118[265] Kim D, Lee S, Park D, et al. A dynamic pseudo 4-tap CMOS time-of-flight image sensor with motion artifact suppression and background light cancelling over 120klux. 2020 IEEE International Solid-State Circuits Conference, 2020, 100[266] Keel M S, Kim D, Kim Y, et al. A 1.2-mpixel indirect time-of-flight image sensor with 4-tap 3.5-μm pixels for peak current mitigation and multi-user interference cancellation. IEEE J Solid State Circuits, 2021, 56, 3209 doi: 10.1109/JSSC.2021.3112405[267] Yasutomi K, Furuhashi T, Sagawa K, et al. A 38µm range precision time-of-flight CMOS range line imager with gating driver jitter reduction using charge-injection pseudo photocurrent reference. 2022 IEEE International Solid-State Circuits Conference, 2022, 65, 100[268] Payne A, Daniel A, Mehta A, et al. A 512×424 CMOS 3D Time-of-Flight image sensor with multi-frequency photo-demodulation up to 130MHz and 2GS/s ADC. 2014 IEEE International Solid-State Circuits Conference, 2014, 134[269] Bamji C S, Mehta S, Thompson B, et al. IMpixel 65nm BSI 320MHz demodulated TOF image sensor with 3μm global shutter pixels and analog binning. 2018 IEEE International Solid-State Circuits Conference, 2018, 94[270] Keel M S, Kim D, Kim Y, et al. A 4-tap 3.5μm 1.2Mpixel indirect time-of-flight CMOS image sensor with peak current mitigation and multi-user interference cancellation. 2021 IEEE International Solid-State Circuits Conference, 2021, 64, 106[271] Okino T, Yamada S, Sakata Y, et al. A 1200×9006µm 450fps geiger-mode vertical avalanche photodiodes CMOS image sensor for a 250m time-of-flight ranging system using direct-indirect-mixed frame synthesis with configurable-depth-resolution down to 10cm. 2020 IEEE International Solid-State Circuits Conference, 2020, 96[272] Park S, Kim B, Cho J, et al. An 80×60 flash LiDAR sensor with in-pixel histogramming TDC based on quaternary search and time-gated Δ-intensity phase detection for 45m detectable range and background light cancellation. 2022 IEEE International Solid-State Circuits Conference, 2022, 98[273] Kim B, Park S, Chun J H, et al. A 48×40 13.5mm depth resolution flash LiDAR sensor with in-pixel zoom histogramming time-to-digital converter. 2021 IEEE International Solid-State Circuits Conference, 2021, 64, 108[274] Henderson R K, Johnston N, Hutchings S W, et al. A 256×256 40nm/90nm CMOS 3D-stacked 120dB dynamic-range reconfigurable time-resolved SPAD imager. 2019 IEEE International Solid-State Circuits Conference, 2019, 106[275] Park B, Park I, Park C, et al. A 64 × 64 SPAD-based indirect time-of-flight image sensor with 2-tap analog pulse counters. IEEE J Solid State Circuits, 2021, 56, 2956 doi: 10.1109/JSSC.2021.3094524[276] Keel M S, Jin Y G, Kim Y, et al. A VGA indirect time-of-flight CMOS image sensor with 4-tap 7-μm global-shutter pixel and fixed-pattern phase noise self-compensation. IEEE J Solid State Circuits, 2020, 55, 889 doi: 10.1109/JSSC.2019.2959502[277] Arute F, Arya K, Babbush R, et al. Quantum supremacy using a programmable superconducting processor. Nature, 2019, 574, 505 doi: 10.1038/s41586-019-1666-5[278] Collaborators G A Q A, Arute F, Arya K, et al. Hartree-Fock on a superconducting qubit quantum computer. Science, 2020, 369, 1084 doi: 10.1126/science.abb9811[279] Xue X, Patra B, van Dijk J P G, et al. CMOS-based cryogenic control of silicon quantum circuits. Nature, 2021, 593, 205 doi: 10.1038/s41586-021-03469-4[280] Ball P. First 100-QUBIT quantum computer enters crowded race. Nature, 2021, 599, 542 doi: 10.1038/d41586-021-03476-5[281] Pudenz K L, Albash T, Lidar D A. Error-corrected quantum annealing with hundreds of qubits. Nat Commun, 2014, 5, 3243 doi: 10.1038/ncomms4243[282] Charbon E, Sebastiano F, Babaie M, et al. Cryo-CMOS circuits and systems for scalable quantum computing. 2017 IEEE International Solid-State Circuits Conference, 2017, 264[283] Patra B, Incandela R M, van Dijk J P G, et al. Cryo-CMOS circuits and systems for quantum computing applications. IEEE J Solid State Circuits, 2018, 53, 309 doi: 10.1109/JSSC.2017.2737549[284] Bardin J C, Jeffrey E, Lucero E, et al. A 28nm bulk-CMOS 4-to-8GHz 2mW cryogenic pulse modulator for scalable quantum computing. 2019 IEEE International Solid-State Circuits Conference, 2019, 456[285] Patra B, van Dijk J P G, Subramanian S, et al. A scalable cryo-CMOS 2-to-20 GHz digitally intensive controller for 4×32 frequency multiplexed spin qubits/transmons in 22nm FinFET technology for quantum computers. 2020 IEEE International Solid-State Circuits Conference, 2020, 304[286] Park J S, Subramanian S, Lampert L, et al. A fully integrated cryo-CMOS SoC for qubit control in quantum computers capable of state manipulation, readout and high-speed gate pulsing of spin qubits in Intel 22nm FFL FinFET technology. 2021 IEEE International Solid-State Circuits Conference, 2021, 208[287] Frank D J, Chakraborty S, Tien K, et al. A cryo-CMOS low-power semi-autonomous qubit state controller in 14 nm FinFET technology. 2022 IEEE International Solid-State Circuits Conference, 2022, 360[288] Kang K, Minn D, Bae S, et al. A cryo-CMOS controller IC with fully integrated frequency generators for superconducting qubits. 2022 IEEE International Solid-State Circuits Conference, 2022, 362[289] Prabowo B, Zheng G J, Mehrpoo M, et al. A 6-to-8GHz 0.17mW/qubit cryo-CMOS receiver for multiple spin qubit readout in 40nm CMOS technology. 2021 IEEE International Solid-State Circuits Conference, 2021, 212[290] Ruffino A, Peng Y T, Yang T Y, et al. A fully-integrated 40-nm 5-6.5GHz cryo-CMOS system-on-chip with I/Q receiver and frequency synthesizer for scalable multiplexed readout of quantum dots. 2021 IEEE International Solid-State Circuits Conference, 2021, 210[291] Gong J, Chen Y, Sebastiano F, et al. A 200dB FoM 4-to-5GHz cryogenic oscillator with an automatic common-mode resonance calibration for quantum computing applications. 2020 IEEE International Solid-State Circuits Conference, 2020, 308[292] Peng Y T, Ruffino A, Benserhir J, et al. A cryogenic SiGe BiCMOS hybrid class B/C mode-switching VCO achieving 201dBc/Hz figure-of-merit and 4.2GHz frequency tuning range. 2022 IEEE International Solid-State Circuits Conference, 2022, 364[293] Kiene G, Catania A, Overwater R, et al. A 1GS/s 6-to-8b 0.5mW/qubit cryo-CMOS SAR ADC for quantum computing in 40nm CMOS. 2021 IEEE International Solid-State Circuits Conference, 2021, 214[294] Qu G Y, Wang H Q, Zhao Y M, et al. A 0.28mΩ-sensitivity 105dB-dynamic-range electrochemical impedance spectroscopy soc for electrochemical gas detection. 2018 IEEE International Solid-State Circuits Conference, 2018, 286[295] Sonmezoglu S, Maharbiz M M. A 4.5mm3 deep-tissue ultrasonic implantable luminescence oxygen sensor. 2020 IEEE International Solid-State Circuits Conference, 2020, 454[296] Yeknami A F, Wang X Y, Imani S, et al. A 0.3V biofuel-cell-powered glucose/lactate biosensing system employing a 180nW 64dB SNR passive δς ADC and a 920MHz wireless transmitter. 2018 IEEE International Solid-State Circuits Conference, 2018, 284[297] El Ansary M, Soltani N, Kassiri H, et al. 50nW 5kHz-BW opamp-less ΔΣ impedance analyzer for brain neurochemistry monitoring. 2018 IEEE International Solid-State Circuits Conference, 2018, 288[298] Jang J, Lee J, Lee K R, et al. 4-camera VGA-resolution capsule endoscope with 80Mb/s body-channel communication transceiver and sub-cm range capsule localization. 2018 IEEE International Solid-State Circuits Conference, 2018, 282[299] Park J H, Tan J S Y, Wu H, et al. 1225-channel localized temperature-regulated neuromorphic retinal-prosthesis SoC with 56.3nW/channel image processor. 2020 IEEE International Solid-State Circuits Conference, 2020, 508[300] Yu Z H, Chen J C, Avants B W, et al. An 8.2mm3 implantable neurostimulator with magnetoelectric power and data transfer. 2020 IEEE International Solid-State Circuits Conference, 2020, 510[301] Lee S, Cortese A J, Trexel P, et al. A 330μm × 90μm opto-electronically integrated wireless system-on-chip for recording of neural activities. 2018 IEEE International Solid-State Circuits Conference, 2018, 292[302] Xu J W, Konijnenburg M, Song S, et al. A 665μW silicon photomultiplier-based NIRS/EEG/EIT monitoring ASIC for wearable functional brain imaging. IEEE Trans Biomed Circuits Syst, 2018, 12, 1267 doi: 10.1109/TBCAS.2018.2883289[303] Li J M, Dong Y L, Park J H, et al. Human-body-coupled power-delivery and ambient-energy-harvesting ICs for a full-body-area power sustainability. 2020 IEEE International Solid-State Circuits Conference, 2020, 514[304] Tang T, Yan L, Park J H, et al. EEG dust: A BCC-based wireless concurrent recording/transmitting concentric electrode. 2020 IEEE International Solid-State Circuits Conference, 2020, 516 -

Proportional views

DownLoad:

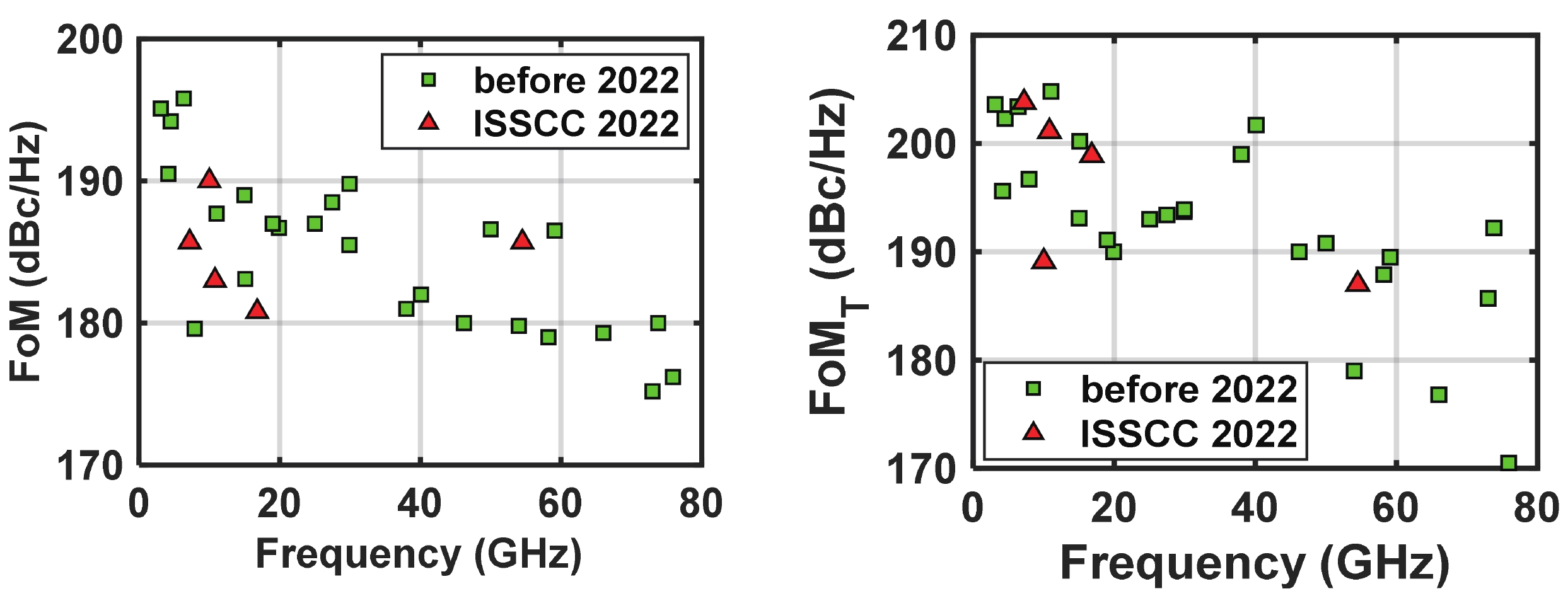

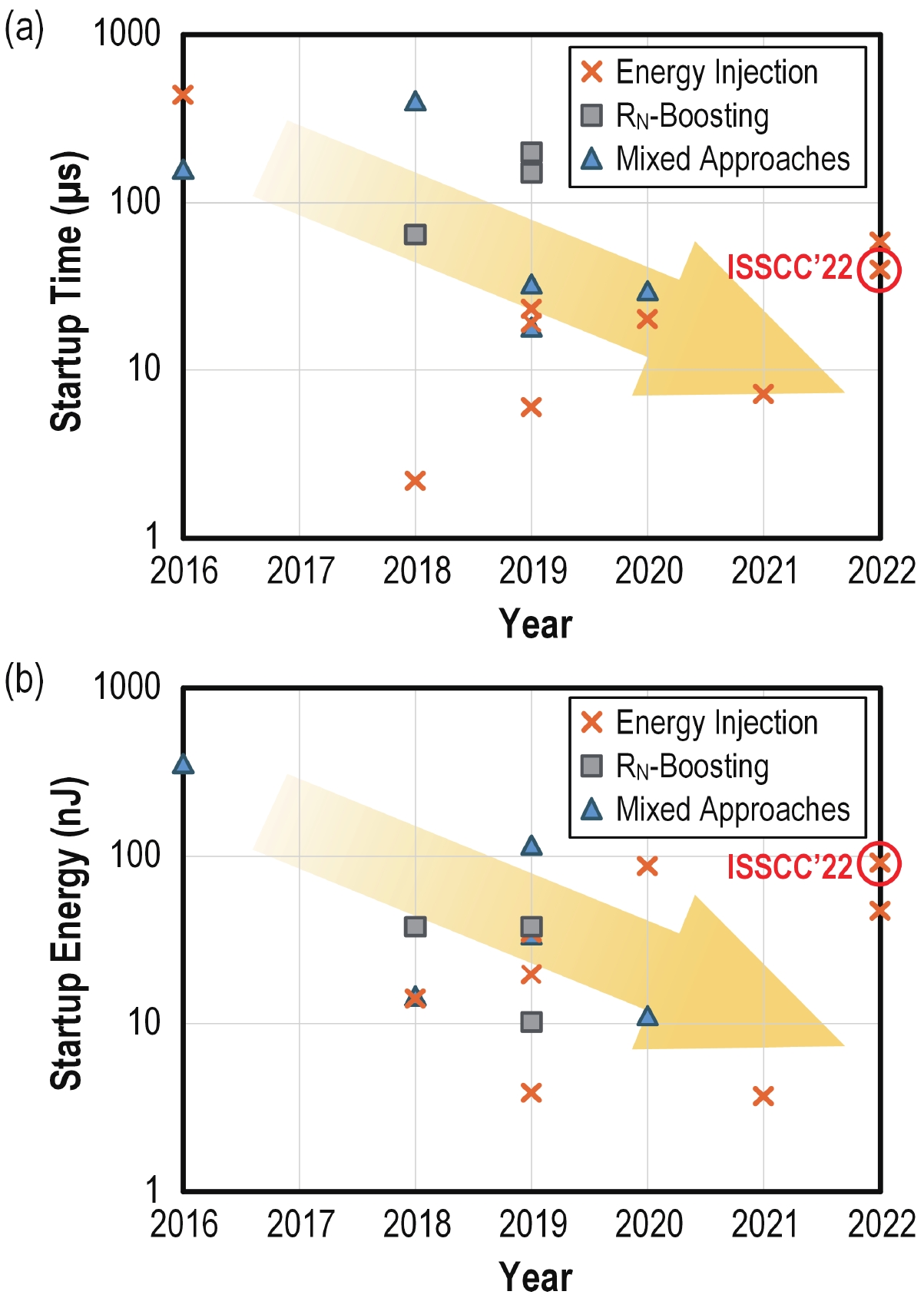

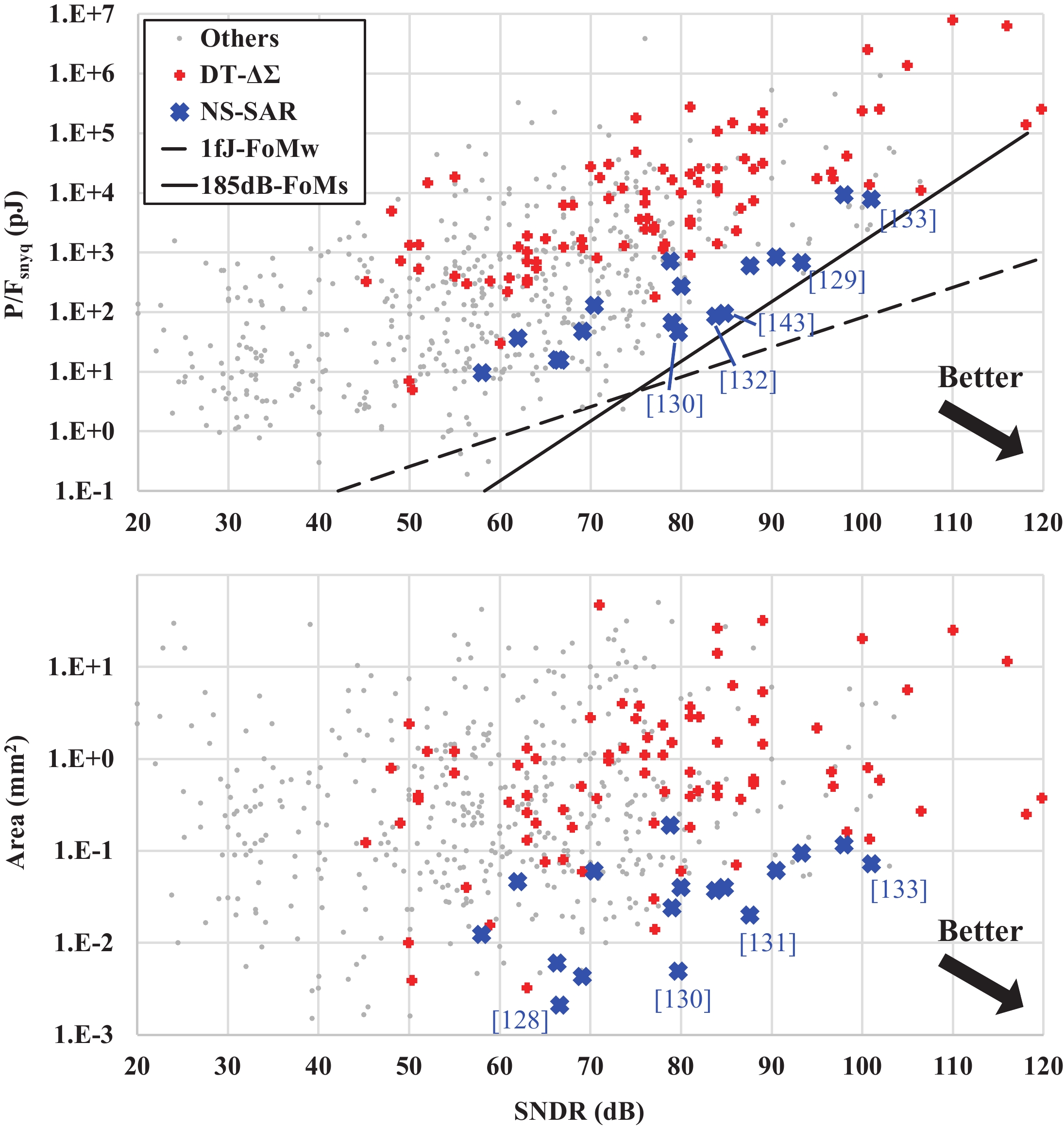

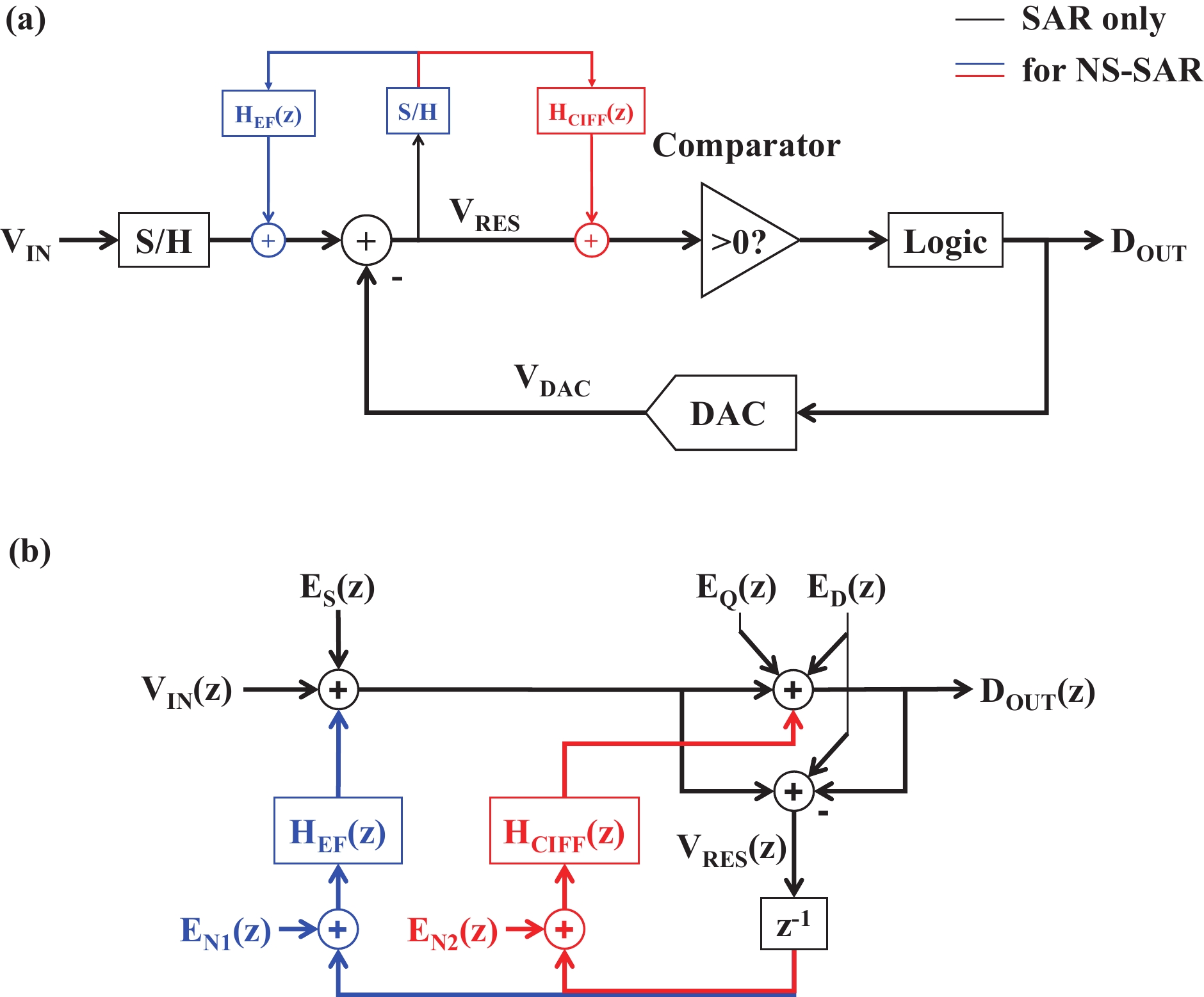

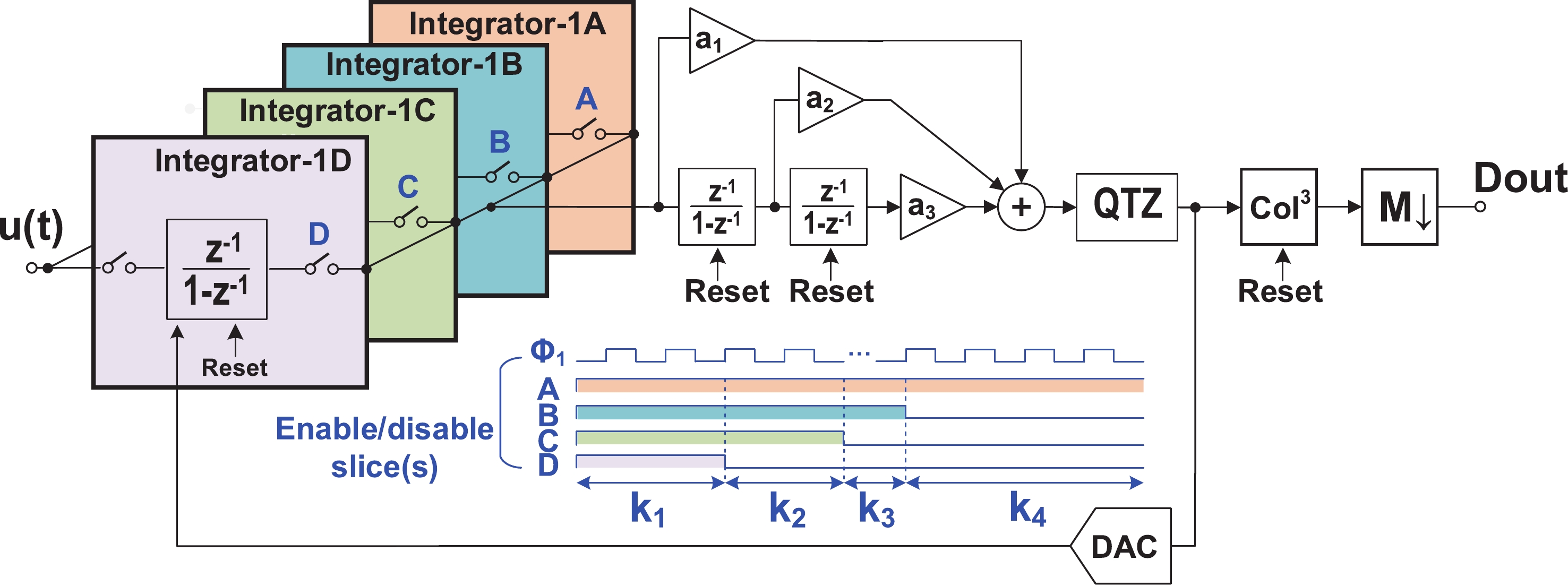

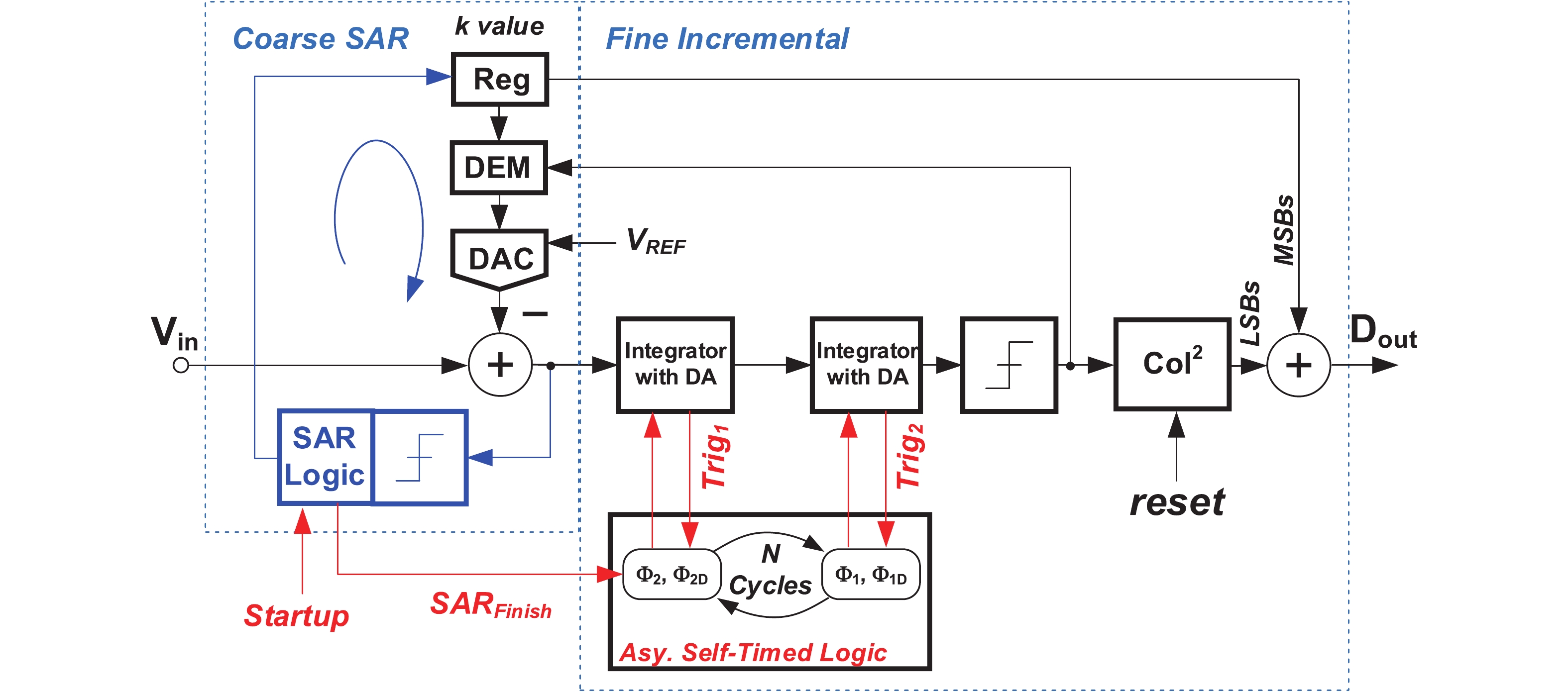

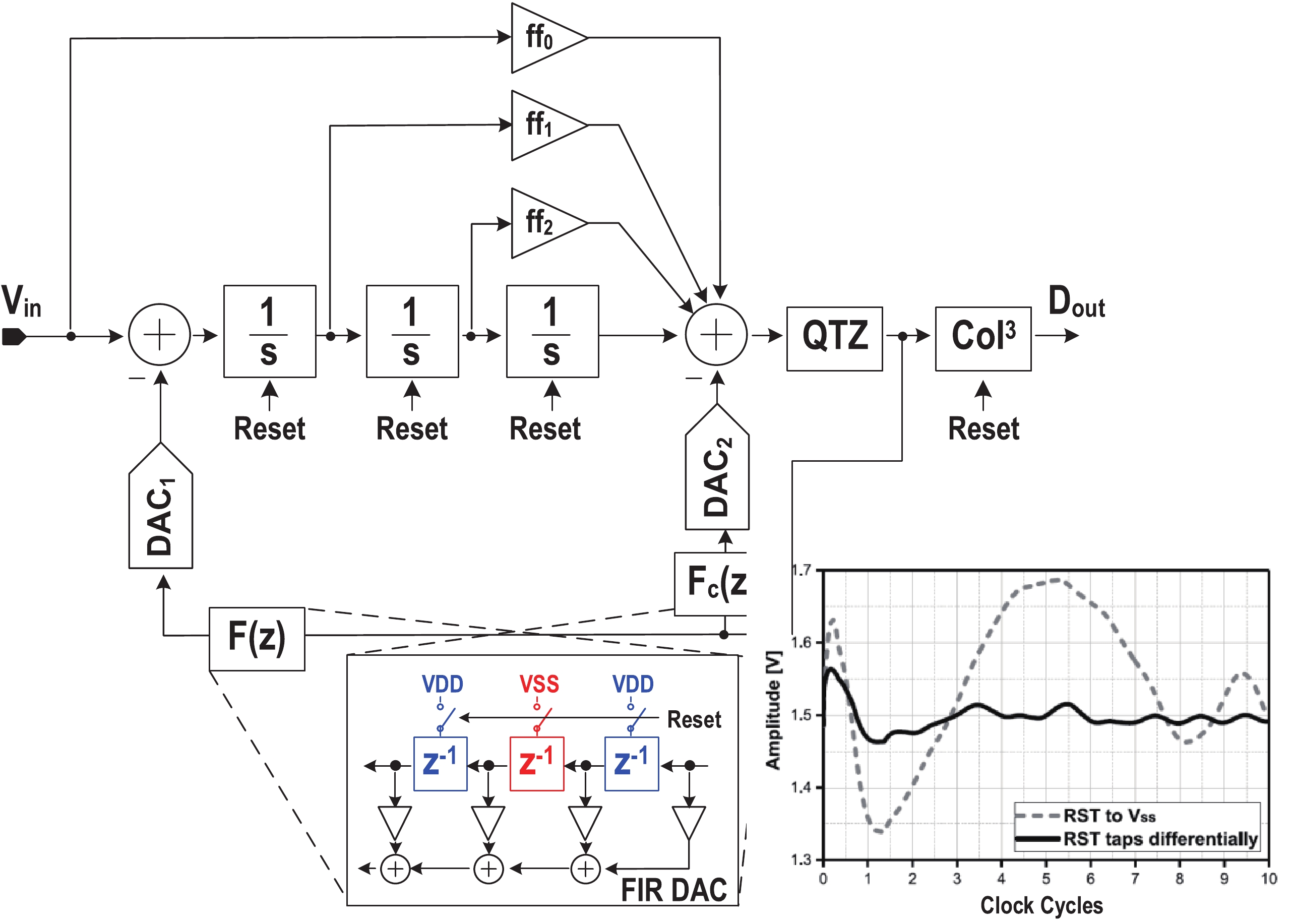

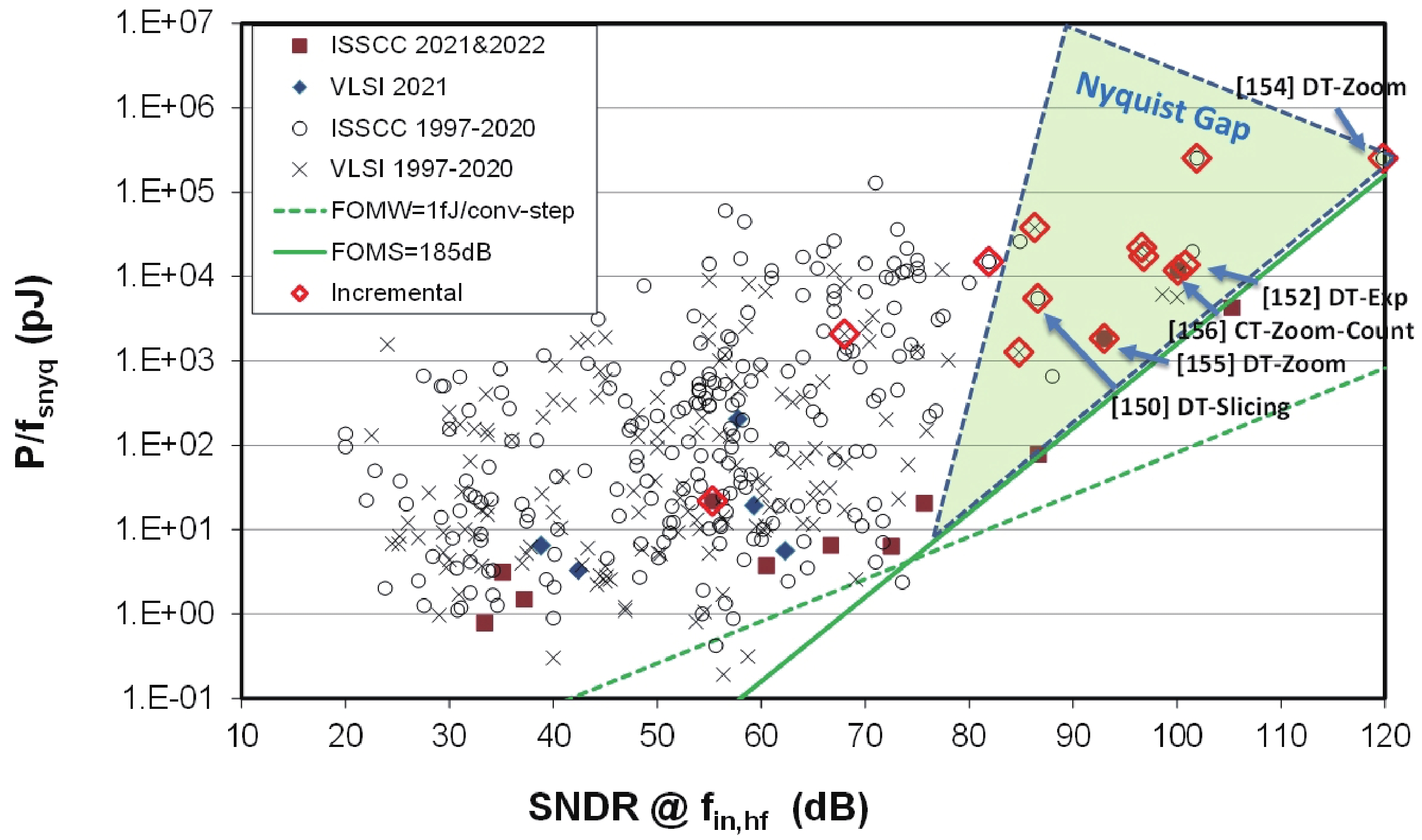

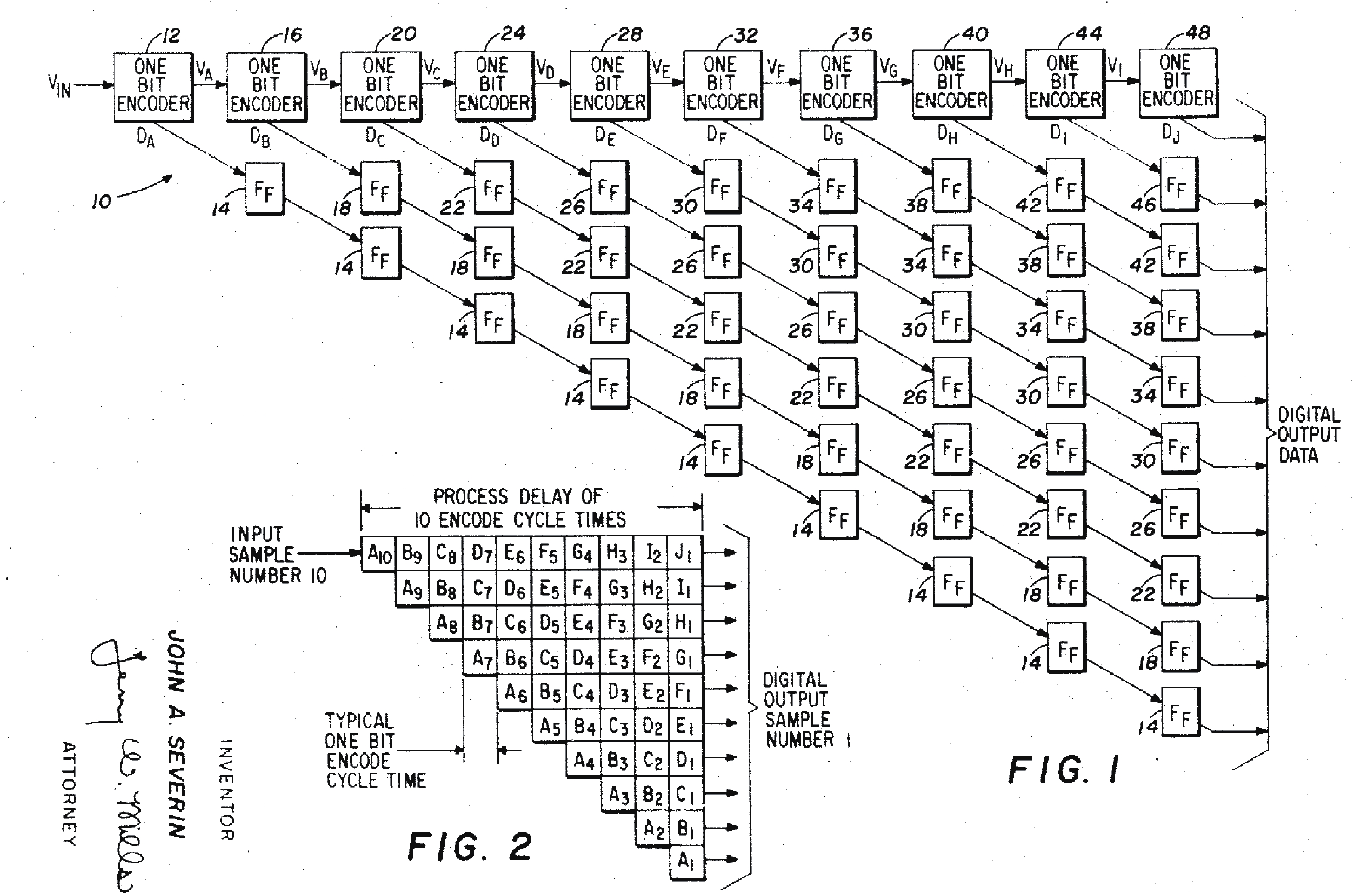

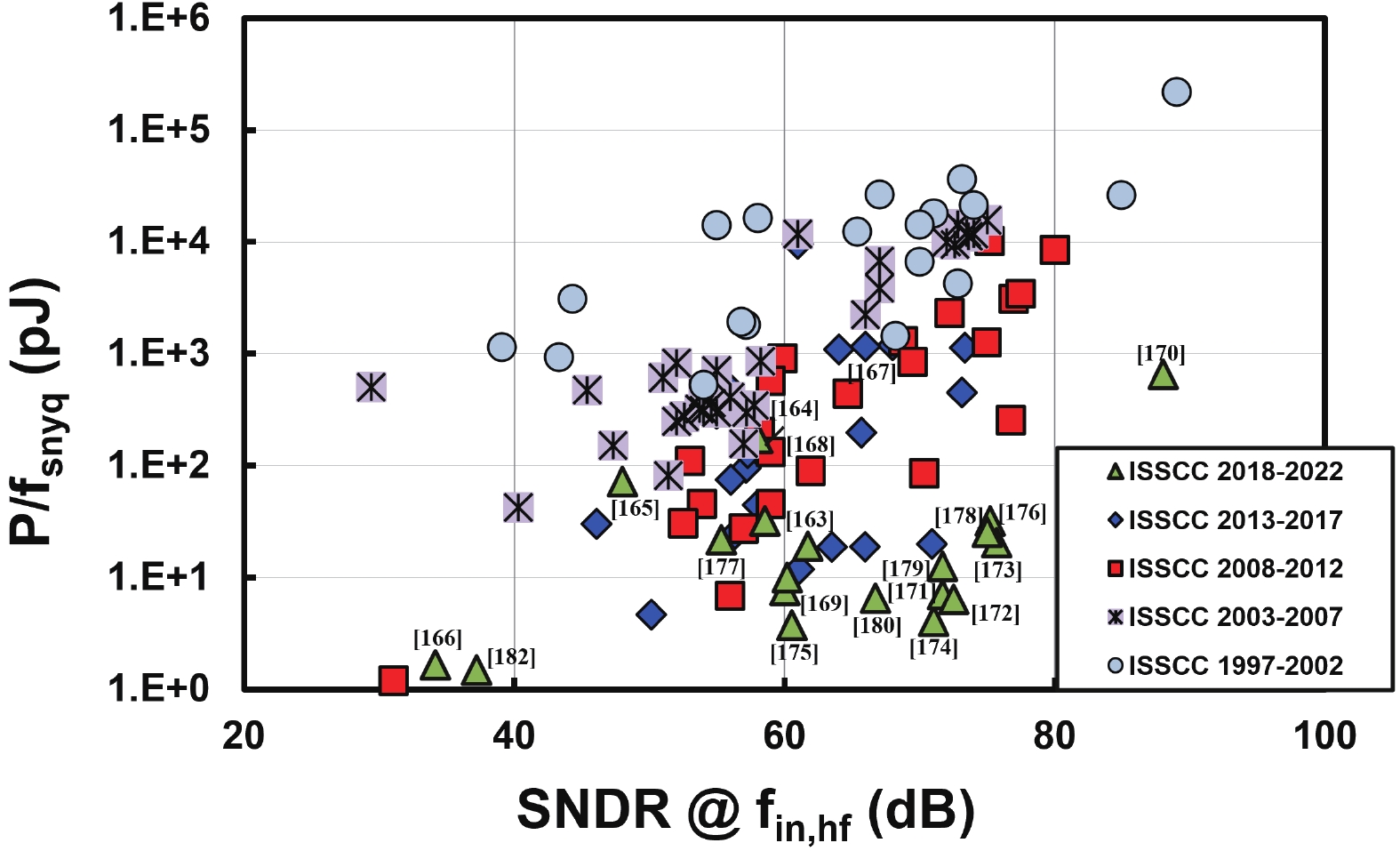

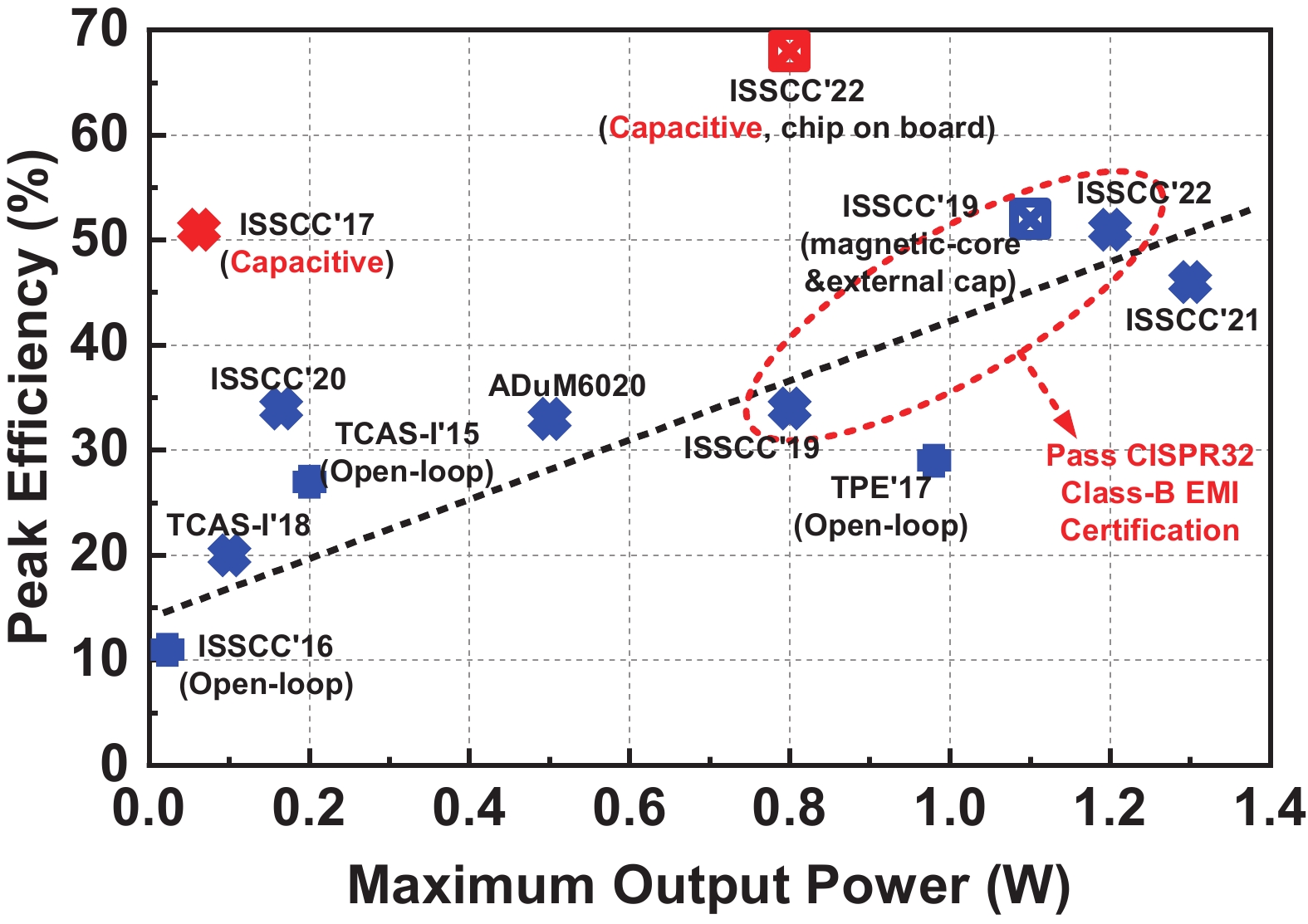

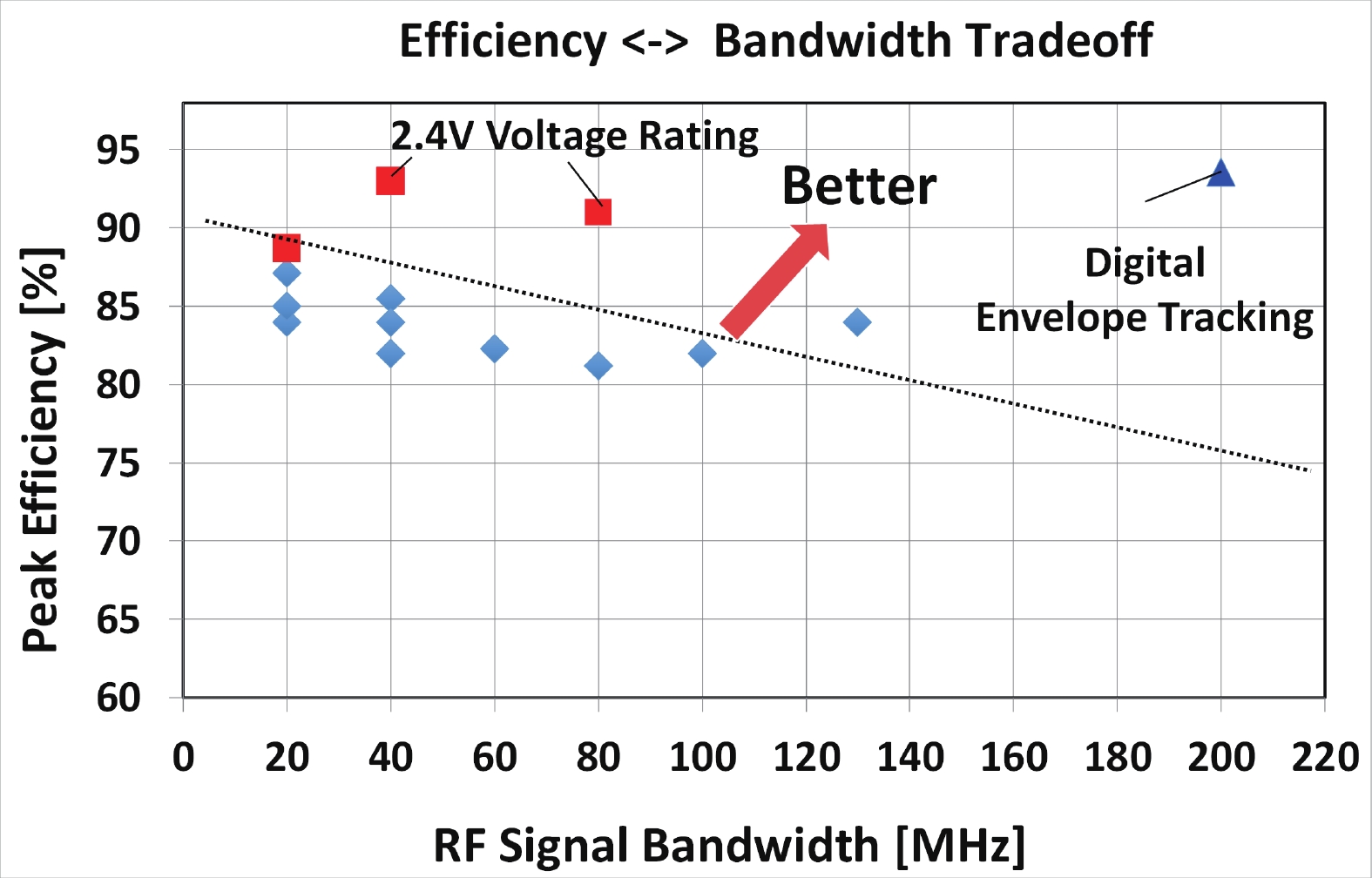

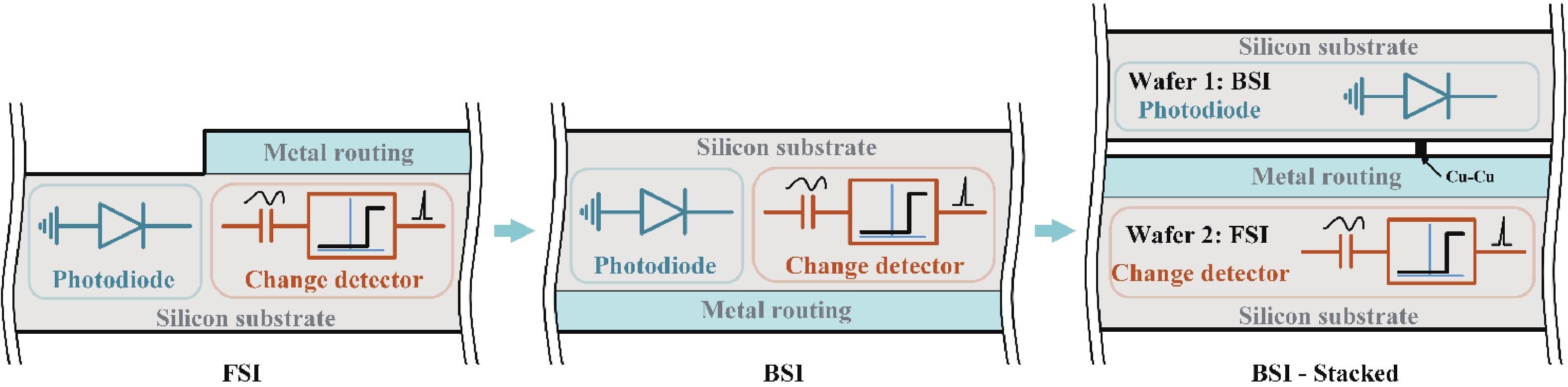

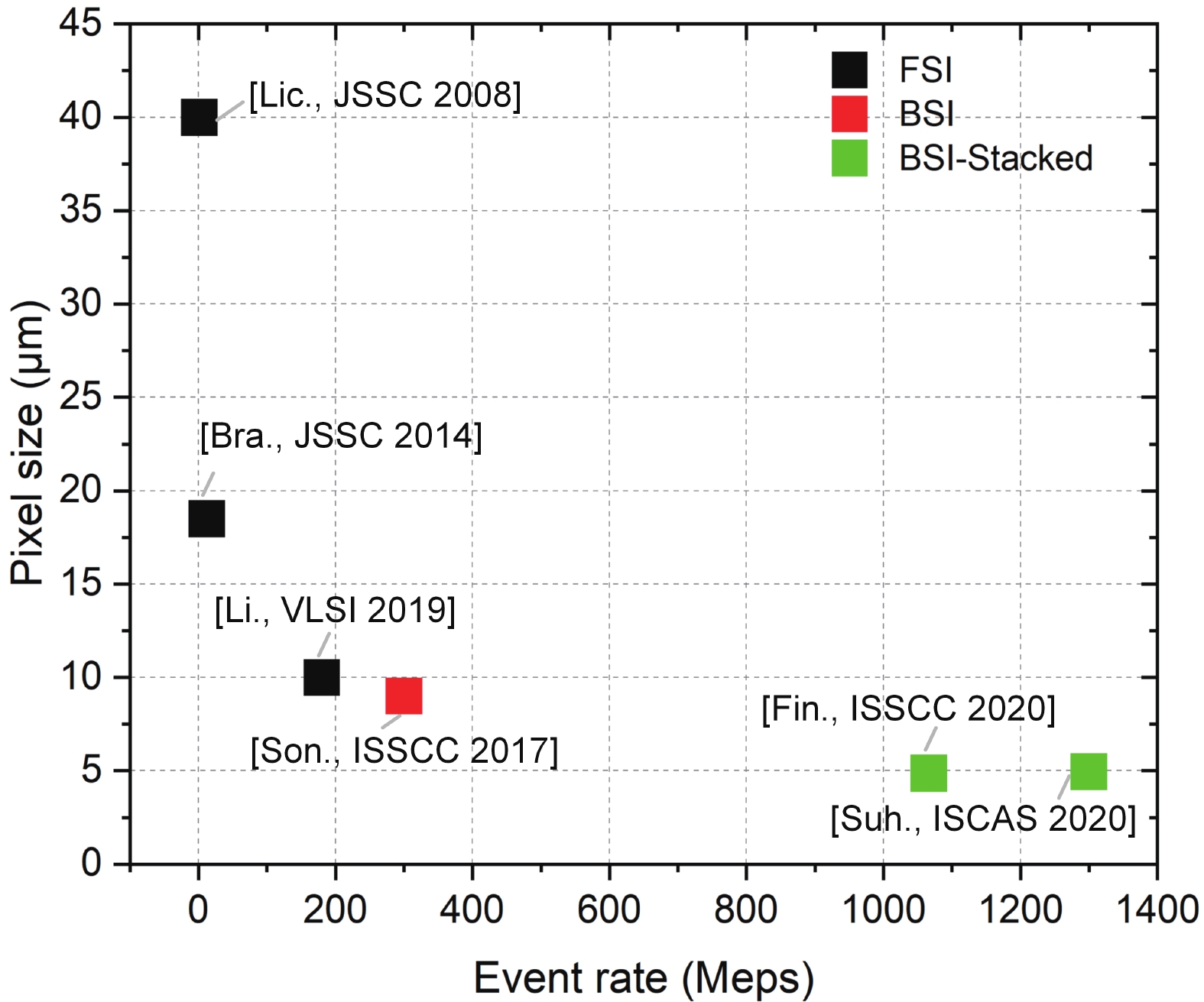

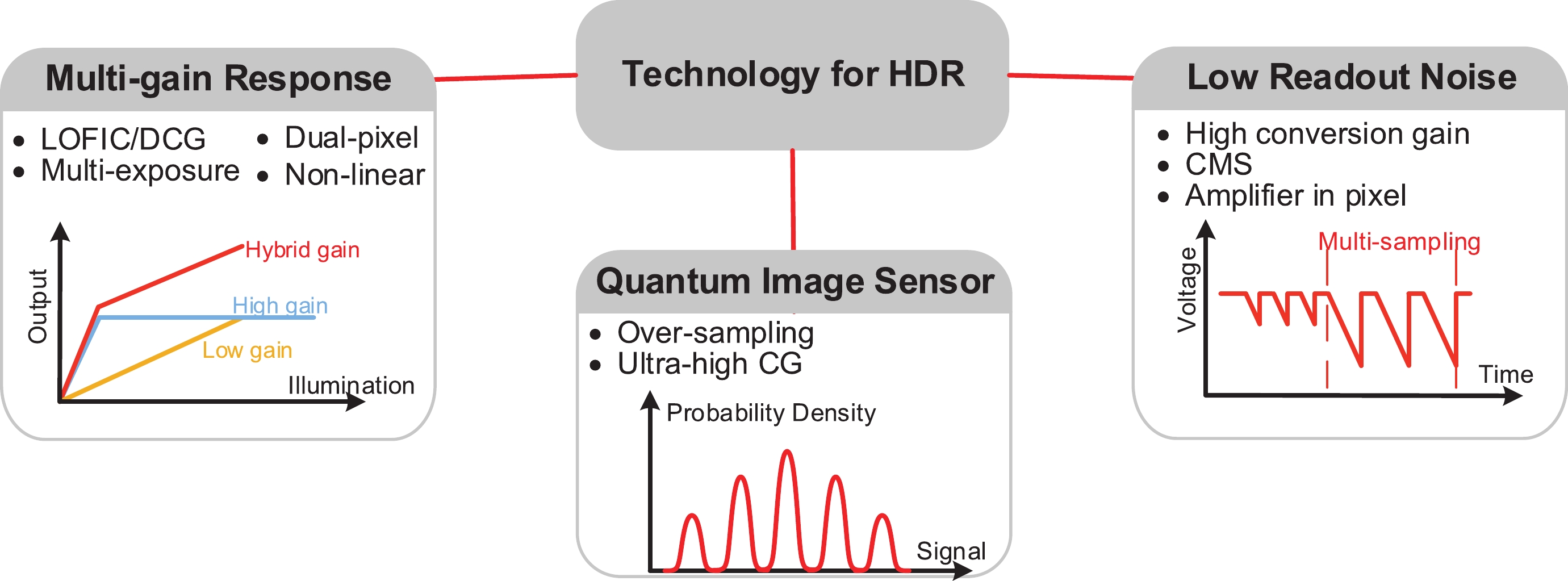

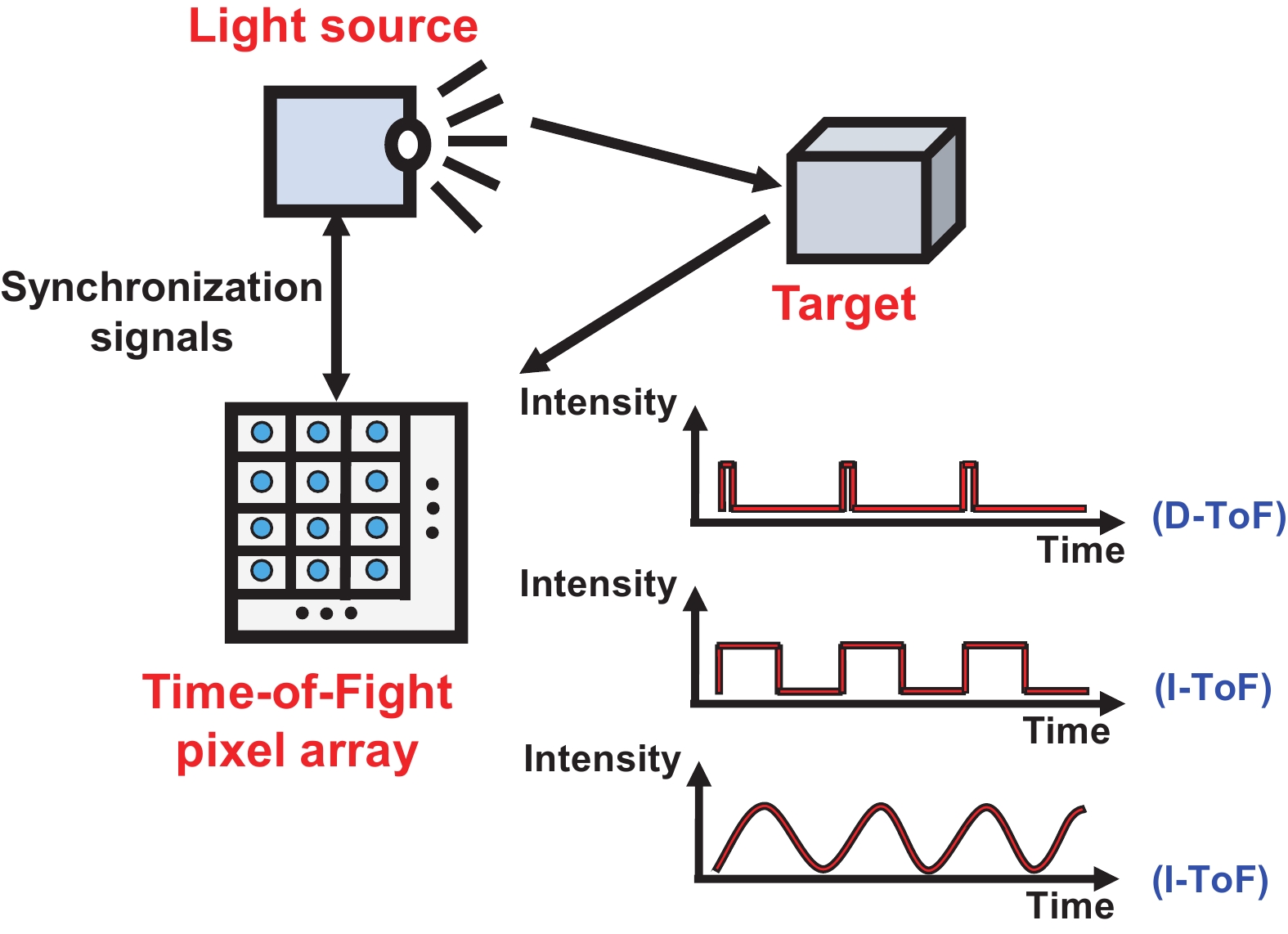

DownLoad: