| Citation: |

You Li, Junsheng Lü, Yumei Zhou, Jianzhong Zhao, Yuhu Chen, Feng Zhang. A 5 Gb/s low area CDR for embedded clock serial links[J]. Journal of Semiconductors, 2015, 36(2): 025005. doi: 10.1088/1674-4926/36/2/025005

****

Y Li, J Lü, Y M Zhou, J Z Zhao, Y H Chen, F Zhang. A 5 Gb/s low area CDR for embedded clock serial links[J]. J. Semicond., 2015, 36(2): 025005. doi: 10.1088/1674-4926/36/2/025005.

|

A 5 Gb/s low area CDR for embedded clock serial links

DOI: 10.1088/1674-4926/36/2/025005

More Information

-

Abstract

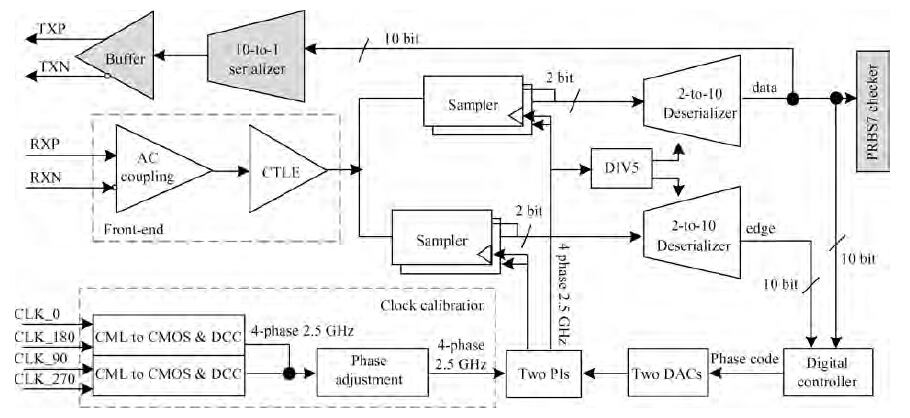

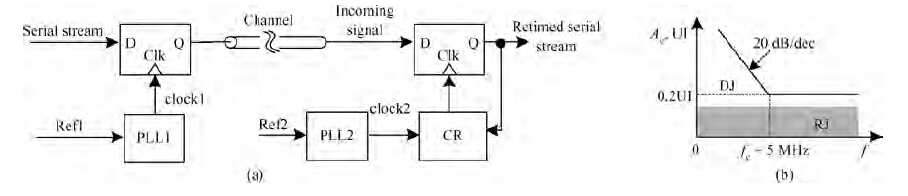

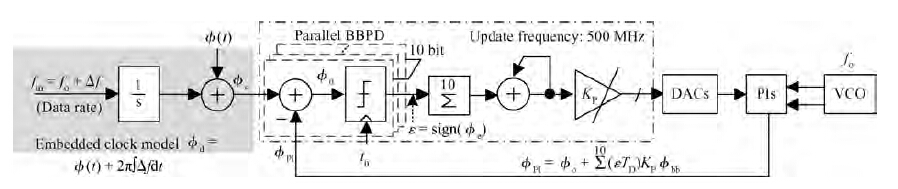

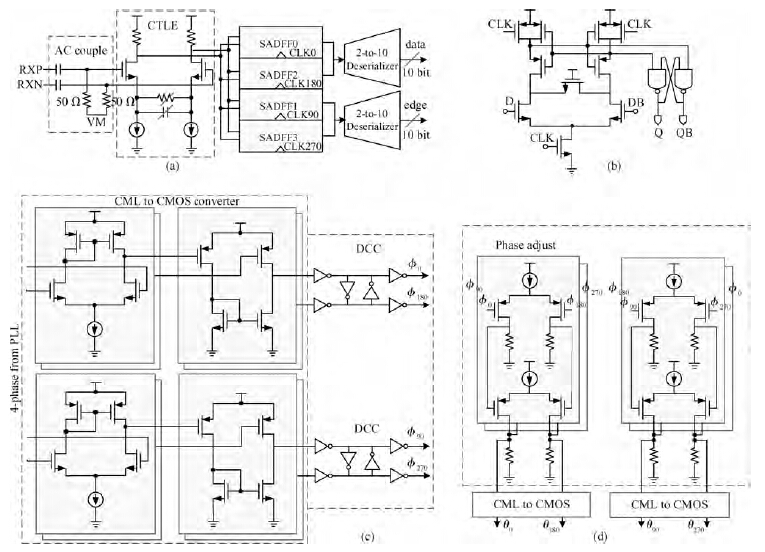

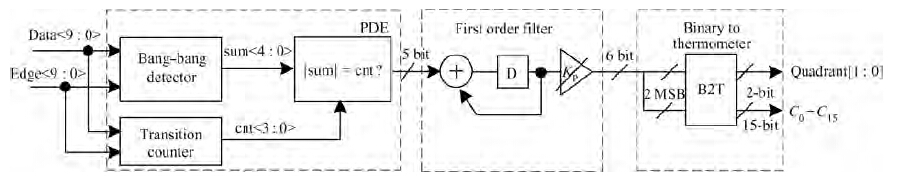

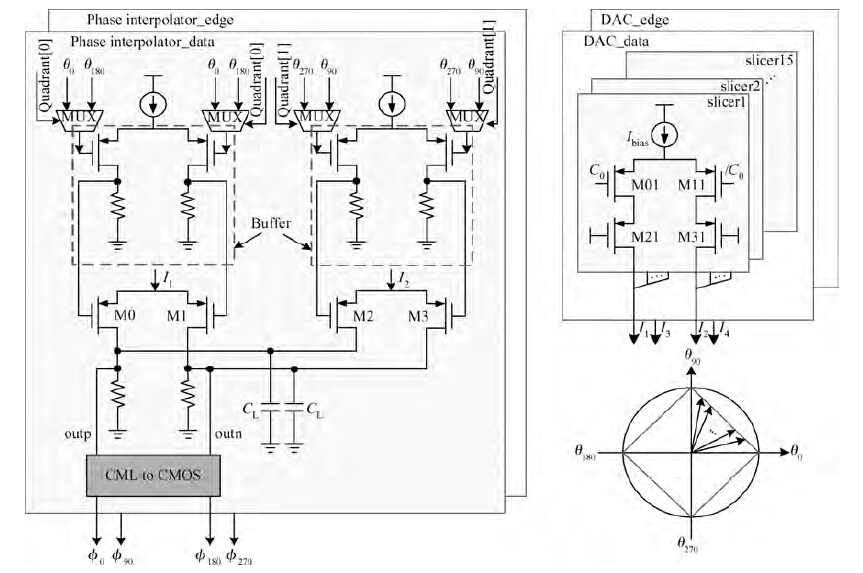

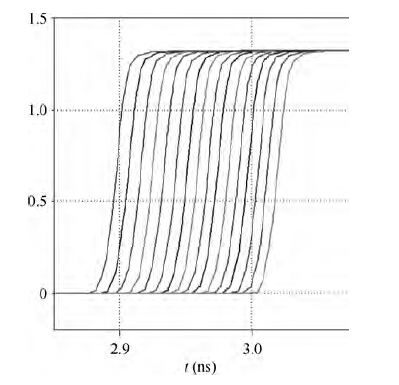

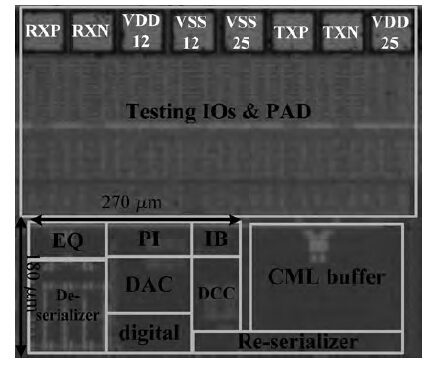

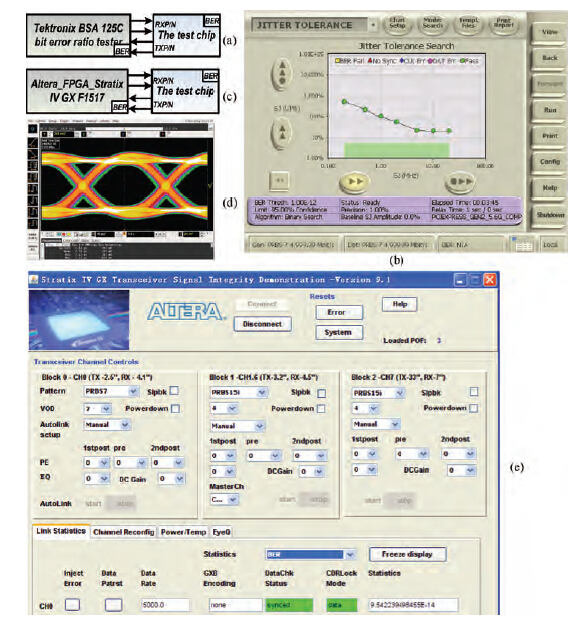

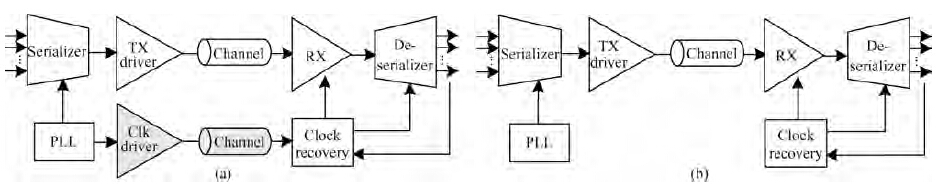

A multi-standard compatible clock and data recovery circuit (CDR) with a programmable equalizer and wide tracking range is presented. Considering the jitter performance, tracking range and chip area, the CDR employs a first-order digital loop filter, two 6-bit DACs and high linearity phase interpolators to achieve high phase resolution and low area. Meanwhile the tracking range is greater than ± 2200 ppm, making this proposed CDR suitable for the embedded clock serial links. A test chip was fabricated in the 55 nm CMOS process. The measurements show that the test chip can achieve BER <10-12 and meet the jitter tolerance specification. The test chip occupies 0.19 mm2 with a 0.0486 mm2 CDR core, which only consumes 30 mW from a 1.2 V supply at 5 Gb/s. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] -

Proportional views

DownLoad:

DownLoad: