| Citation: |

Yiling Xie, Baochuang Wang, Dihu Chen, Jianping Guo. An NMOS output-capacitorless low-dropout regulator with dynamic-strength event-driven charge pump[J]. Journal of Semiconductors, 2024, 45(6): 062203. doi: 10.1088/1674-4926/23120057

****

Y L Xie, B C Wang, D H Chen, and J P Guo, An NMOS output-capacitorless low-dropout regulator with dynamic-strength event-driven charge pump[J]. J. Semicond., 2024, 45(6), 062203 doi: 10.1088/1674-4926/23120057

|

An NMOS output-capacitorless low-dropout regulator with dynamic-strength event-driven charge pump

DOI: 10.1088/1674-4926/23120057

More Information

-

Abstract

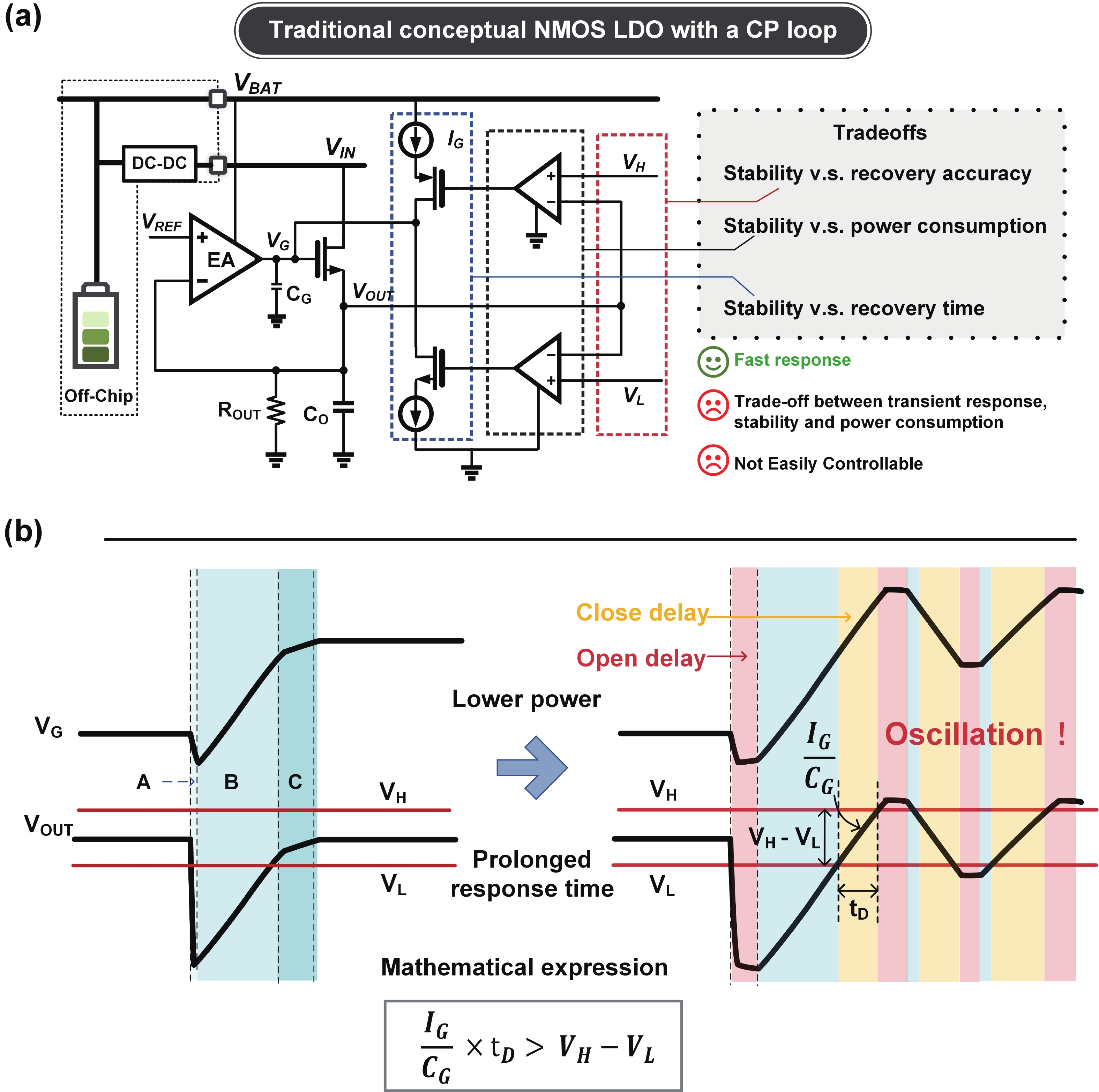

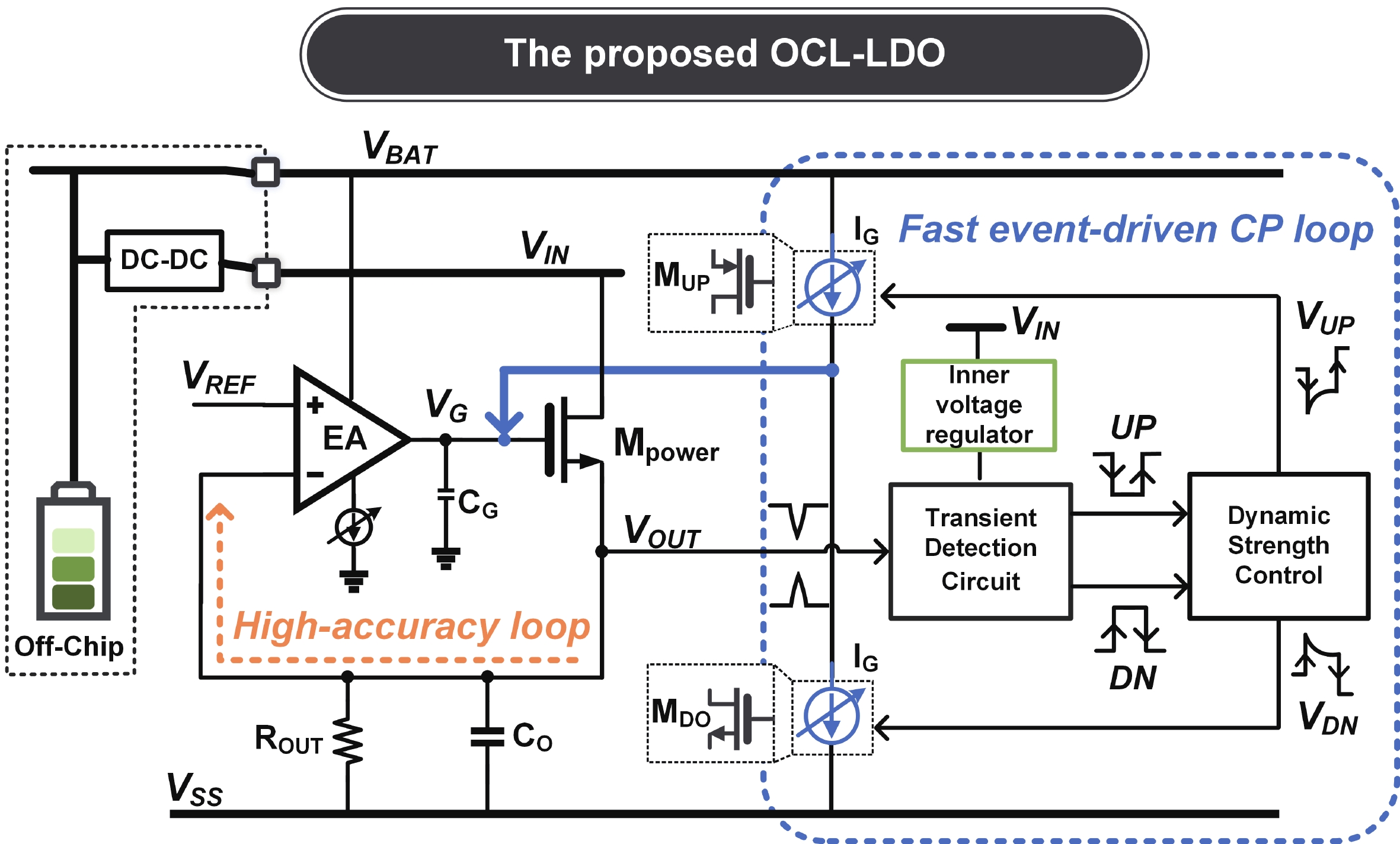

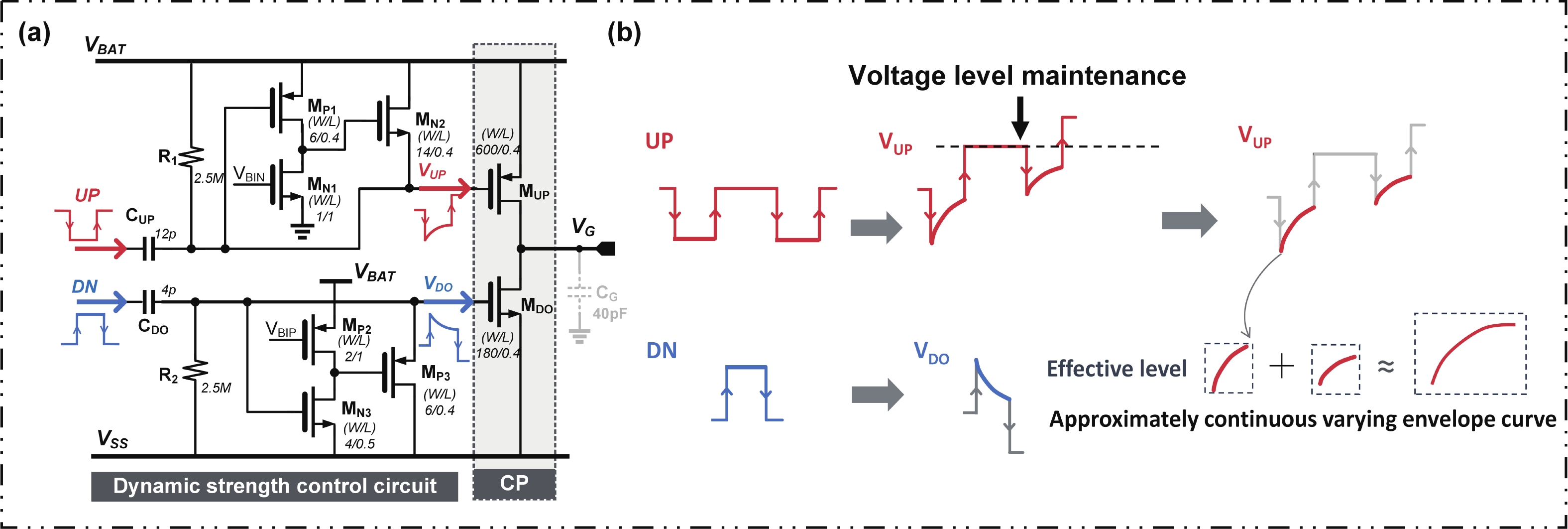

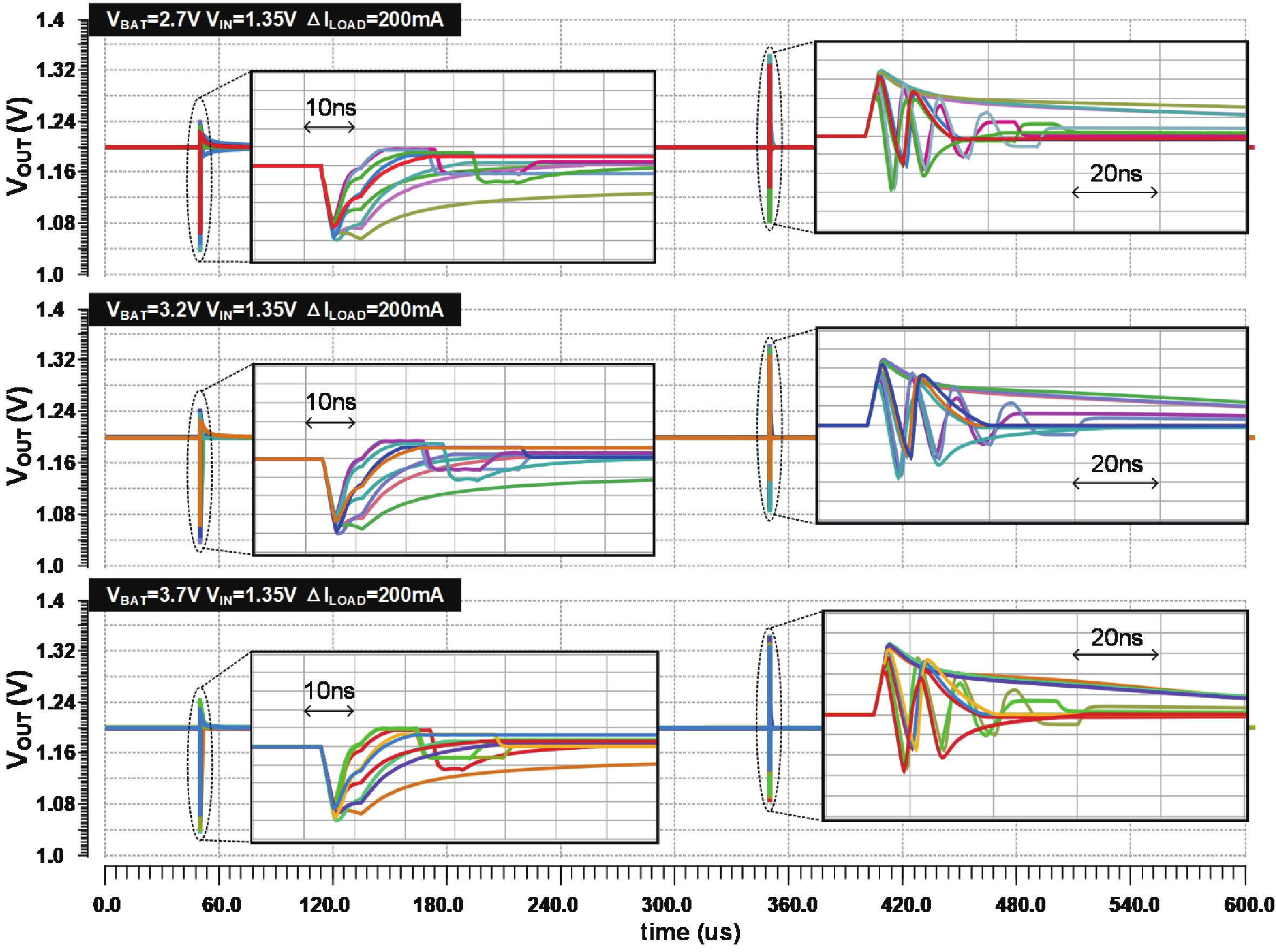

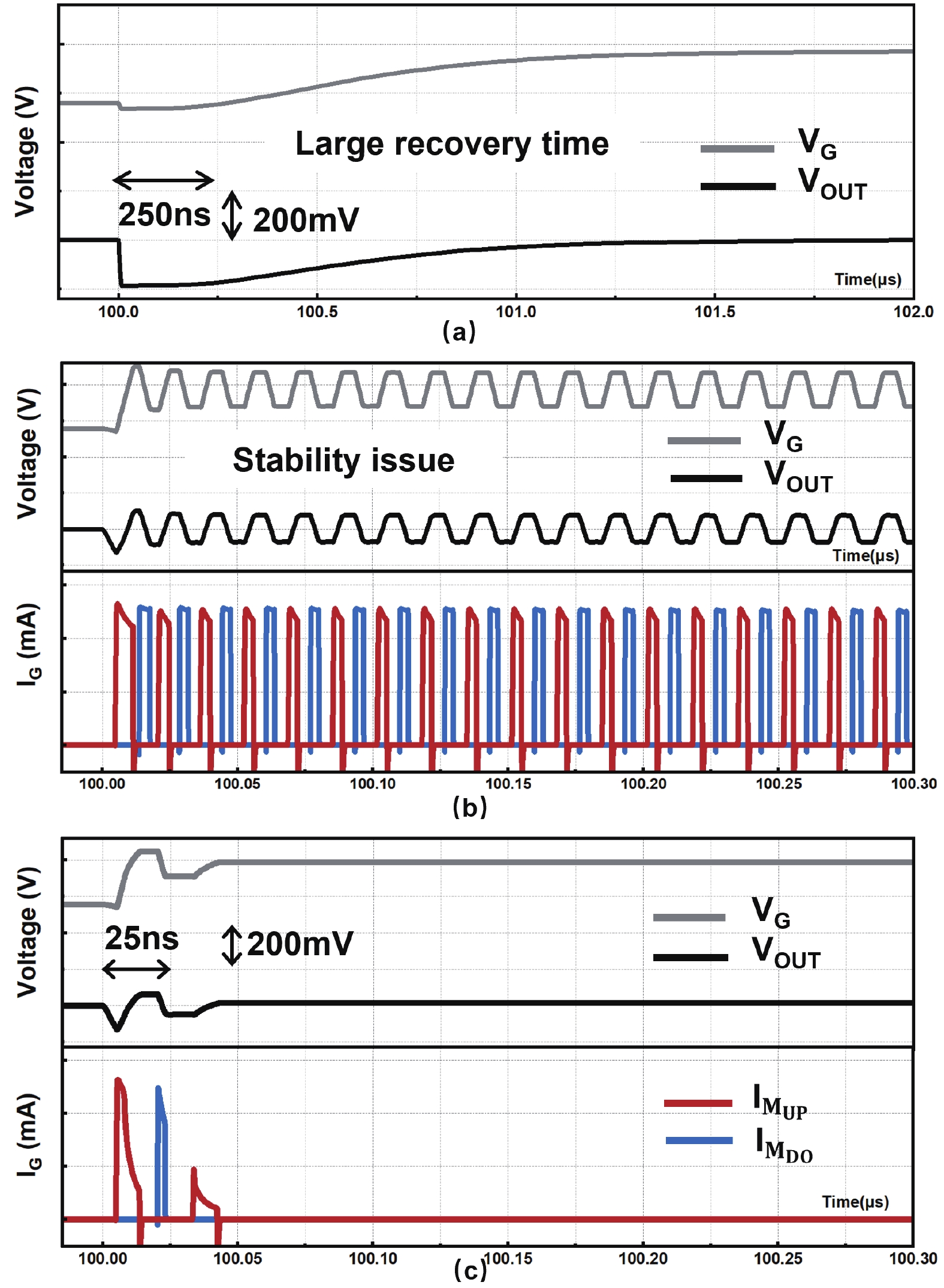

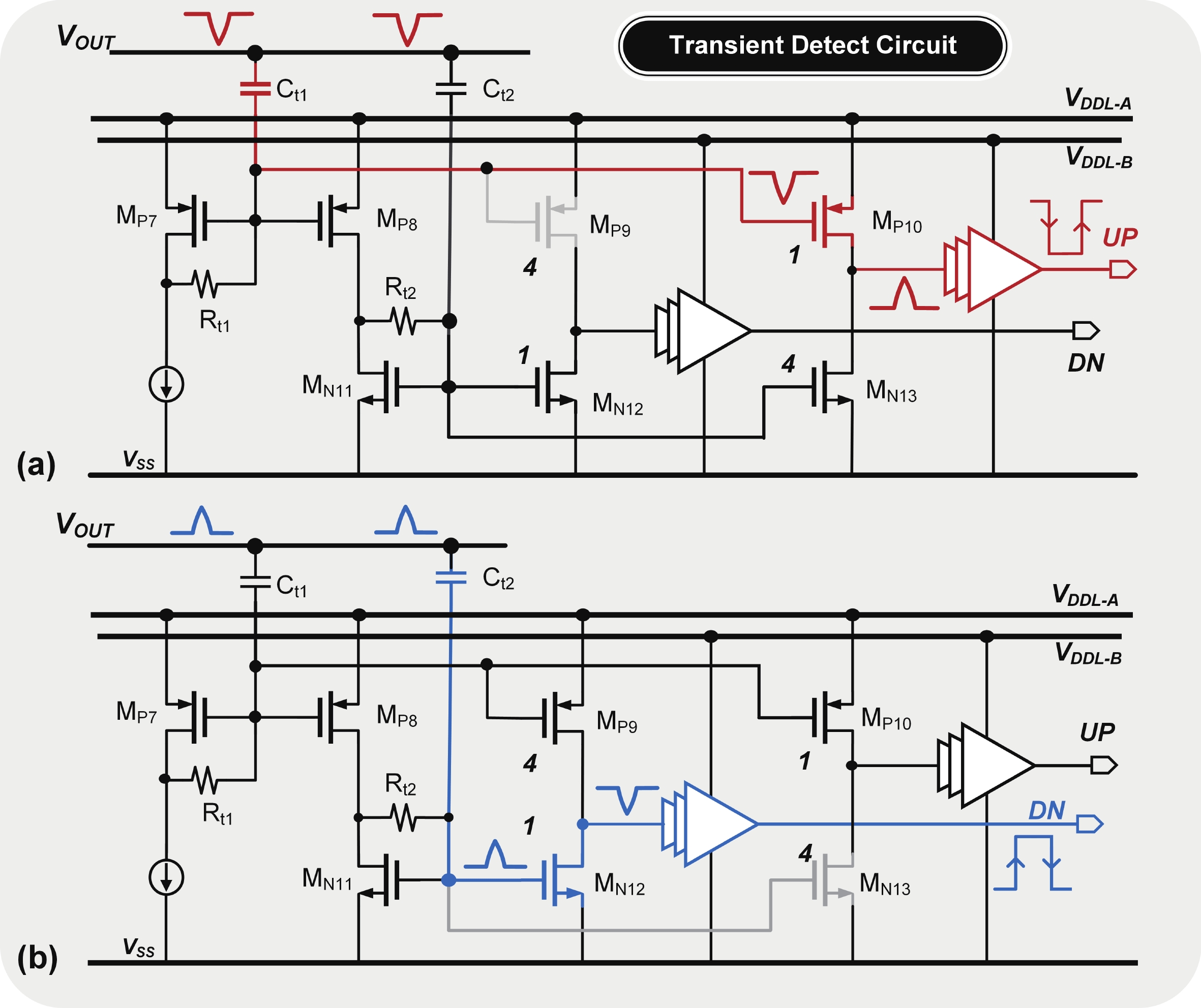

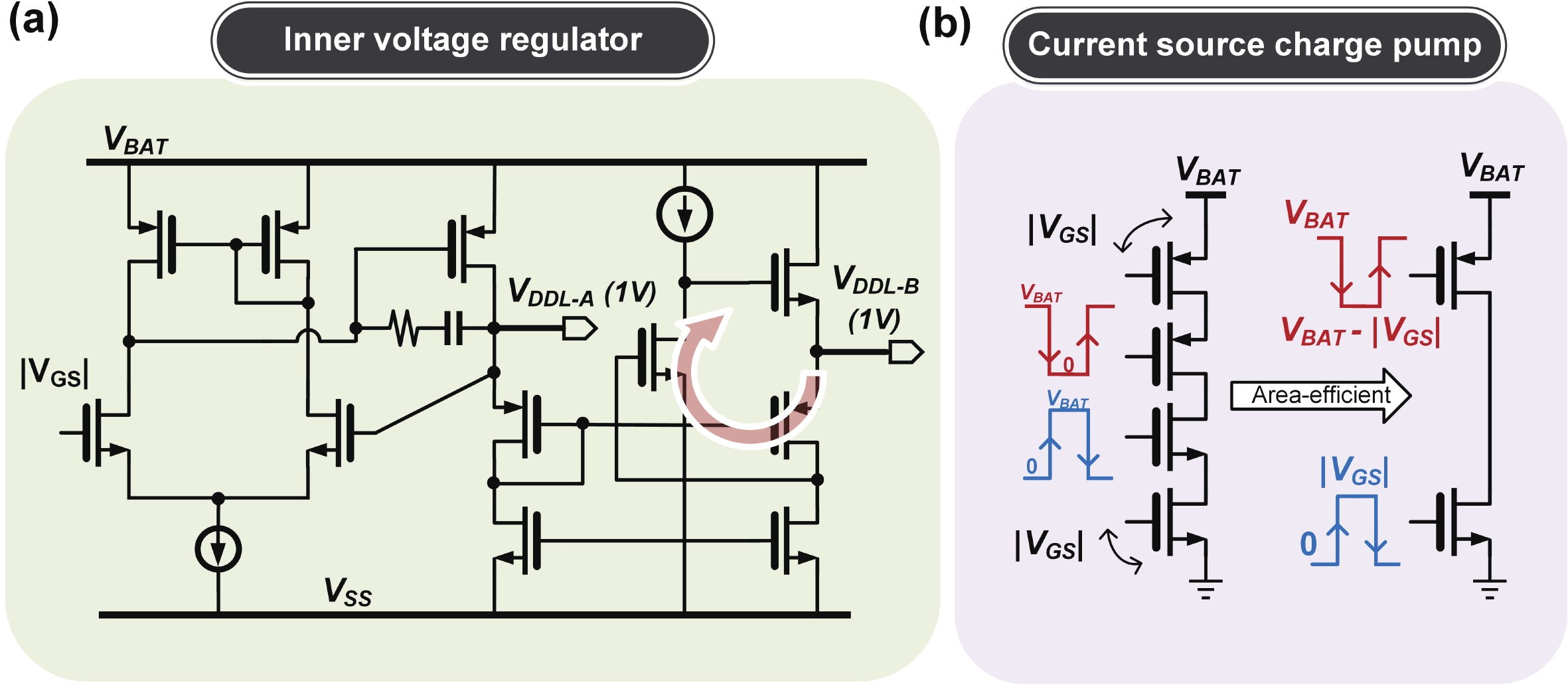

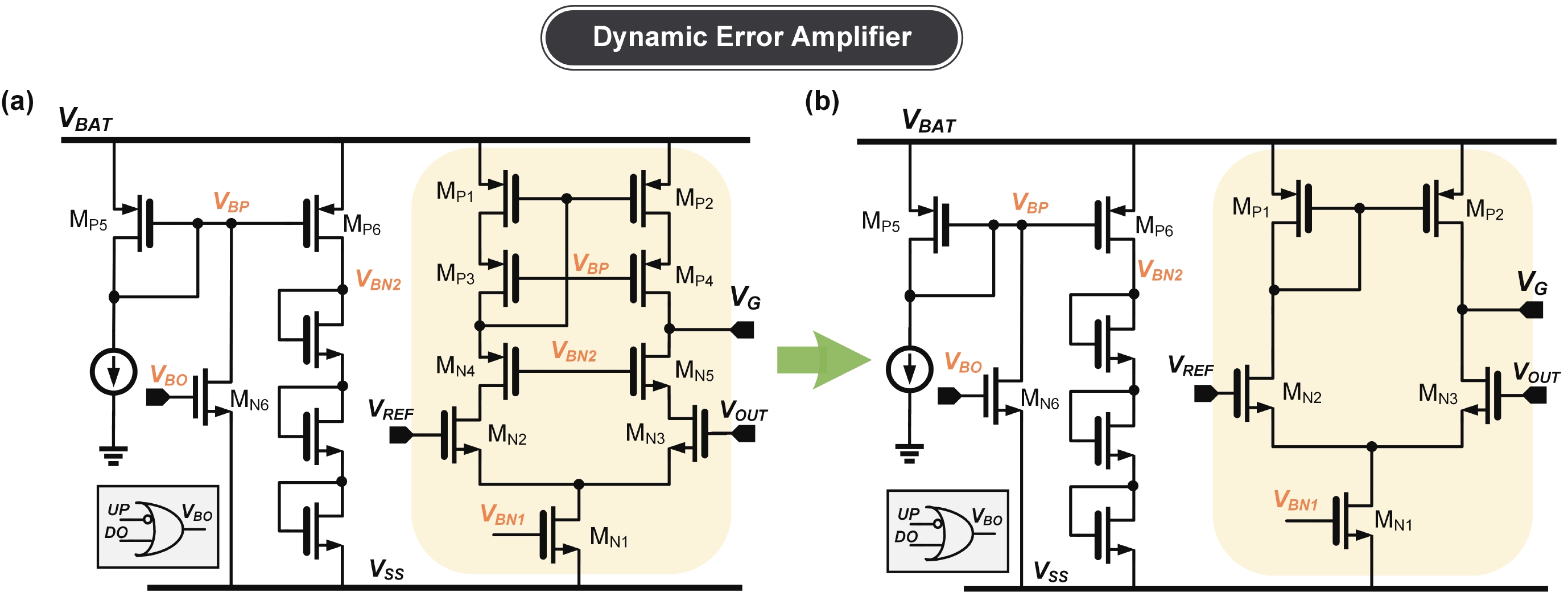

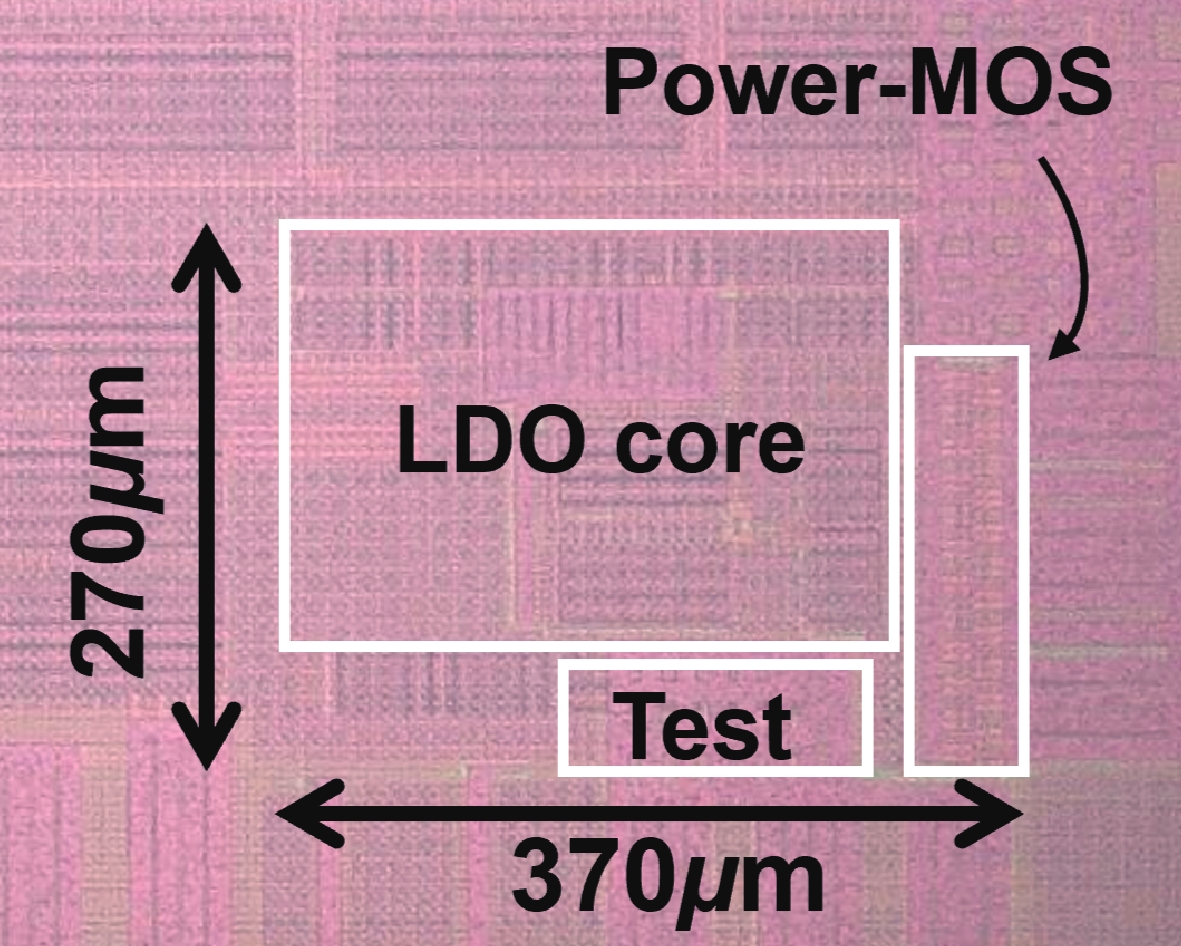

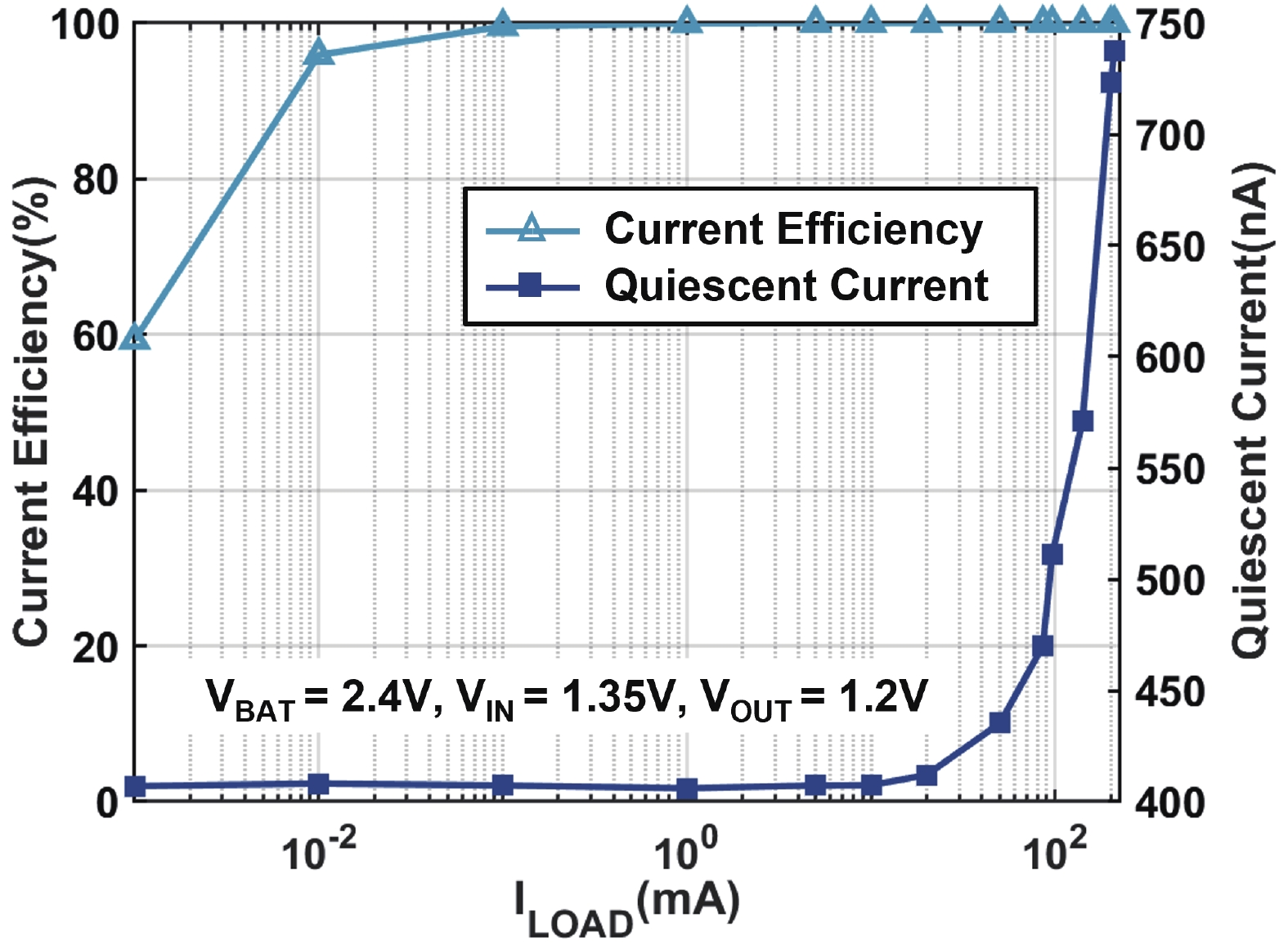

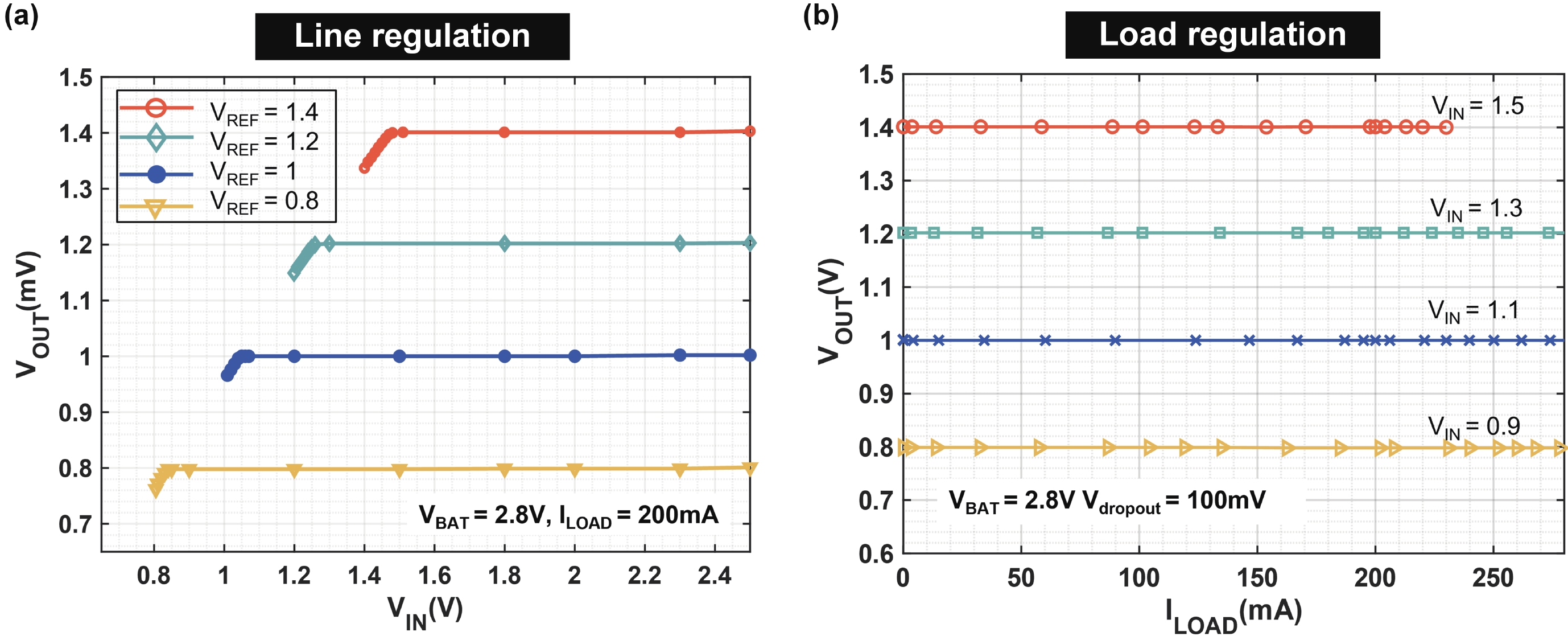

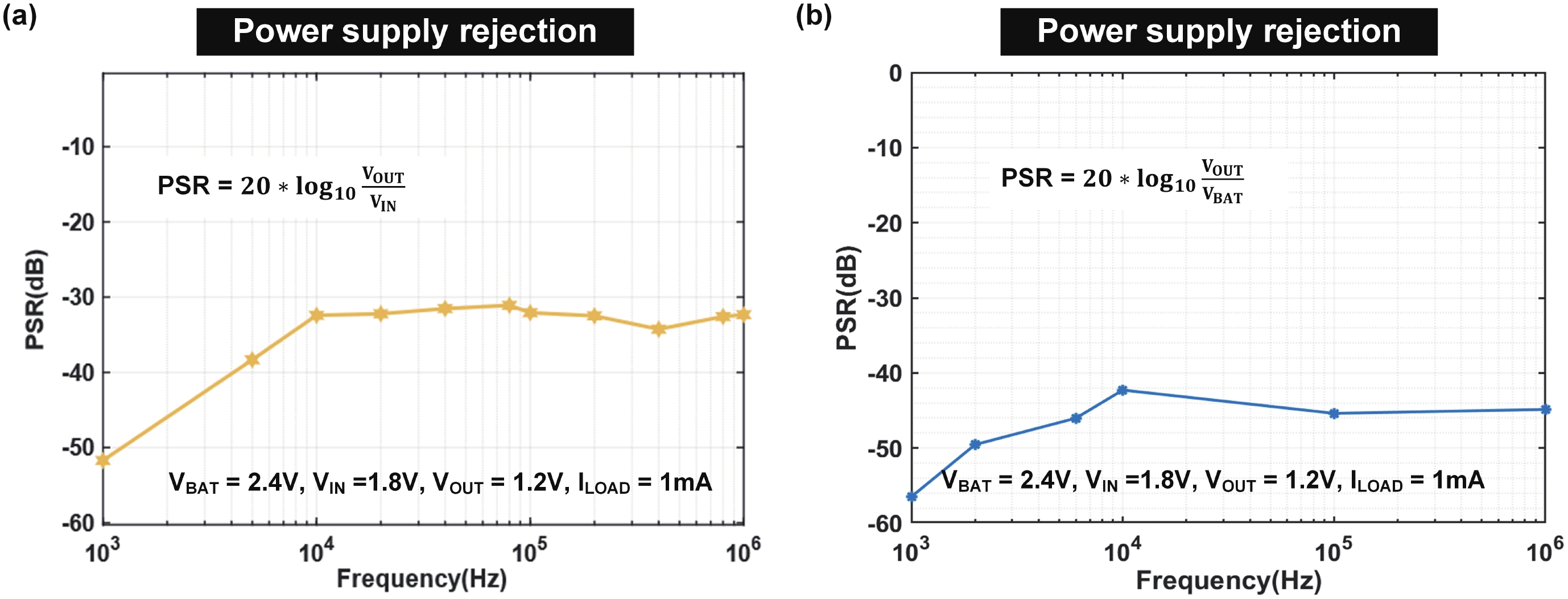

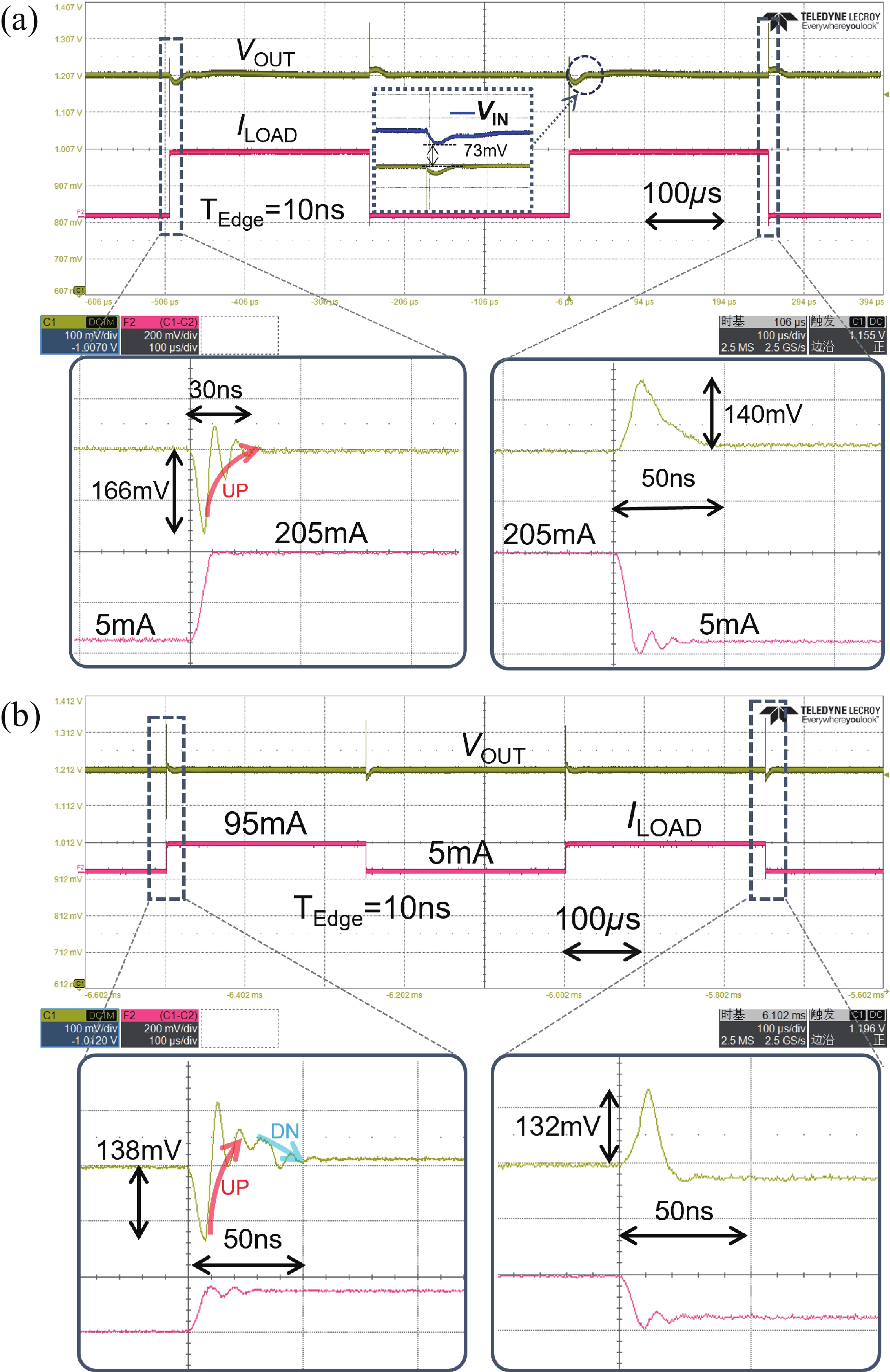

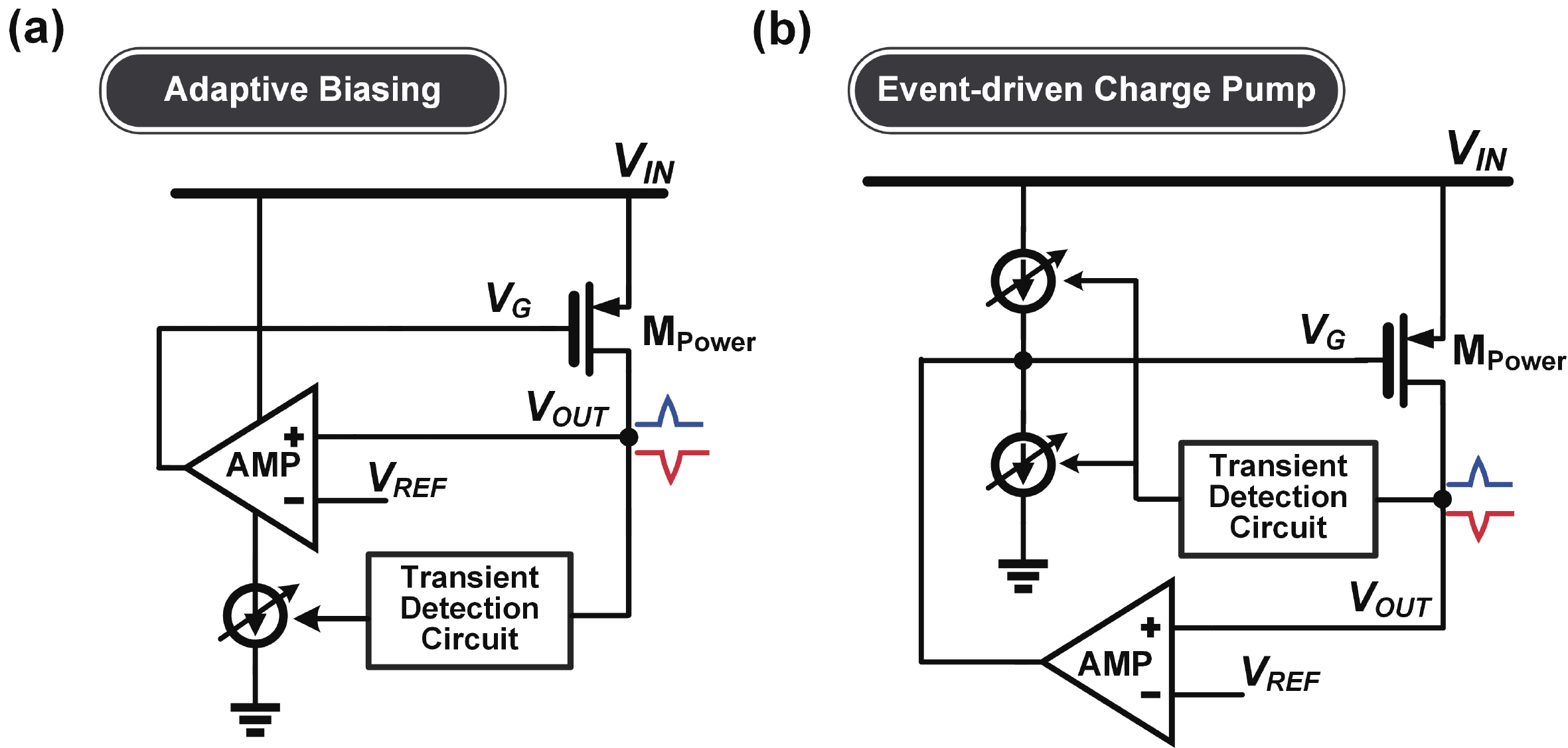

In this paper, an NMOS output-capacitorless low-dropout regulator (OCL-LDO) featuring dual-loop regulation has been proposed, achieving fast transient response with low power consumption. An event-driven charge pump (CP) loop with the dynamic strength control (DSC), is proposed in this paper, which overcomes trade-offs inherent in conventional structures. The presented design addresses and resolves the large signal stability issue, which has been previously overlooked in the event-driven charge pump structure. This breakthrough allows for the full exploitation of the charge-pump structure's potential, particularly in enhancing transient recovery. Moreover, a dynamic error amplifier is utilized to attain precise regulation of the steady-state output voltage, leading to favorable static characteristics. A prototype chip has been fabricated in 65 nm CMOS technology. The measurement results show that the proposed OCL-LDO achieves a 410 nA low quiescent current (IQ) and can recover within 30 ns under 200 mA/10 ns loading change. -

References

[1] Huang M, Lu Y, Martins R P. A comparative study of digital low dropout regulators. J Semicond, 2020, 41, 111405 doi: 10.1088/1674-4926/41/11/111405[2] Burd T D, Pering T A, Stratakos A J, et al. A dynamic voltage scaled microprocessor system. IEEE J Solid-State Circuits, 2000, 35, 1571 doi: 10.1109/4.881202[3] Man T Y, Mok P K T, Chan M S. A high slew-rate push–pull output amplifier for low-quiescent current low-dropout regulators with transient-response improvement. IEEE Trans Circuits Syst II Express Briefs, 2007, 54, 755 doi: 10.1109/TCSII.2007.900347[4] Lam Y H, Ki W H. A 0.9V 0.35 μm adaptively biased CMOS LDO regulator with fast transient response. 2008 IEEE International Solid-State Circuits Conference-Digest of Technical Papers. San Francisco, CA, USA. IEEE, 2008, 442 doi: 10.1109/ISSCC.2008.4523247[5] Ho M, Leung K N, Mak K L. A low-power fast-transient 90-nm low-dropout regulator with multiple small-gain stages. IEEE J Solid-State Circuits, 2010, 45, 2466 doi: 10.1109/JSSC.2010.2072611[6] Guo J P, Leung K N. A 6-μW chip-area-efficient output-capacitorless LDO in 90-nm CMOS technology. IEEE J Solid-State Circuits, 2010, 45, 1896 doi: 10.1109/JSSC.2010.2053859[7] Ming X, Li Q, Zhou Z K, et al. An ultrafast adaptively biased capacitorless LDO with dynamic charging control. IEEE Trans Circuits Syst II Express Briefs, 2012, 59, 40 doi: 10.1109/TCSII.2011.2177698[8] Lu Y, Wang Y P, Pan Q, et al. A fully-integrated low-dropout regulator with full-spectrum power supply rejection. IEEE Trans Circuits Syst I Regul Pap, 2015, 62, 707 doi: 10.1109/TCSI.2014.2380644[9] Lavalle-Aviles F, Torres J, Sánchez-Sinencio E. A high power supply rejection and fast settling time capacitor-less LDO. IEEE Trans Power Electron, 2019, 34, 474 doi: 10.1109/TPEL.2018.2826922[10] Maity A, Patra A. Tradeoffs aware design procedure for an adaptively biased capacitorless low dropout regulator using nested miller compensation. IEEE Trans Power Electron, 2016, 31, 369 doi: 10.1109/TPEL.2015.2398868[11] Huang Y Q, Lu Y, Maloberti F, et al. Nano-ampere low-dropout regulator designs for IoT devices. IEEE Trans Circuits Syst I Regul Pap, 2018, 65, 4017 doi: 10.1109/TCSI.2018.2851226[12] Mandal D, Desai C, Bakkaloglu B, et al. Adaptively biased output cap-less NMOS LDO with 19 ns settling time. IEEE Trans Circuits Syst II Express Briefs, 2019, 66, 167 doi: 10.1109/TCSII.2018.2842642[13] Li G X, Qian H M, Guo J P, et al. Dual active-feedback frequency compensation for output-capacitorless LDO with transient and stability enhancement in 65-nm CMOS. IEEE Trans Power Electron, 2020, 35, 415 doi: 10.1109/TPEL.2019.2910557[14] Cai G G, Lu Y, Zhan C C, et al. A fully integrated FVF LDO with enhanced full-spectrum power supply rejection. IEEE Trans Power Electron, 2021, 36, 4326 doi: 10.1109/TPEL.2020.3024595[15] Song Y, Oh J, Cho S Y, et al. A fast droop-recovery event-driven digital LDO with adaptive linear/binary two-step search for voltage regulation in advanced memory. IEEE Trans Power Electron, 2022, 37, 1189 doi: 10.1109/TPEL.2021.3103611[16] Hsu W Y, Aymerich J, Yang X L, et al. A 0-to-35mA NMOS capacitor-less LDO with dual-loop regulation achieving 3ns response time and 1pF-to-10nF loading range. ESSCIRC 2023-IEEE 49th European Solid State Circuits Conference (ESSCIRC), 2023, 253 doi: 10.1109/ESSCIRC59616.2023.10268699[17] Wang X Y, Mercier P P. A dynamically high-impedance charge-pump-based LDO with digital-LDO-like properties achieving a sub-4-fs FoM. IEEE J Solid-State Circuits, 2020, 55, 719 doi: 10.1109/JSSC.2019.2960004[18] Zhao J M, Gao Y, Zhang T T, et al. A 310-nA quiescent current 3-fs-FoM fully integrated capacitorless time-domain LDO with event-driven charge pump and feedforward transient enhancement. IEEE J Solid-State Circuits, 2021, 56, 2924 doi: 10.1109/JSSC.2021.3077453[19] Han W J, Lee H. A 340-nA-quiescent 80-mA-load 0.02-fs-FOM active-capacitor-based low-dropout regulator in standard 0.18-μm CMOS. IEEE Solid-State Circuits Lett, 2021, 4, 125 doi: 10.1109/LSSC.2021.3089975[20] Huang J R, Wen Y H, Yang T H, et al. A 10 nA ultra-low quiescent current and 60 ns fast transient response low-dropout regulator for internet-of-things. IEEE Trans Circuits Syst I Regul Pap, 2022, 69, 139 doi: 10.1109/TCSI.2021.3093057[21] Baochuang W. A low-power off-chip capacitorless linear regulator with fast transient response. China Patent, CN114460996B, 2023 (in Chinese)[22] Akram M A, Hong W, Hwang I C. Capacitorless self-clocked all-digital low-dropout regulator. IEEE J Solid-State Circuits, 2019, 54, 266 doi: 10.1109/JSSC.2018.2871039 -

Proportional views

Yiling Xie received the B.Eng. degree in microelectronic science and engineering in 2022 from the School of Electronics and Information Technology, Sun Yat-sen University, Guangzhou, China, where she is currently working toward the M.S. degree in integrated circuits. Her current research interests mainly include the design of power management integrated circuits design.

Yiling Xie received the B.Eng. degree in microelectronic science and engineering in 2022 from the School of Electronics and Information Technology, Sun Yat-sen University, Guangzhou, China, where she is currently working toward the M.S. degree in integrated circuits. Her current research interests mainly include the design of power management integrated circuits design. Baochuang Wang received the B.Eng. degree from School of Electronics and Information Technology, Sun Yat-sen University (SYSU), Guangzhou, China, in 2022. He is currently pursuing the M.S. degree with the School of Microelectronics, University of Science and Technology of China (USTC), Hefei, China. His current research interests mainly include power converter topologies and power management integrated circuits.

Baochuang Wang received the B.Eng. degree from School of Electronics and Information Technology, Sun Yat-sen University (SYSU), Guangzhou, China, in 2022. He is currently pursuing the M.S. degree with the School of Microelectronics, University of Science and Technology of China (USTC), Hefei, China. His current research interests mainly include power converter topologies and power management integrated circuits. Dihu Chen received the B.Sc. and M.Phil. degrees in semiconductor physics from Sichuan University, Chengdu, China, in 1986 and 1989, respectively, and the Ph.D. degree in solid-state electron from the Chinese University of Hong Kong, Hong Kong, in 2000. In 1989, he joined Sun Yat-sen University, Guangzhou, China, where he is a Professor and Vice Dean of the School of Electronics and Information Technology. His current research interests include electronic devices, IC design, and design methodology.

Dihu Chen received the B.Sc. and M.Phil. degrees in semiconductor physics from Sichuan University, Chengdu, China, in 1986 and 1989, respectively, and the Ph.D. degree in solid-state electron from the Chinese University of Hong Kong, Hong Kong, in 2000. In 1989, he joined Sun Yat-sen University, Guangzhou, China, where he is a Professor and Vice Dean of the School of Electronics and Information Technology. His current research interests include electronic devices, IC design, and design methodology. Jianping Guo received the B.Sc. and M.Sc. degrees from Xidian University, Xi’an, China, in 2003 and 2006, respectively, and the Ph.D. degree from the Chinese University of Hong Kong (CUHK), Hong Kong, in 2011, all in electronic engineering. From 2004 to 2007, he was with Xi’an Deheng Microelectronics Inc. as an IC designer. From 2011 to 2012, he was a Postdoctoral Research Fellow with the Department of Electronic Engineering, CUHK. In July 2012, he was with the Sun Yat-sen University, Guangzhou, China, where he is currently a Professor with the School of Electronics and Information Technology. His current research interests include the design of power-management ICs and analog/mixed-signal ICs for Lidar applications.

Jianping Guo received the B.Sc. and M.Sc. degrees from Xidian University, Xi’an, China, in 2003 and 2006, respectively, and the Ph.D. degree from the Chinese University of Hong Kong (CUHK), Hong Kong, in 2011, all in electronic engineering. From 2004 to 2007, he was with Xi’an Deheng Microelectronics Inc. as an IC designer. From 2011 to 2012, he was a Postdoctoral Research Fellow with the Department of Electronic Engineering, CUHK. In July 2012, he was with the Sun Yat-sen University, Guangzhou, China, where he is currently a Professor with the School of Electronics and Information Technology. His current research interests include the design of power-management ICs and analog/mixed-signal ICs for Lidar applications.

DownLoad:

DownLoad: