| Citation: |

Yongrui Zhao, Xinquan Lai. Novel bandgap-based under-voltage-lockout methods with high reliability[J]. Journal of Semiconductors, 2013, 34(10): 105008. doi: 10.1088/1674-4926/34/10/105008

****

Y R Zhao, X Q Lai. Novel bandgap-based under-voltage-lockout methods with high reliability[J]. J. Semicond., 2013, 34(10): 105008. doi: 10.1088/1674-4926/34/10/105008.

|

Novel bandgap-based under-voltage-lockout methods with high reliability

DOI: 10.1088/1674-4926/34/10/105008

More Information

-

Abstract

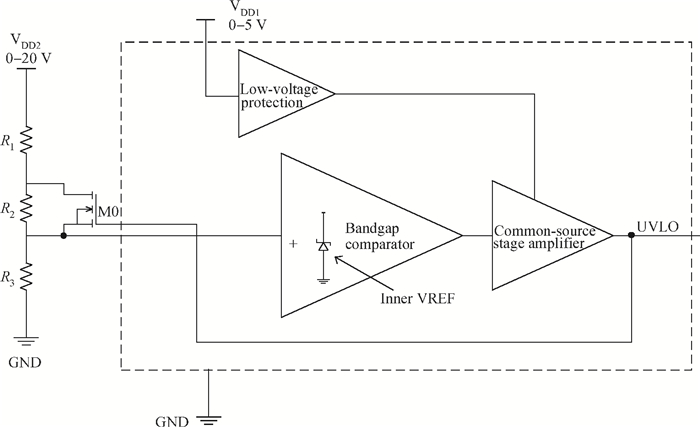

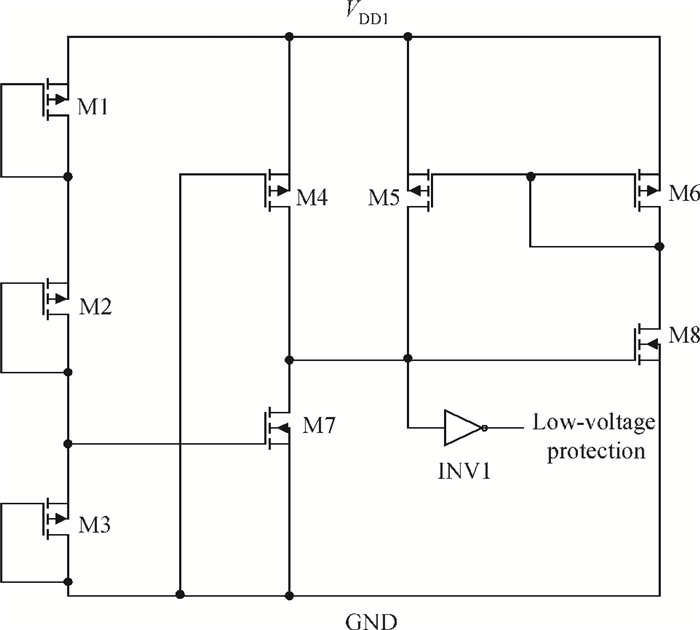

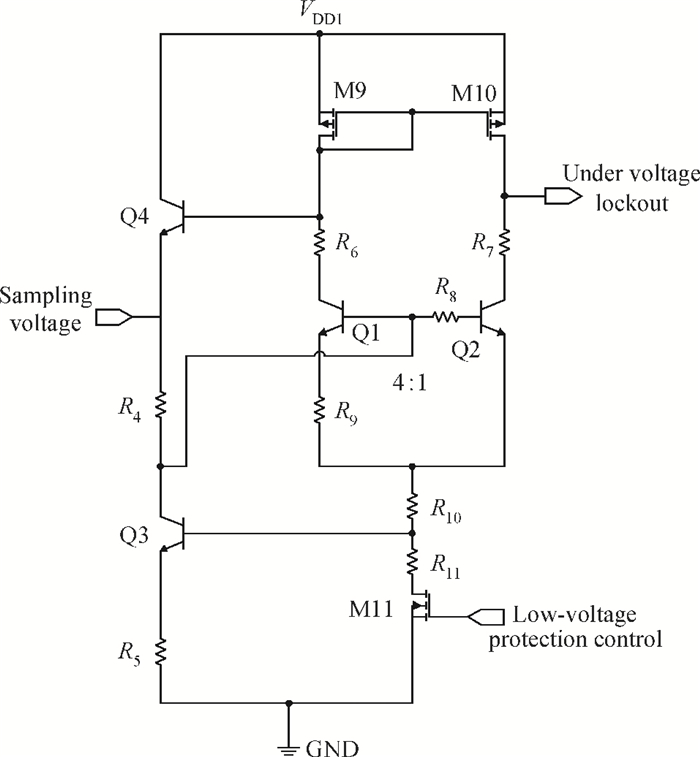

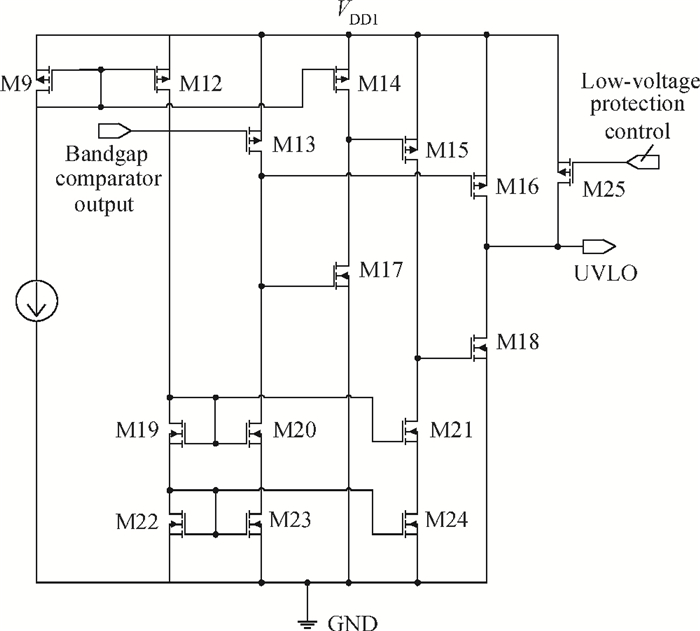

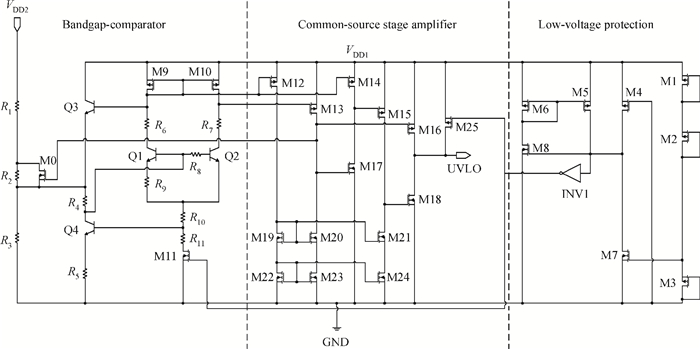

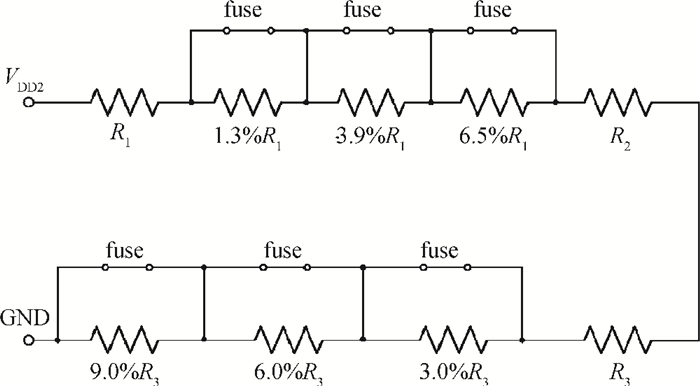

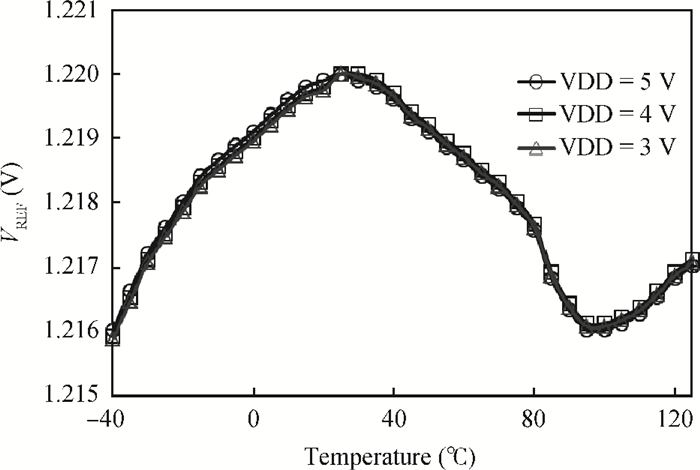

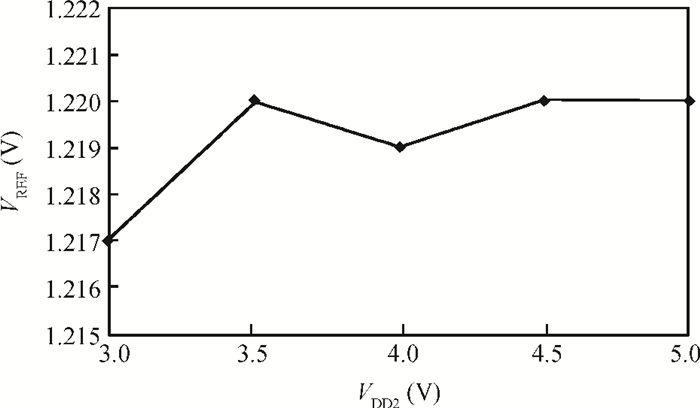

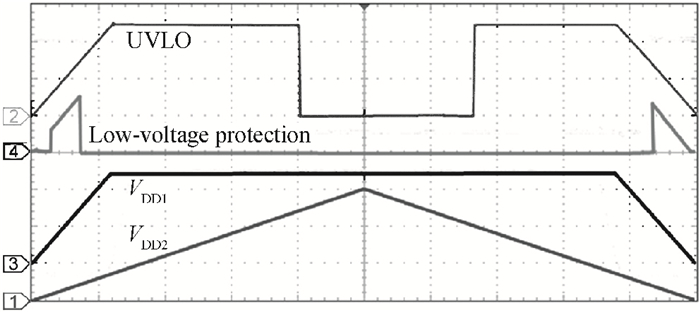

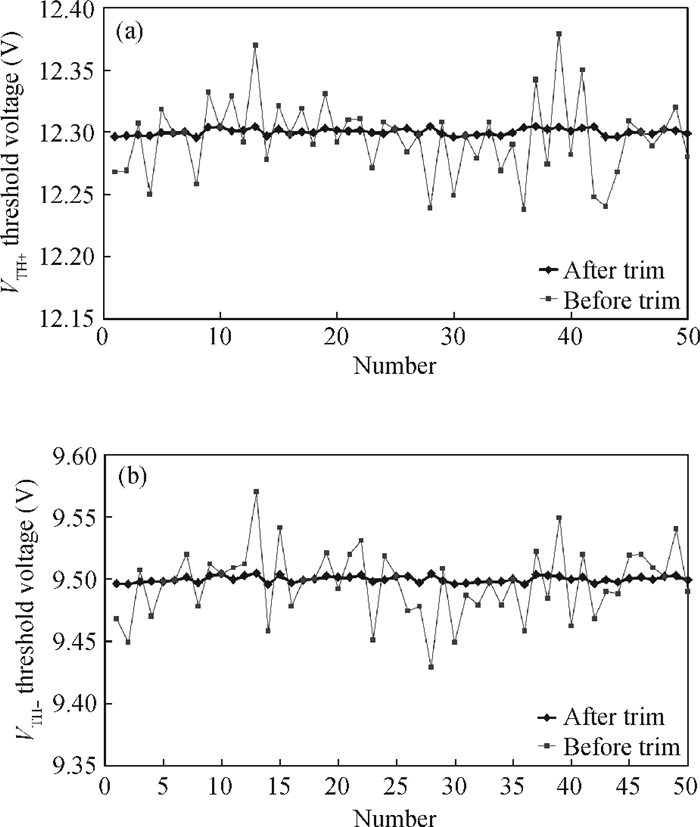

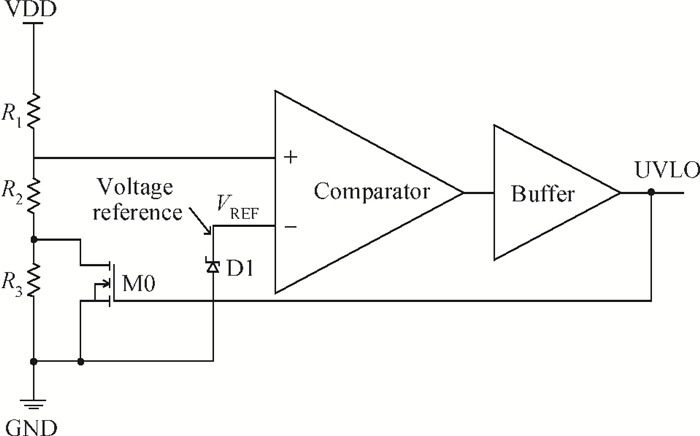

Highly reliable bandgap-based under-voltage-lockout (UVLO) methods are presented in this paper. The proposed under-voltage state to signal conversion methods take full advantages of the high temperature stability characteristics and the enhancement low-voltage protection methods which protect the core circuit from error operation; moreover, a common-source stage amplifier method is introduced to expand the output voltage range. All of these methods are verified in a UVLO circuit fabricated with a 0.5 μm standard BCD process technology. The experimental result shows that the proposed bandgap method exhibits a good temperature coefficient of 20 ppm/℃, which ensures that the UVLO keeps a stable output until the under-voltage state changes. Moreover, at room temperature, the high threshold voltage VTH+ generated by the UVLO is 12.3 V with maximum drift voltage of ±80 mV, and the low threshold voltage VTH- is 9.5 V with maximum drift voltage of ±70 mV. Also, the low voltage protection method used in the circuit brings a high reliability when the supply voltage is very low.-

Keywords:

- UVLO,

- bandgap-comparator,

- high reliability,

- high temperature stability

-

References

[1] Katiraei F, Iravani M R. Power management strategies for a microgrid with multiple distributed generation units. IEEE Trans Power Syst, 2006, 21(4):1821 doi: 10.1109/TPWRS.2006.879260[2] Kwak D K. Novel PFC AC-DC converter of high efficiency used in 2 kW fire electric installation. IEICE Electron Express, 2007, 4(1):1 doi: 10.1587/elex.4.1[3] Brohlin P L, Allen. Supply independent low quiescent current under voltage lockout circuit. US Patent, No. 6842321B2, 2005[4] Gariboldi R, Lacchiarella, Pulvirenti F. Circuit for generating a reference voltage and detecting an under voltage of a supply and corresponding method. US Patent, No. 5747978, 1998[5] Brokaw A P. A simple three-terminal IC bandgap reference. IEEE J Solid-State Circuits, 1974, 9(6):388 doi: 10.1109/JSSC.1974.1050532[6] Lai Xinquan, Hu Juncai, Jia Ligang, et al. Design of hysteretic comparator with bandgap structure. Proceedings of 5th International Conference on ASIC, 2003:615[7] Allen P E, Holberg D R. CMOS analog circuit design. 2nd ed. Oxford:Oxford University, 2002[8] Razavi B. Design of analog CMOS integrated circuits. New York:McGraw-Hill, 2003 http://catalog.lib.kyushu-u.ac.jp/recordID/1001200565[9] Mohammad R H, Simon S A. A CMOS Under-voltage lockout circuit. Proceedings of the World Congress on Engineering and Computer Science, San Francisco, USA, 2008:157 http://www.iaeng.org/publication/WCECS2008/WCECS2008_pp173-176.pdf[10] Nguyen T K, Kim C H, Ihm G J, et al. CMOS low-noise amplifier design optimization techniques. IEEE Trans Microw Theory Tech, 2004, 52(5):1433 doi: 10.1109/TMTT.2004.827014[11] Halpin S M, Harley K A, Jones R A, et al. Slope-permissive under-voltage load shed relay for delayed voltage recovery mitigation. IEEE Trans Power Syst, 2008, 23(3):1211 doi: 10.1109/TPWRS.2008.926409[12] Perry R T, Lewis S H, Brokaw A P. A 1.4 V supply CMOS fractional bandgap reference. IEEE J Solid-State Circuits, 2007, 42(10):2180 doi: 10.1109/JSSC.2007.905236[13] Leung N K, Mok P K T, Yat L C. A 2-V 23-μ A 5.3-ppm/℃ curvature-compensated CMOS bandgap voltage reference. IEEE J Solid-State Circuits, 2003, 38(3):561 doi: 10.1109/JSSC.2002.808328[14] Chavoshisani R, Hashemipour O. A high-speed current conveyor based current comparator. Microelectron J, 2011, 42(1):28 doi: 10.1016/j.mejo.2010.09.007[15] Lai X, Xu Z, Li Y, et al. A CMOS piecewise curvature-compensated voltage reference. Microelectron J, 2009, 40(1):39 doi: 10.1016/j.mejo.2008.09.006[16] Zhang C, Yang Z, Zhang Z. A CMOS hysteresis undervoltage lockout with current source inverter structure. IEEE 9th International Conference on ASIC (ASICON), 2011:918 http://ieeexplore.ieee.org/document/6157355/?arnumber=6157355[17] Li F, Wang W, Hang Q, et al. Design of a under voltage lock out circuit with bandgap structure. Proceedings of the 12th International Symposium on Integrated Circuits, 2009:224 http://ieeexplore.ieee.org/document/5403714/[18] Zhou Qingsheng, Wu Xiaobo. Design of novel under voltage lock out circuit. Microelectronics & Computer, 2006, 23(11):199(in Chinese) http://en.cnki.com.cn/Article_en/CJFDTOTAL-WXYJ200611059.htm[19] Zhao Fanglan, Feng Quanyuan, Gong Kunlin. An undervoltage lockout of hysteretic threshold of zero temperature coefficients. IEEE Asia-Pacific Microwave Conference Proceedings, 2005:153 http://ieeexplore.ieee.org/document/1606440/?reload=true&arnumber=1606440[20] Zhao Y, Lai X, Ye Q, et al. Timing circuit with preheating/ignition function in ballast ICs. Journal of Convergence Information Technology, 2012, 7(8):19 doi: 10.4156/jcit[21] He H, Lai X, Xu W, et al. High-speed gate driver with a simple structure for power MOSFET. Journal of Xidian University, 2012, 39(2):168(in Chinese) -

Proportional views

DownLoad:

DownLoad: