| Citation: |

Shuai Wang, Ke Li, Yibo Jiang, Mifang Cong, Huan Du, Zhengsheng Han. A thru-reflect-line calibration for measuring the characteristics of high power LDMOS transistors[J]. Journal of Semiconductors, 2013, 34(3): 034005. doi: 10.1088/1674-4926/34/3/034005

****

S Wang, K Li, Y B Jiang, M F Cong, H Du, Z S Han. A thru-reflect-line calibration for measuring the characteristics of high power LDMOS transistors[J]. J. Semicond., 2013, 34(3): 034005. doi: 10.1088/1674-4926/34/3/034005.

|

A thru-reflect-line calibration for measuring the characteristics of high power LDMOS transistors

DOI: 10.1088/1674-4926/34/3/034005

More Information

-

Abstract

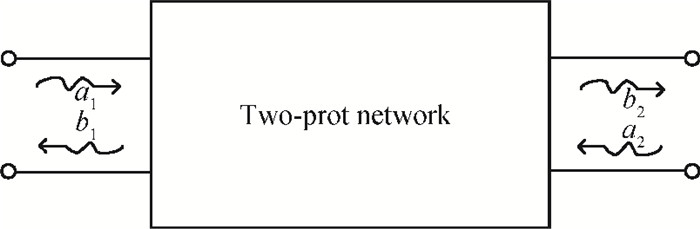

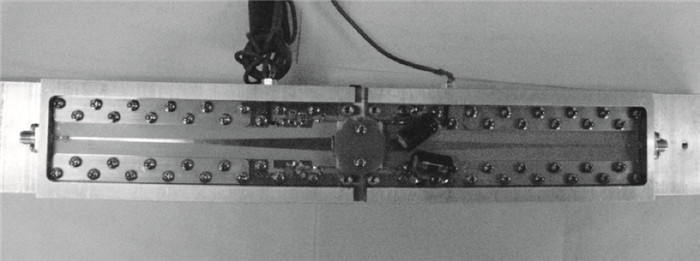

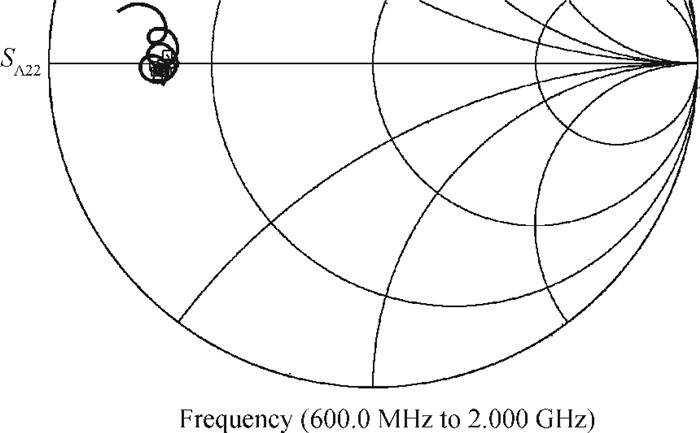

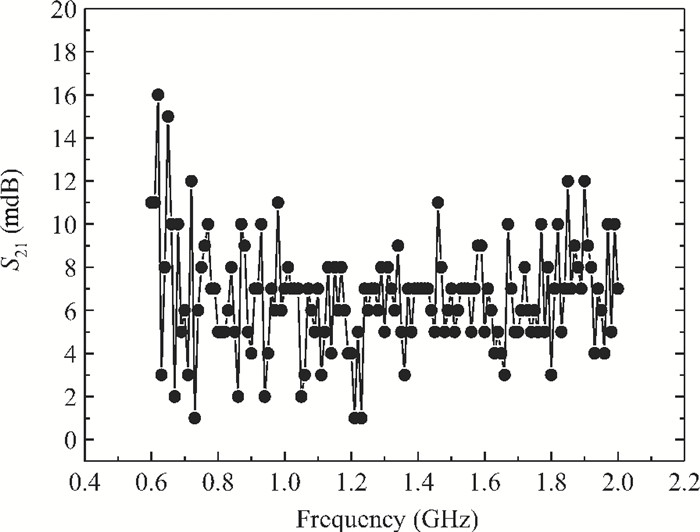

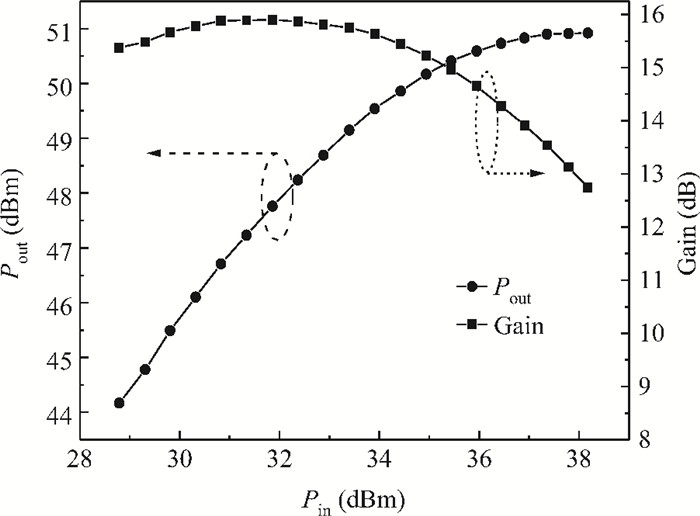

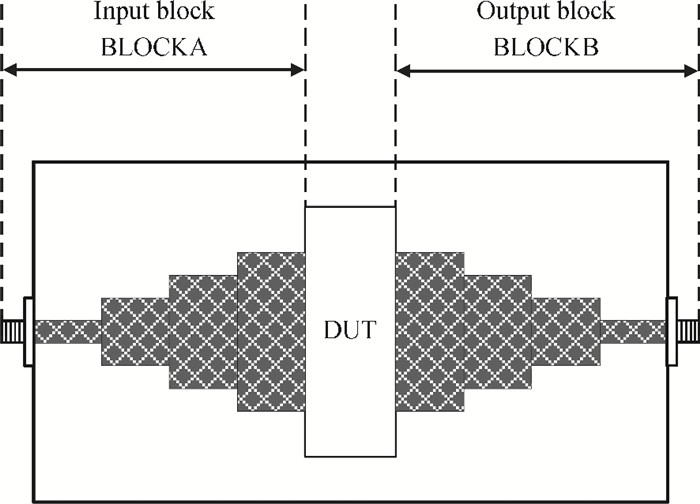

The impedance and output power measurements of LDMOS transistors are always a problem due to their low impedance and lead widths. An improved thru-reflect-line (TRL) calibration algorithm for measuring the characteristics of L-band high power LDMOS transistors is presented. According to the TRL algorithm, the individual two-port S parameters of each fixture half can be obtained. By de-embedding these S parameters of the test fixture, an accurate calibration can be made. The improved TRL calibration algorithm is successfully utilized to measure the characteristics of an L-band LDMOS transistor with a 90 mm gate width. The impedance of the transistor is obtained, and output power at 1 dB compression point can reach as much as 109.4 W at 1.2 GHz, achieving 1.2 W/mm power density. From the results, it is seen that the presented TRL calibration algorithm works well. -

References

[1] Ma R, Han G, Chen X, et al. Calibrating an arbitrary test fixture for a symmetric device by three measurements. IEEE Trans Instrumentation Measurement, 2010, 59(1):145 doi: 10.1109/TIM.2009.2022111[2] Engen G F, Hoer C A. Thru-reflect-line:an improved technique for calibrating the dual six-port automatic network analyzer. IEEE Trans Microw Theory Tech, 1979, 27(12):987 doi: 10.1109/TMTT.1979.1129778[3] Ludwig R, Bretchko P. RF circuit design:theory and applications. Upper Saddle River:Prentice-Hall, 2000 http://ci.nii.ac.jp/ncid/BA48143667[4] Aaen P, Pla J, Bridges D, et al. A wideband method for the rigorous low-impedance loadpull measurement of high-power transistors suitable for large-signal model validation. ARFTG Conference Digest-Fall, 2000, 38:1 http://ieeexplore.ieee.org/document/4120134/?reload=true&arnumber=4120134&contentType=Conference%20Publications[5] Bouny J J. Impedance measurements for high power RF transistors using the TRL method. Microwave Journal, 1999, 42(10):126[6] Aboush Z, Jones C, Knight G, et al. High power active harmonic load-pull system for characterization of high power 100-watt transistors. Microwave Conference, 2005, 1:4 http://ieeexplore.ieee.org/document/1608930/keywords[7] Pozar D M. Microwave engineering. 3rd ed. New York: John Wiley & Sons, 2005[8] Klopfenstein R W. A transmission line taper of improved design. Proc IRE, 1956, 44(1):31 doi: 10.1109/JRPROC.1956.274847[9] Shih C. Advanced TRL (through-reflect-line) fixture design and error analyses for RF high power transistor characterization and automatic load pull measurement. ARFTG Conference Digest-Spring, 1998, 33:72 http://ieeexplore.ieee.org/document/4119969/keywords -

Proportional views

DownLoad:

DownLoad: