| Citation: |

Xiaodan Guo, Qiao Meng, Yong Liang. A 4 GHz CMOS multiplier for sigma-delta modulated signals[J]. Journal of Semiconductors, 2014, 35(1): 015003. doi: 10.1088/1674-4926/35/1/015003

****

X D Guo, Q Meng, Y Liang. A 4 GHz CMOS multiplier for sigma-delta modulated signals[J]. J. Semicond., 2014, 35(1): 015003. doi: 10.1088/1674-4926/35/1/015003.

|

A 4 GHz CMOS multiplier for sigma-delta modulated signals

DOI: 10.1088/1674-4926/35/1/015003

More Information

-

Abstract

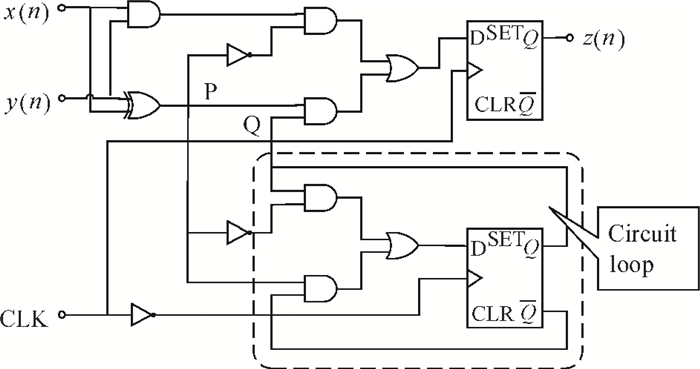

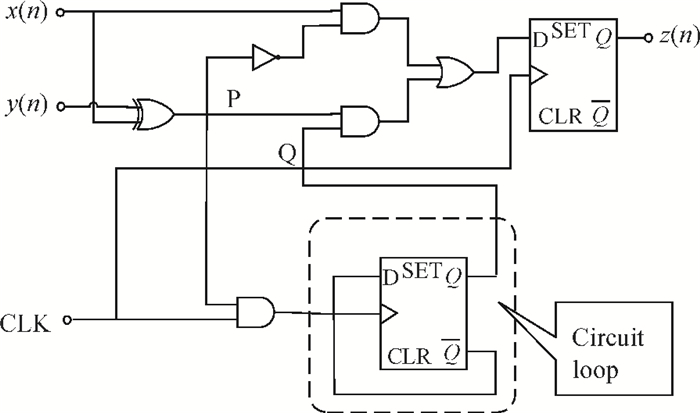

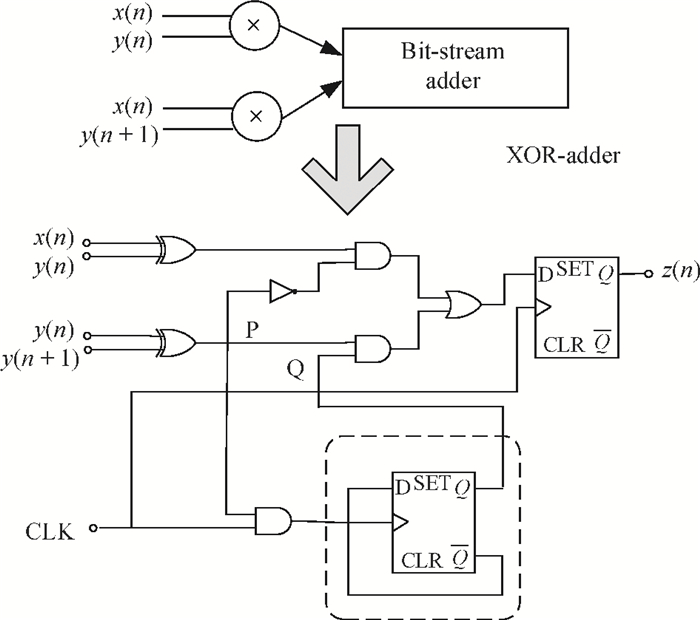

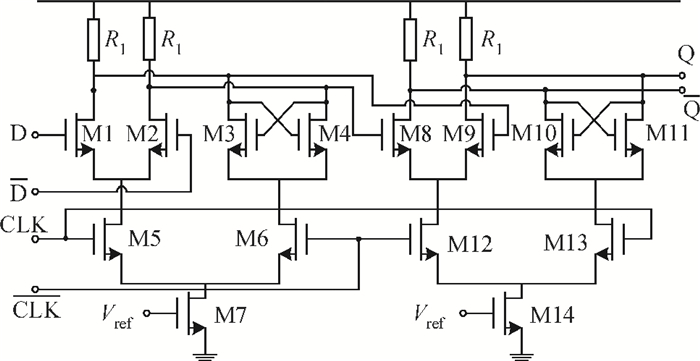

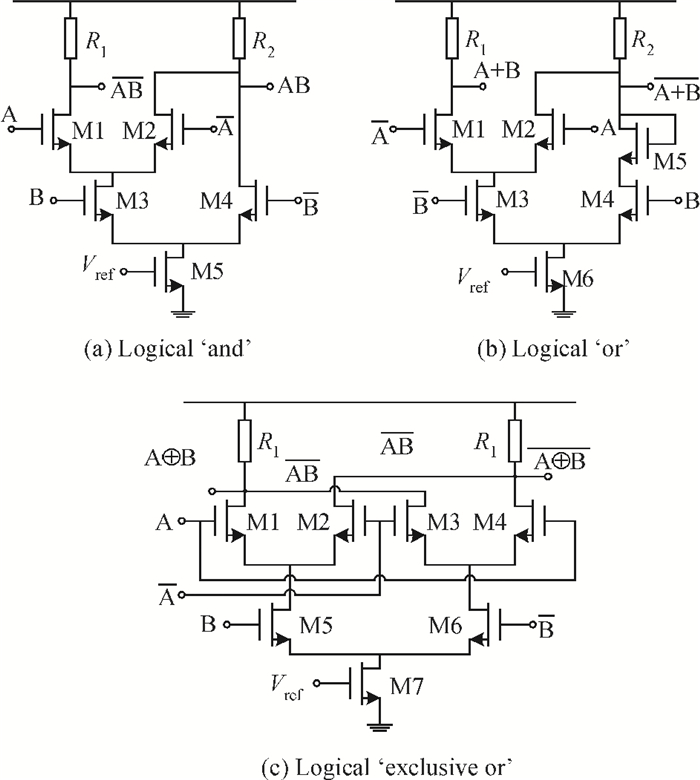

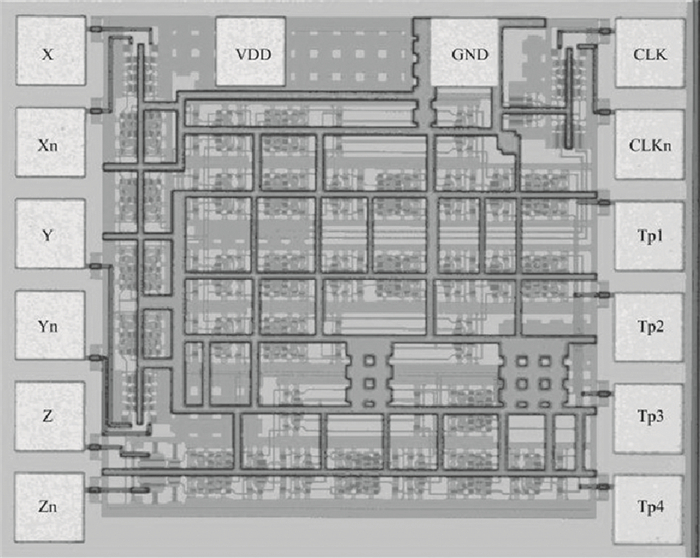

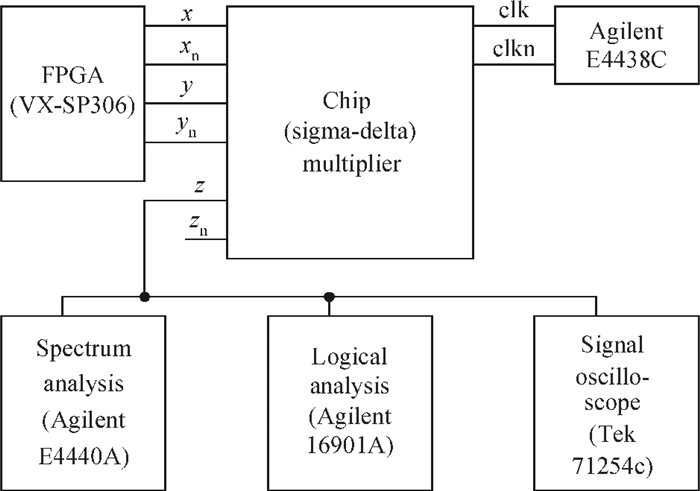

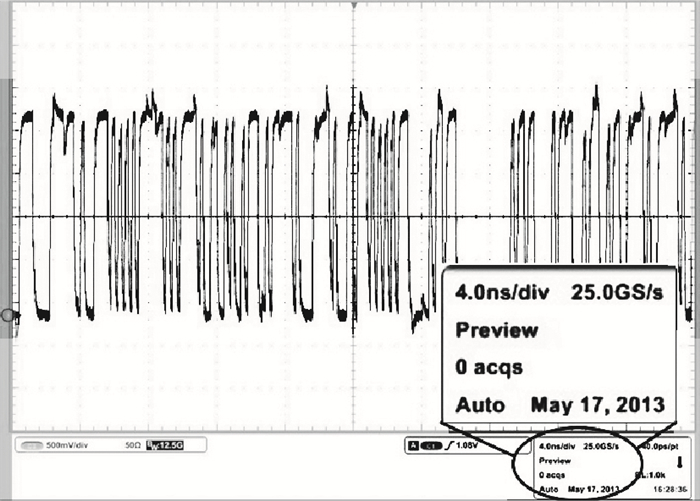

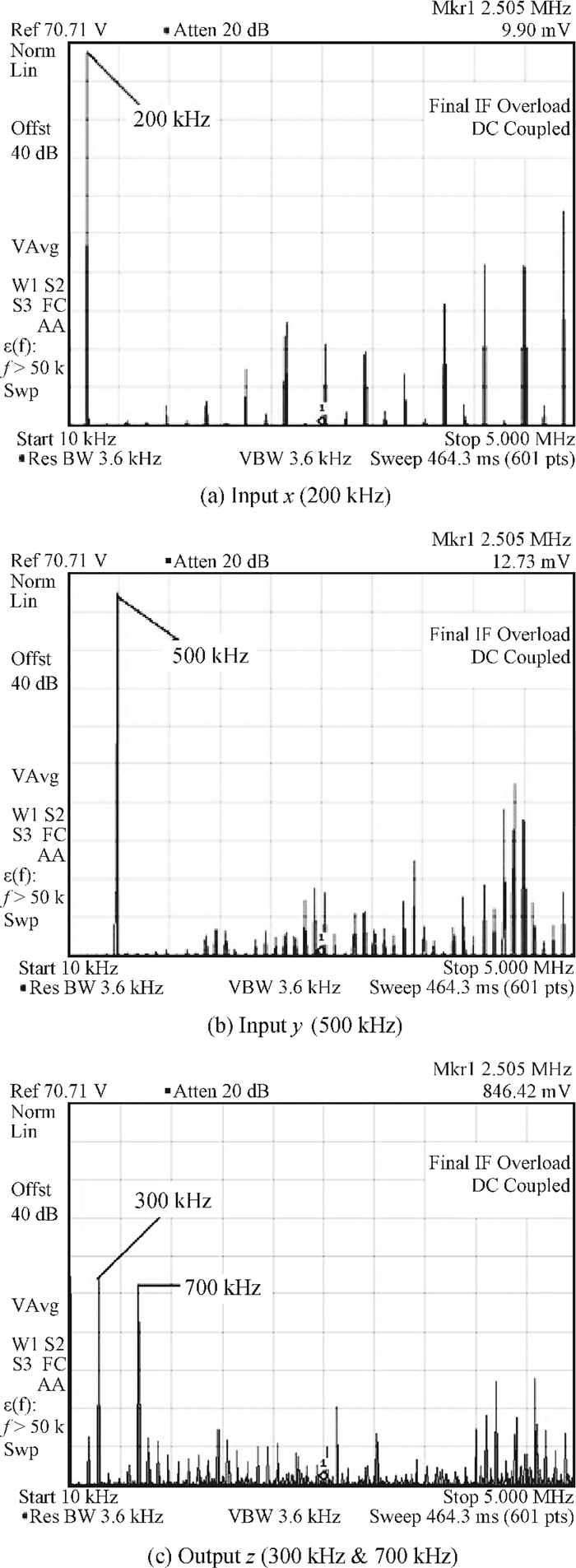

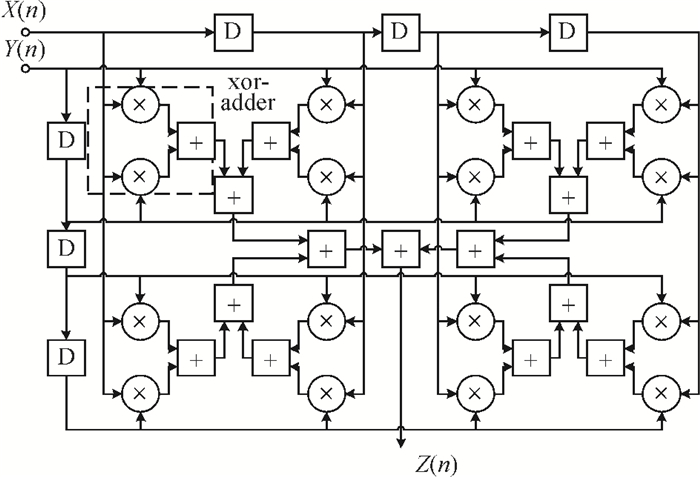

An integrated circuit design of a high speed multiplier for direct sigma-delta modulated bit-stream signals is presented. Compared with conventional structures, this multiplier reduces the circuit-loop delay of its sub-modules and works efficiently at a high speed. The multiplier's stability has also been improved with source coupled logic technology. The chip is fabricated in a TSMC 0.18-μm CMOS process. The test results demonstrate that the chip realizes the multiplication function and exhibits an excellent performance. It can work at 4 GHz and the voltage output amplitude reaches the designed maximum value with no error bit caused by logic race-and-hazard. Additionally, the analysis of the multiplier's noise performance is also presented.-

Keywords:

- CMOS,

- sigma-delta modulation,

- multiplier,

- bit-stream

-

References

[1] Fujisaka H, Kamio T, Ahn C J, et al. Sorter-based arithmetic circuits for sigma-delta domain signal processing-Part Ⅰ:addition, approximate transcendental functions, and log-domain operations. IEEE Trans Circuits Syst Ⅰ:Regular Papers, 2012, 59(9):1952 doi: 10.1109/TCSI.2011.2180451[2] Fujisaka H, Sakamoto M, Ahn C J, et al. Sorter-based arithmetic circuits for sigma-delta domain signal processing-Part Ⅱ:multiplication and algebraic functions. IEEE Trans Circuits Syst Ⅰ:Regular Papers, 2012, 59(9):1966 doi: 10.1109/TCSI.2011.2180450[3] Ng C W, Wong N, Ng T S. Efficient FPGA implementation of bit-stream multipliers. Electron Lett, 2007, 43(9):496 doi: 10.1049/el:20070293[4] Liang Y, Meng Q, Wang Z G, et al. Design of bit-stream neuron based on direct Σ-Δ signal process. IEEE International Conference on Wireless Communications & Signal Processing, 2009:1 http://ieeexplore.ieee.org/document/5371617/?reload=true&arnumber=5371617&contentType=Conference+Publications[5] Hart A, Voinigescu S P. A 1 GHz bandwidth low-pass ΔΣ ADC with 20-50 GHz adjustable sampling rate. IEEE J Solid-State Circuits, 2009, 44(5):1401 doi: 10.1109/JSSC.2009.2015852[6] Dagher E H, Stubberud P A, Masenten W K, et al. A 2-GHz analog-to-digital delta-sigma modulator for CDMA receivers with 79-dB signal-to-noise ratio in 1.23-MHz bandwidth. IEEE J Solid-State Circuits, 2004, 39(11):1819 doi: 10.1109/JSSC.2004.835831[7] Liang Y, Wang Z G, Meng Q, et al. 4 GHz bit-stream adder based on sigma-delta modulation. Journal of Semiconductors, 2010, 31(8):085001 doi: 10.1088/1674-4926/31/8/085001[8] Matic T, Svedek T, Herceg M. An analog multiplier based on asynchronous sigma-delta pulse amplitude modulation. IEEE 10th International Conference on Telecommunication in Modern Satellite Cable and Broadcasting Services (TELSIKS), 2011, 2:707[9] Zrilic D G. Circuit for multiplication of two sigma-delta modulated pulse streams. IEEE World Automation Congress (WAC), 2010:1 http://ieeexplore.ieee.org/document/5665424/authors[10] Fujisaka H, Kurata R, Sakamoto M, et al. Bit-stream signal processing and its application to communication systems. IEE Proceedings-Circuits, Devices and Systems, 2002, 149(3):159 doi: 10.1049/ip-cds:20020396[11] Alioto M, Palumbo G. Design strategies for source coupled logic gates. IEEE Trans Circuits Syst Ⅰ:Fundamental Theory and Applications, 2003, 50(5):640 doi: 10.1109/TCSI.2003.811023 -

Proportional views

DownLoad:

DownLoad: