| Citation: |

Jiaojiao Zhu, Xiaohua Luo, Lisheng Chen, Yi Ye, Xiaolang Yan. An improved shape shifting method of critical area extraction[J]. Journal of Semiconductors, 2014, 35(2): 026006. doi: 10.1088/1674-4926/35/2/026006

****

J J Zhu, X H Luo, L S Chen, Y Ye, X L Yan. An improved shape shifting method of critical area extraction[J]. J. Semicond., 2014, 35(2): 026006. doi: 10.1088/1674-4926/35/2/026006.

|

An improved shape shifting method of critical area extraction

DOI: 10.1088/1674-4926/35/2/026006

More Information

-

Abstract

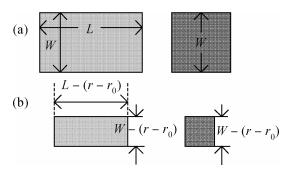

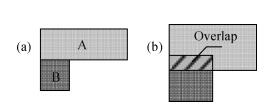

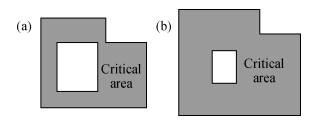

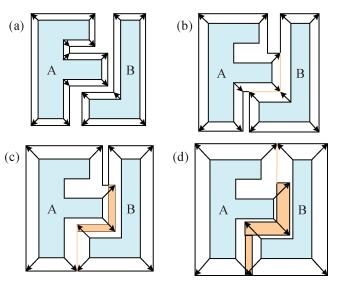

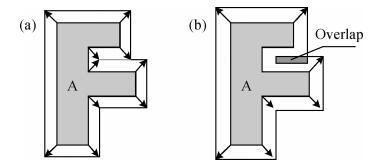

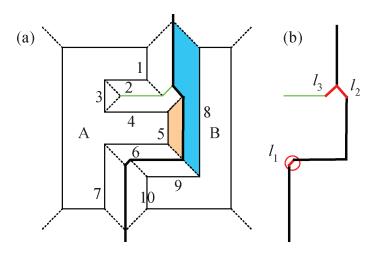

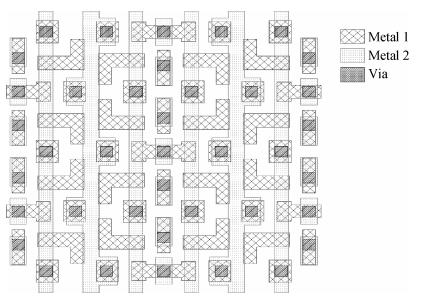

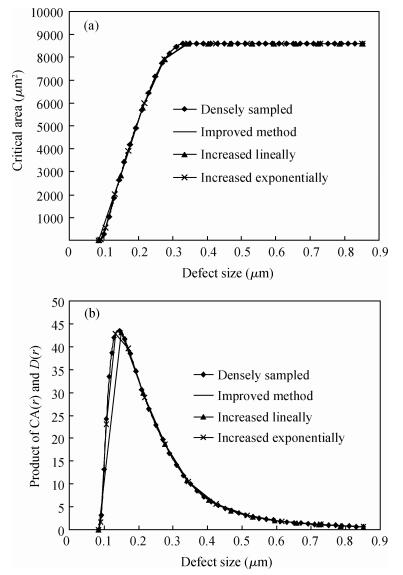

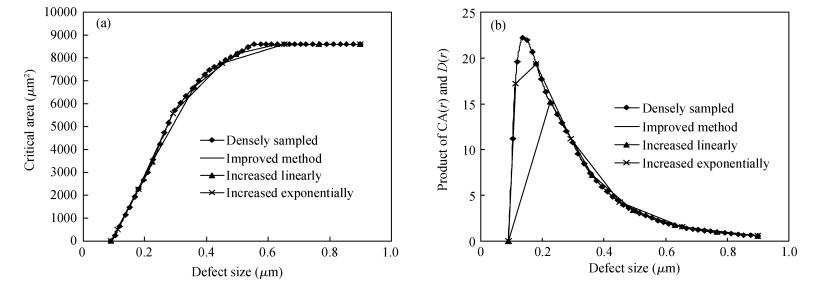

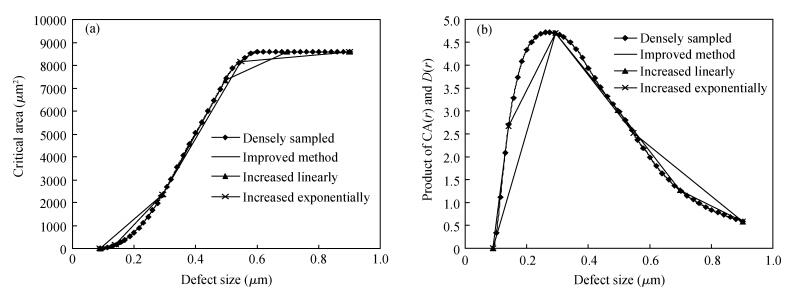

As die size and complexity increase, accurate and efficient extraction of the critical area is essential for yield prediction. Aiming at eliminating the potential integration errors of the traditional shape shifting method, an improved shape shifting method is proposed for Manhattan layouts. By mathematical analyses of the relevance of critical areas to defect sizes, the critical area for all defect sizes is modeled as a piecewise quadratic polynomial function of defect size, which can be obtained by extracting critical area for some certain defect sizes. Because the improved method calculates critical areas for all defect sizes instead of several discrete values with traditional shape shifting method, it eliminates the integration error of the average critical area. Experiments on industrial layouts show that the improved shape shifting method can improve the accuracy of the average critical area calculation by 24.3% or reduce about 59.7% computational expense compared with the traditional method. -

References

[1] Ghaida R S, Doniger K, Zarkesh-ha P. Random yield prediction based on a stochastic layout sensitivity model. IEEE Trans Semicond Manuf, 2009, 22(3):329 doi: 10.1109/TSM.2009.2024821[2] Allan G A, Walton A J. Efficient extra material critical area algorithms. IEEE Trans Computer-Aided Design of Integrated Circuits and Systems, 1999, 18(10):1480 doi: 10.1109/43.790624[3] Long C, Maynard D, Bjornsen M A. Technology assessment of commercially available critical area extraction tools. IEEE Advanced Semiconductor Manufacturing Conference and Workshop, 2000:76 http://ieeexplore.ieee.org/document/902562/[4] Walker H, Stephen W. VLASIC:a catastrophic fault yield simulator for integrated circuits. IEEE Trans Computer-Aided Design of Integrated Circuits and Systems, 1986, CAD-5(4):541 http://ieeexplore.ieee.org/document/1270225/[5] Allan G. Efficient critical area estimation for arbitrary defect shapes. Defect and Fault Tolerance in VLSI, 1997:20 http://ieeexplore.ieee.org/document/628305/[6] Maynard D N, Hibbeler J D. Measurement and reduction of critical area using Voronoi diagrams. IEEE/SEMI Conference and Workshop on Advanced Semiconductor Manufacturing, 2005:243[7] Papadopoulou E. Net-aware critical area extraction for opens in VLSI circuits via higher-order Voronoi diagrams. IEEE Trans Computer-Aided Design of Integrated Circuits and Systems, 2011, 30(5):704 doi: 10.1109/TCAD.2010.2100550[8] E Papadopoulou, D T Lee. Critical area computation via Voronoi diagrams. IEEE Trans Computer-Aided Design of Integrated Circuits and Systems, 1999, 18(4):463 doi: 10.1109/43.752929[9] Chiang C, Kawa J. Design for manufacturability and yield for nano-scale CMOS. Springer, 2007:25[10] Dalal A, Franzon P. A layout-driven yield predictor and fault generator for VLSI. IEEE Trans Semicond Manuf, 1993, 6(1):77 doi: 10.1109/66.210661[11] Ouyang C H, Pleskacz W A, Maly W. Extraction of critical areas for opens in large VLSI circuits. IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, 1996:21[12] Pleskacz W A, Ouyang C H, Maly W. A DRC-based algorithm for extraction of critical areas for opens in large VLSI circuits. IEEE Trans Computer-Aided Design of Integrated Circuits and Systems, 1999, 18(2):151 doi: 10.1109/43.743724[13] Dalal A R, Franzon P D, Lorenzetti M J. A layout-driven yield predictor and fault generator for VLSI. IEEE Trans Semicond Manuf, 1993, 6(1):77 doi: 10.1109/66.210661[14] Papadopoulou E. Critical area computation for missing material defects in VLSI circuits. IEEE Trans Computer-Aided Design of Integrated Circuits and Systems, 2001, 20(5):583 doi: 10.1109/43.920683[15] Allan G. Yield prediction by sampling IC layout. Computer-Aided Design of Integrated Circuits and System, 2000, 30:704 -

Proportional views

DownLoad:

DownLoad: