| Citation: |

Jianxin Li, Fujun Huang, Yong Zong, Jing Gao. High-stage analog accumulator for TDI CMOS image sensors[J]. Journal of Semiconductors, 2016, 37(2): 025001. doi: 10.1088/1674-4926/37/2/025001

****

J X Li, F J Huang, Y Zong, J Gao. High-stage analog accumulator for TDI CMOS image sensors[J]. J. Semicond., 2016, 37(2): 025001. doi: 10.1088/1674-4926/37/2/025001.

|

High-stage analog accumulator for TDI CMOS image sensors

DOI: 10.1088/1674-4926/37/2/025001

More Information

-

Abstract

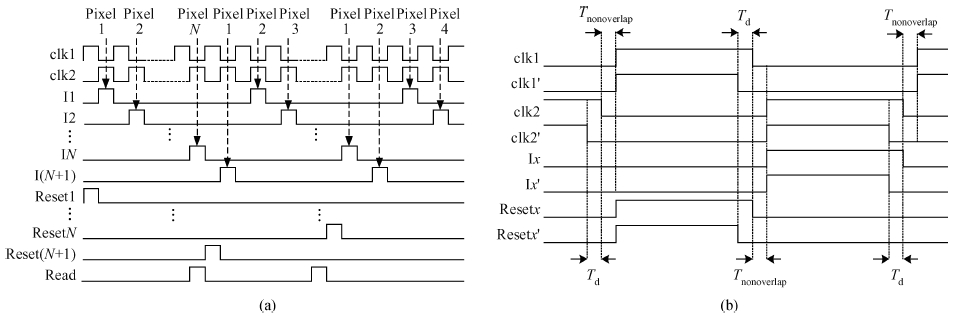

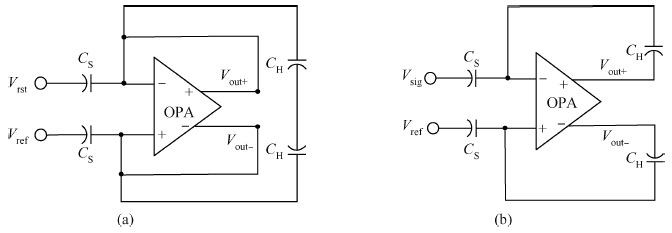

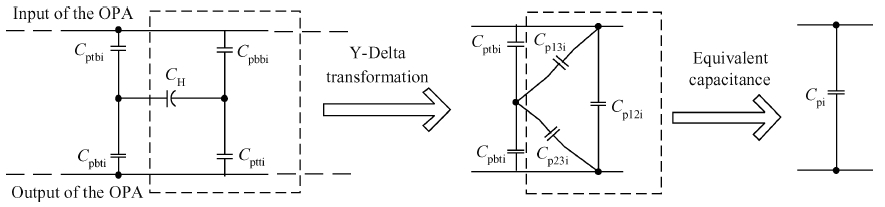

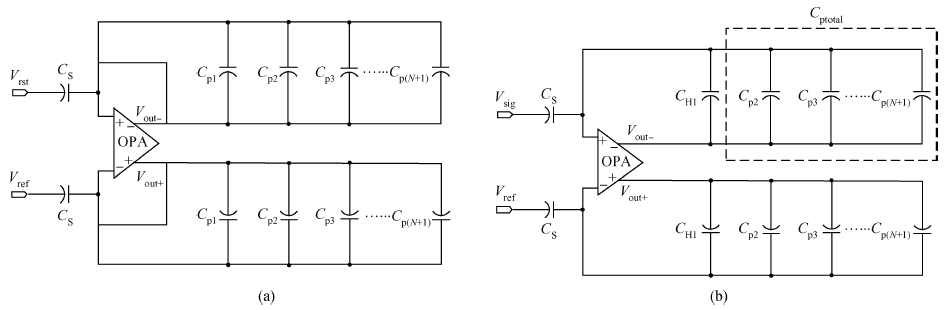

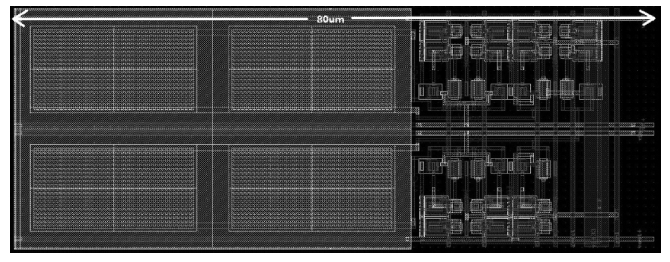

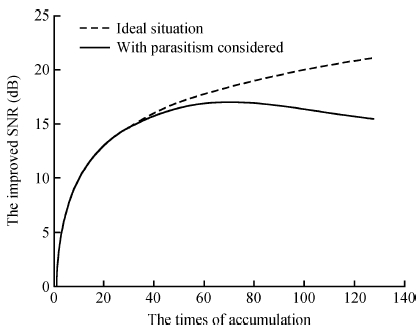

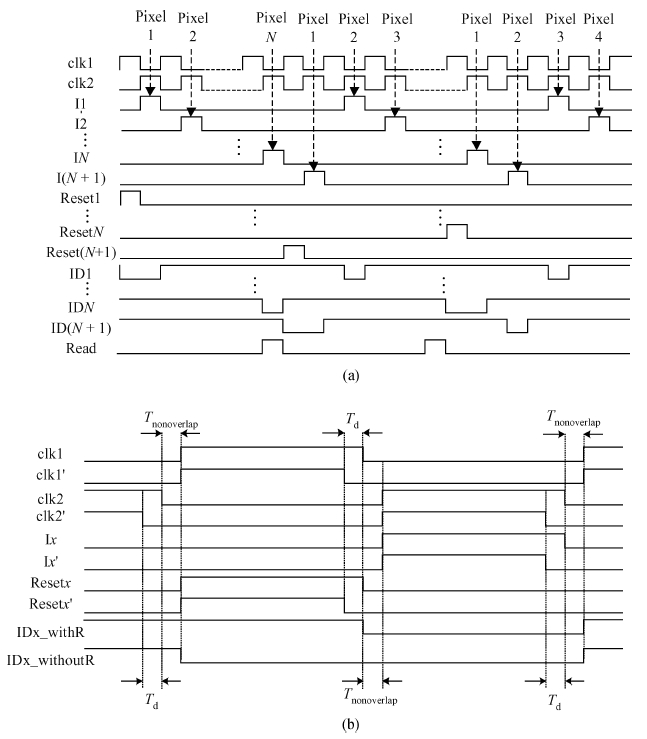

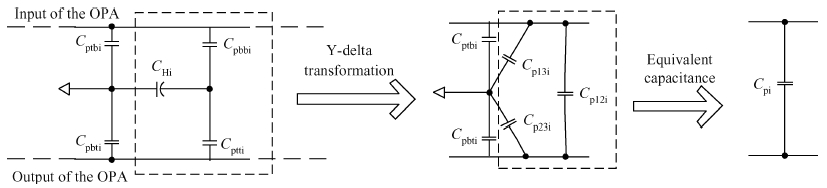

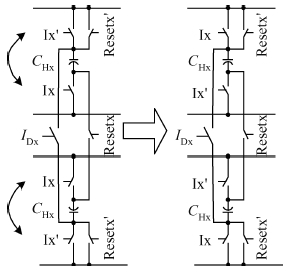

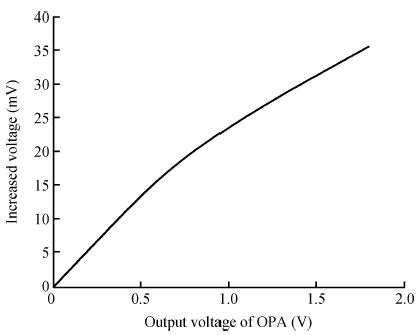

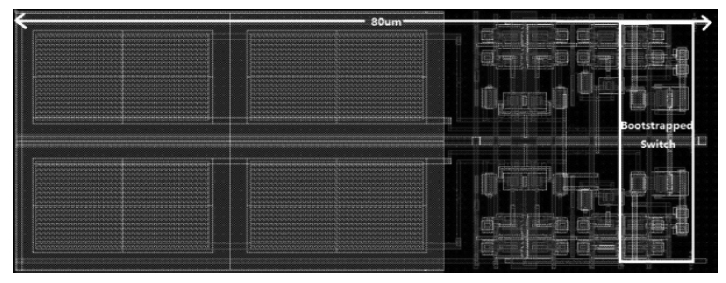

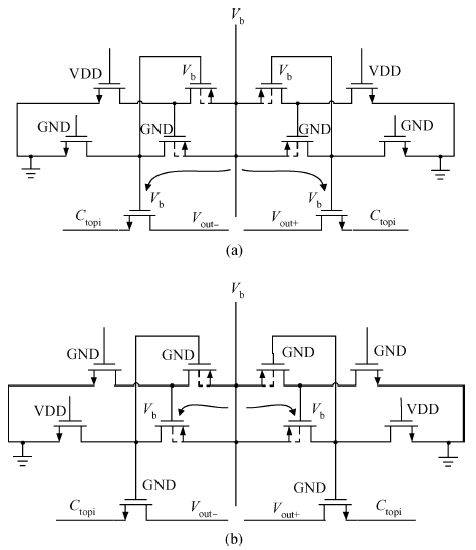

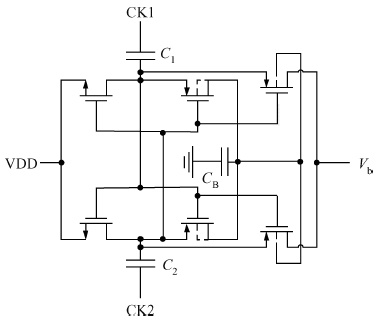

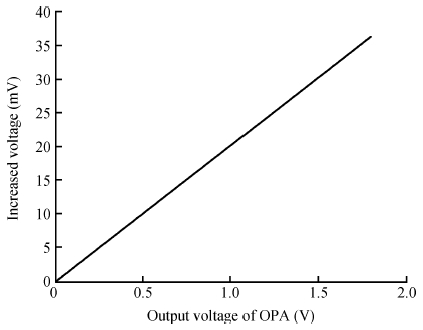

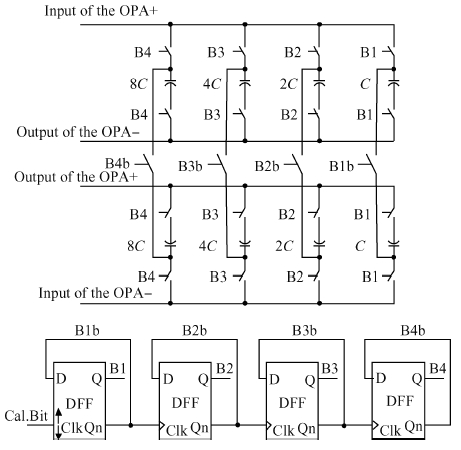

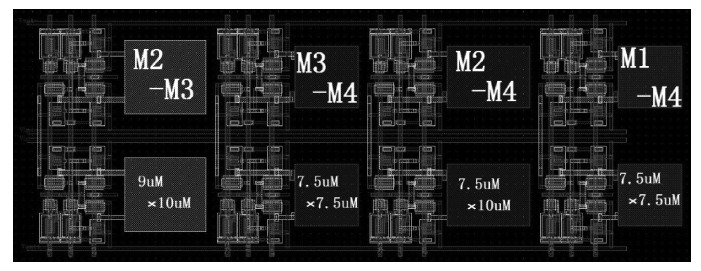

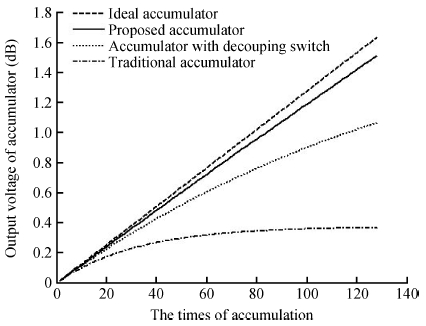

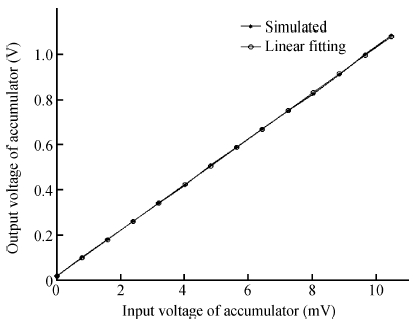

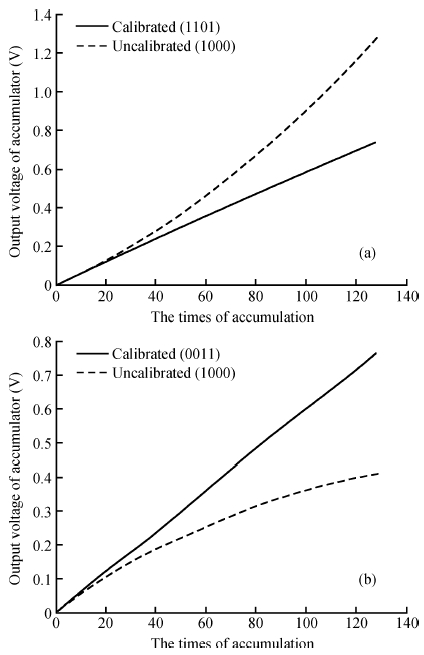

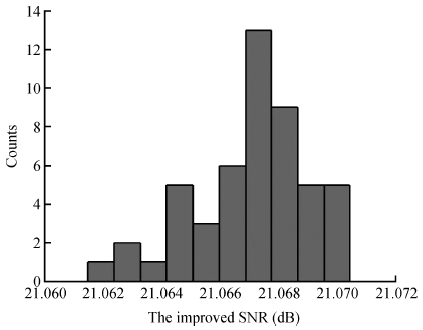

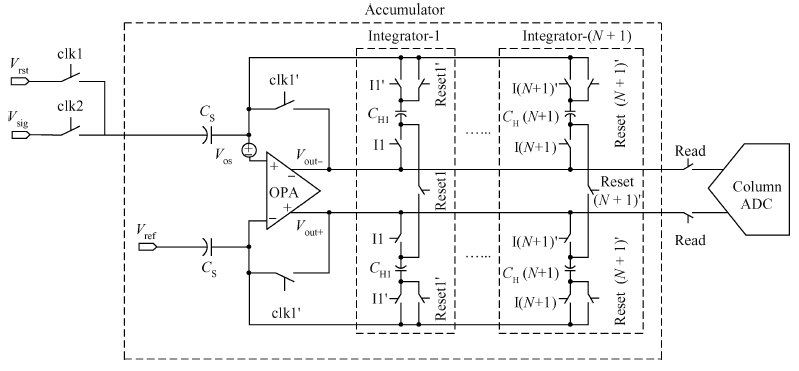

The impact of the parasitic phenomenon on the performance of the analog accumulator in TDI CMOS image sensor is analyzed and resolved. A 128-stage optimized accumulator based on 0.18-μ m one-poly four-metal 3.3 V CMOS technology is designed and simulated. A charge injection effect from the top plate sampling is employed to compensate the un-eliminated parasitics based on the accumulator with a decoupling switch, and then a calibration circuit is designed to restrain the mismatch and Process, Voltage and Temperature (PVT) variations. The post layout simulation indicates that the improved SNR of the accumulator upgrades from 17.835 to 21.067 dB, while an ideal value is 21.072 dB. In addition, the linearity of the accumulator is 99.62%. The simulation results of two extreme cases and Monte Carlo show that the mismatch and PVT variations are restrained by the calibration circuit. Furthermore, it is promising to design a higher stage accumulator based on the proposed structure. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] -

Proportional views

DownLoad:

DownLoad: