| Citation: |

Xin Jing, Yiqi Zhuang, Hualian Tang, Li Dai, Yongqian Du, Li Zhang, Hongbo Duan. A power-efficient 12-bit analog-to-digital converter with a novel constant-resistance CMOS input sampling switch[J]. Journal of Semiconductors, 2014, 35(2): 025002. doi: 10.1088/1674-4926/35/2/025002

****

X Jing, Y Q Zhuang, H L Tang, L Dai, Y Q Du, L Zhang, H B Duan. A power-efficient 12-bit analog-to-digital converter with a novel constant-resistance CMOS input sampling switch[J]. J. Semicond., 2014, 35(2): 025002. doi: 10.1088/1674-4926/35/2/025002.

|

A power-efficient 12-bit analog-to-digital converter with a novel constant-resistance CMOS input sampling switch

DOI: 10.1088/1674-4926/35/2/025002

More Information

-

Abstract

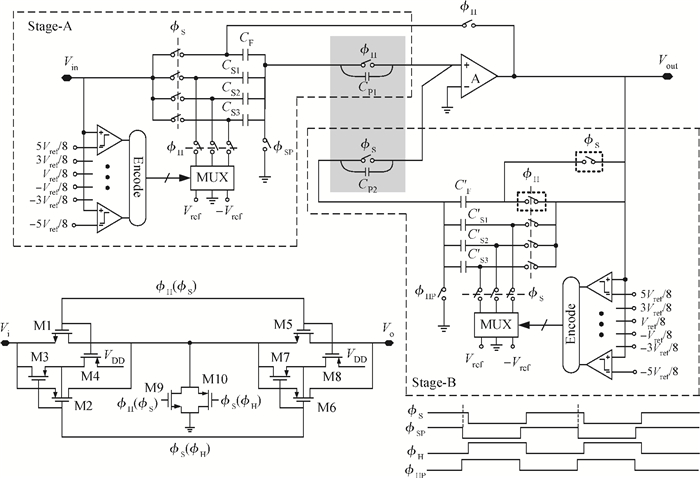

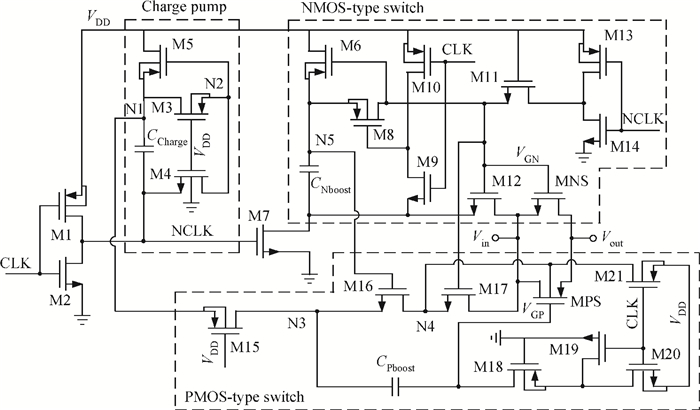

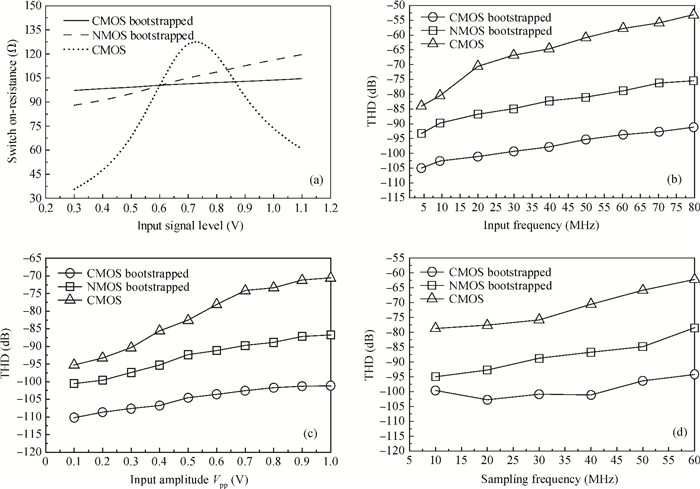

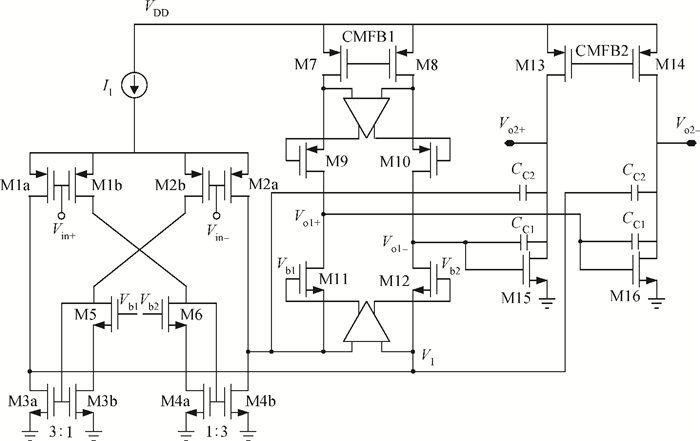

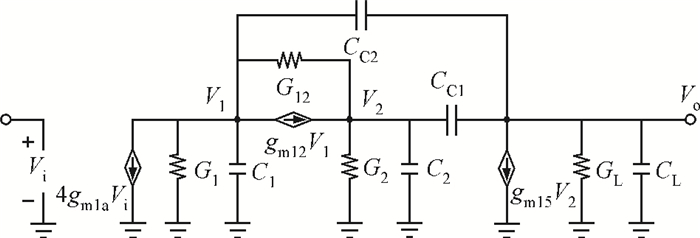

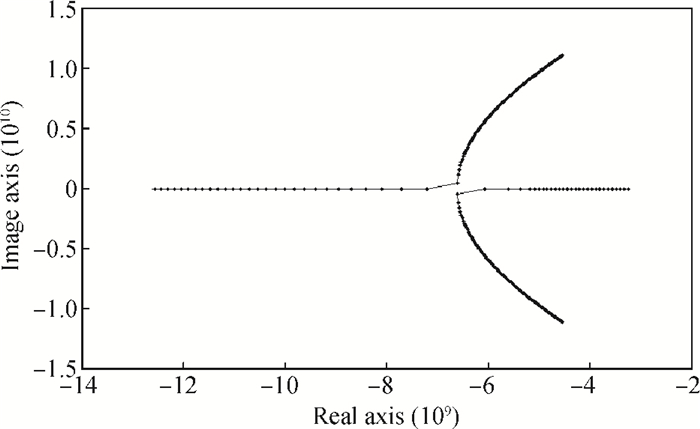

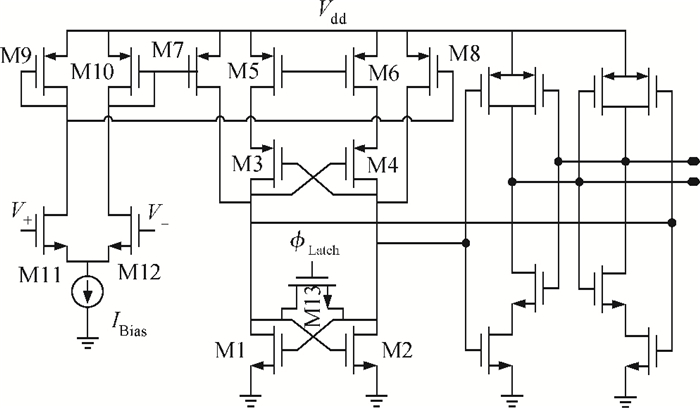

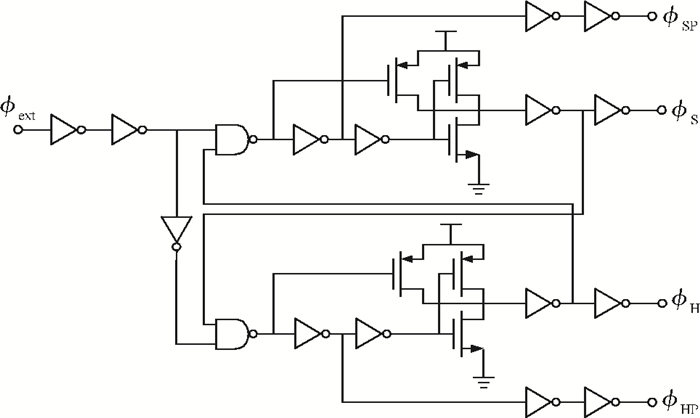

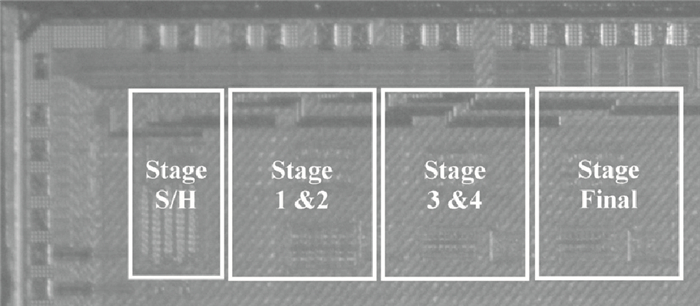

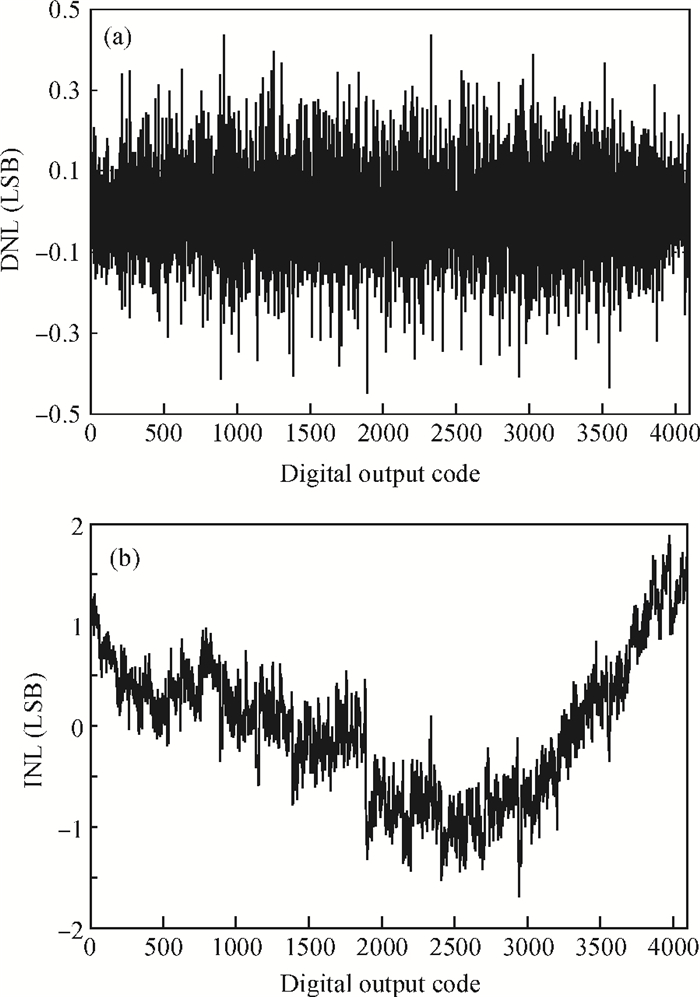

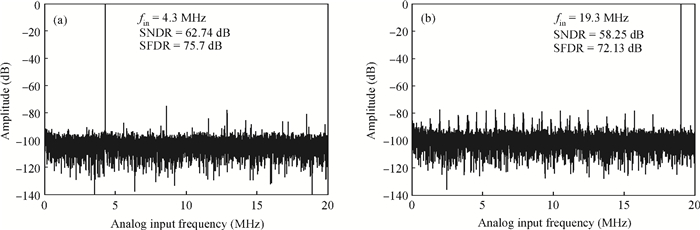

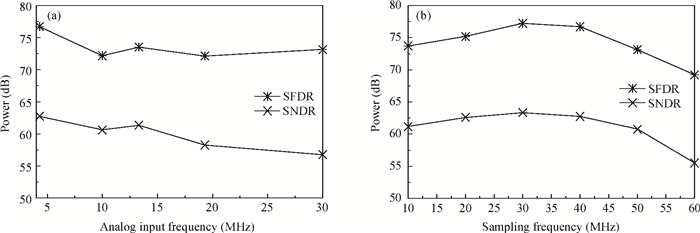

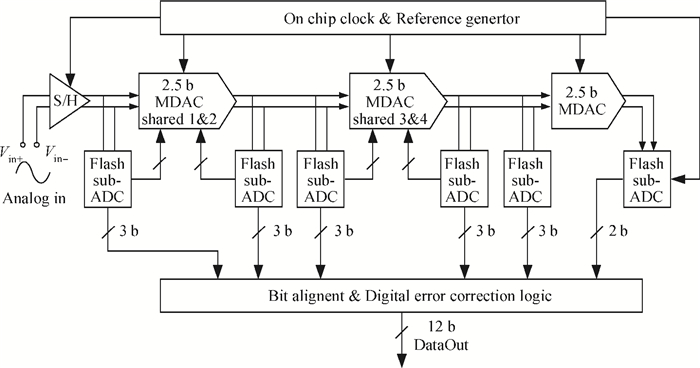

A power-efficient 12-bit 40-MS/s pipeline analog-to-digital converter (ADC) implemented in a 0.13 μm CMOS technology is presented. A novel CMOS bootstrapping switch, which offers a constant on-resistance over the entire input signal range, is used at the sample-and-hold front-end to enhance the dynamic performance of the pipelined ADC. By implementing with 2.5-bit-per-stage and a simplified amplifier sharing architecture between two successive pipeline stages, a very competitive power consumption and small die area can be achieved. Meanwhile, the substrate-biasing-effect attenuated T-type switches are introduced to reduce the crosstalk between the two op-amp sharing successive stages. Moreover, a two-stage gain boosted recycling folded cascode (RFC) amplifier with hybrid frequency compensation is developed to further reduce the power consumption and maintain the ADC's performance simultaneously. The measured results imply that the ADC achieves a spurious-free dynamic range (SFDR) of 75.7 dB and a signal-to-noise-plus-distortion ratio (SNDR) of 62.74 dB with a 4.3 MHz input signal; the SNDR maintains over 58.25 dB for input signals up to 19.3MHz. The measured differential nonlinearity (DNL) and integral nonlinearity (INL) are -0.43 to +0.48 LSB and -1.62 to +1.89 LSB respectively. The prototype ADC consumes 28.4 mW under a 1.2-V nominal power supply and 40 MHz sampling rate, transferring to a figure-of-merit (FOM) of 0.63 pJ per conversion-step. -

References

[1] Lee S C, Jeon Y D, Kwon J K, et al. A 10-bit 205-MS/s 1.0-mm2 90-nm CMOS pipeline ADC for flat panel display applications. IEEE J Solid-State Circuits, 2007, 42(12):2688 doi: 10.1109/JSSC.2007.908760[2] Chiu Y, Gray P R, Nikolic B. A 14-b 12-MS/s CMOS pipeline ADC with over 100-dB SFDR. IEEE J Solid-State Circuits, 2004, 39(12):2139 doi: 10.1109/JSSC.2004.836232[3] Andersen T N, Hernes B, Briskemyr A. A cost-efficient high-speed 12-bit pipeline ADC in 0.18-μm digital CMOS. IEEE J Solid-State Circuits, 2005, 4(7):1506 http://cat.inist.fr/?aModele=afficheN&cpsidt=16950779[4] Devarajan S, Singer L, Kelly D, et al. A 16-bit, 125 MS/s, 385 mW, 78.7 dB SNR CMOS pipeline ADC. IEEE J Solid-State Circuit, 2009, 44(12):3305 doi: 10.1109/JSSC.2009.2032636[5] Lee K H, Kim K S, Lee S H. A 12b 50 MS/s 21.6 mW 0.18μm CMOS ADC maximally sharing capacitors and op-amps. IEEE Trans Circuits Syst I:Regular Papers, 2011, 58(9):2127 doi: 10.1109/TCSI.2011.2112591[6] Li J, Zeng X Y, Xie L, et al. A 1.8-V 22-mW 10-bit 30-MS/s pipelined CMOS ADC for low-power subsampling applications. IEEE J Solid-State Circuits, 2008, 42(2):321 http://ieeexplore.ieee.org/document/4444571/?&arnumber=4444571[7] Shu G, Guo Y, Ren J, et al. A power-efficient 10-bit 40-MS/s sub-sampling pipelined CMOS analog-to-digital converter. Analog Integr Circ Sig Process, 2011, 67:95 doi: 10.1007/s10470-011-9608-7[8] Adeniran O A, Demosthenous A. Constant-resistance CMOS input sampling switch for GSM/WCDMA high dynamic range Δ Σ modulators. IEEE Trans Circuits Syst I:Regular Papers, 2008, 55(10):3234 doi: 10.1109/TCSI.2008.924883[9] Galhardo A, Goes J, Paulino N. Design of improved rail-to-rail low-distortion and low-stress switches in advanced CMOS technologies. Analog Integr Circ Sig Process, 2010, 64:13 doi: 10.1007/s10470-009-9357-z[10] Assaad R S, Silva-Martinez J. The recycling folded cascode:a general enhancement of the folded cascode amplifier. IEEE J Solid-State Circuits, 2009, 44(9):2535 doi: 10.1109/JSSC.2009.2024819[11] Ribner D B, Copeland M A. Design techniques for cascoded CMOS opamps with improved PSRR and common-mode input range. IEEE J Solid-State Circuits, 1984, 19(6):919 doi: 10.1109/JSSC.1984.1052246[12] Yavari M, Shoaei O, Svelto F. Hybrid cascade compensation for two-stage CMOS operational amplifiers. Proceedings IEEE International Symposium Circuits and Systems, 2005:1565 http://ieeexplore.ieee.org/articleDetails.jsp?arnumber=1464900[13] Singh P N, Kumar A, Debnath C, et al. 20 mW, 125 MSPS, 10 bit pipelined ADC in 65 nm standard digital CMOS process. IEEE Custom Integrated Circuits Conference, 2007:189 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=4405710[14] Ding K, Cai K, Han Y. Design of a high-speed sample-and-hold circuit using a substrate-biasing-effect attenuated T switch. Microelectron J, 2010, 41(12):809 doi: 10.1016/j.mejo.2010.06.018[15] Fayomi C J B, Roberts G W, Sawan M. Low-voltage CMOS analog bootstrapped switch for sample-and-hold circuit:design and chip characterization. IEEE International Symposium on Circuits and Systems, Kobe, Japan, 2005, 5:2200 http://ieeexplore.ieee.org/document/1465058/keywords[16] Wang L, Yin W J, Xu J, et al. Dual-channel bootstrapped switch for high-speed high-resolution sampling. IET Electron Lett, 2006, 42(22):1275 doi: 10.1049/el:20062344[17] Iroaga E, Murmann B. A 12-bit 75-MS/s pipelined ADC using incomplete settling. IEEE J Solid-State Circuits, 2007, 42(4):748 doi: 10.1109/JSSC.2007.892154[18] Ahmed I, Johns D A. An 11-bit 45 MS/s pipelined ADC with rapid calibration of DAC errors in a multi-bit pipeline stage. IEEE J Solid-State Circuit, 2008, 43(7):1626 doi: 10.1109/JSSC.2008.923724[19] Choi M H, Ahn G C, Lee S H. 12 b 50 MS/s 0.18μm CMOS ADC with highly linear input variable gain amplifier. Electron Lett, 2010, 46(18):1254 doi: 10.1049/el.2010.1834 -

Proportional views

DownLoad:

DownLoad: