| Citation: |

Chenghao Bian, Jun Yan, Yin Shi, Ling Sun. A 130 nm CMOS low-power SAR ADC for wide-band communication systems[J]. Journal of Semiconductors, 2014, 35(2): 025003. doi: 10.1088/1674-4926/35/2/025003

****

C H Bian, J Yan, Y Shi, L Sun. A 130 nm CMOS low-power SAR ADC for wide-band communication systems[J]. J. Semicond., 2014, 35(2): 025003. doi: 10.1088/1674-4926/35/2/025003.

|

A 130 nm CMOS low-power SAR ADC for wide-band communication systems

DOI: 10.1088/1674-4926/35/2/025003

More Information

-

Abstract

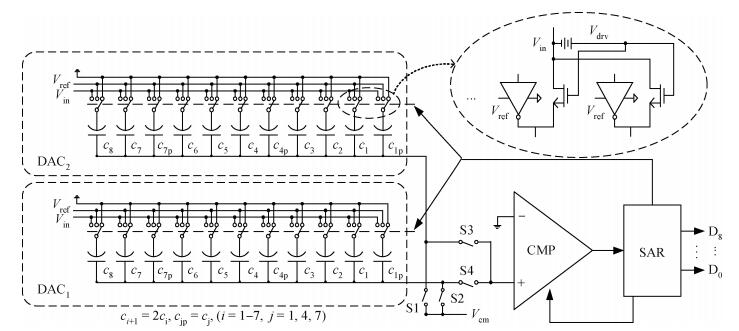

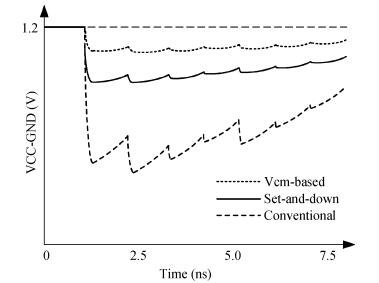

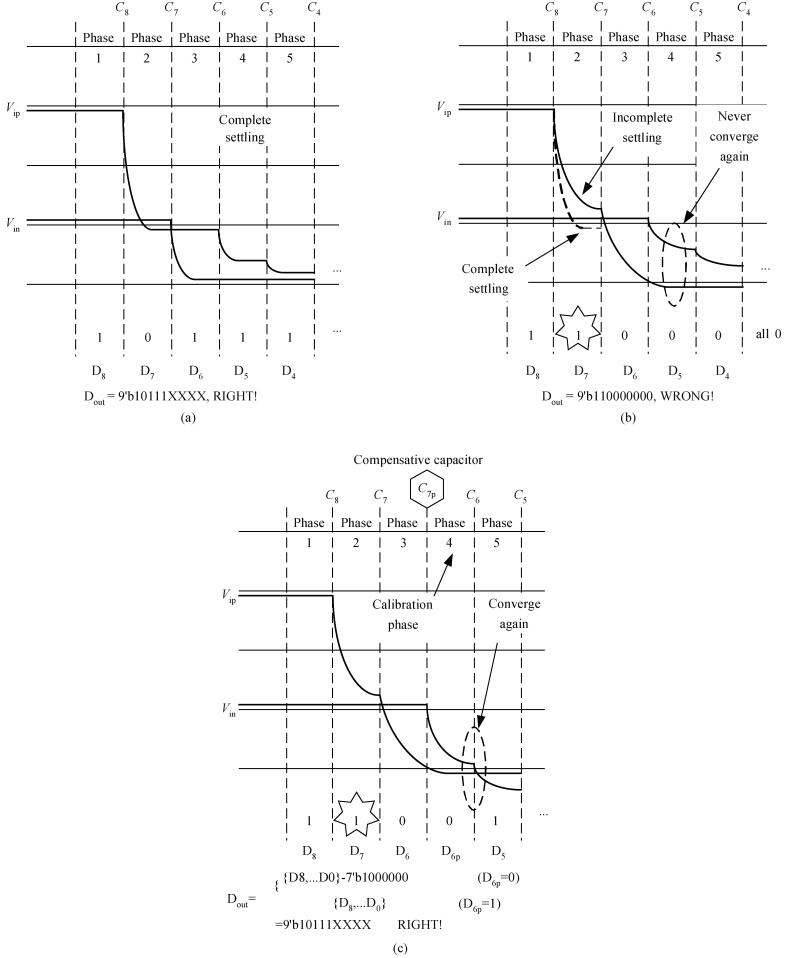

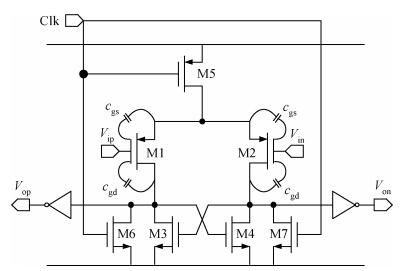

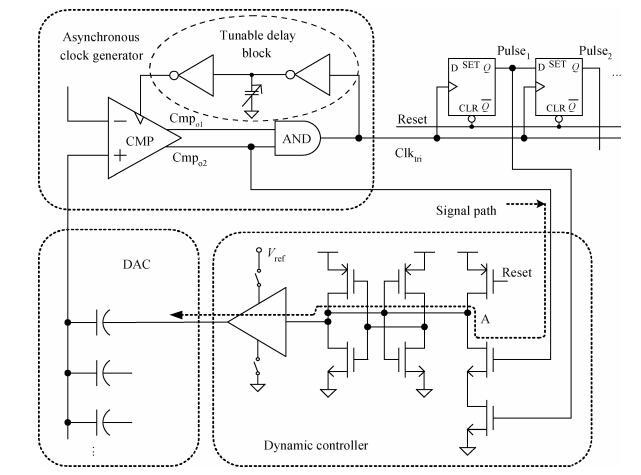

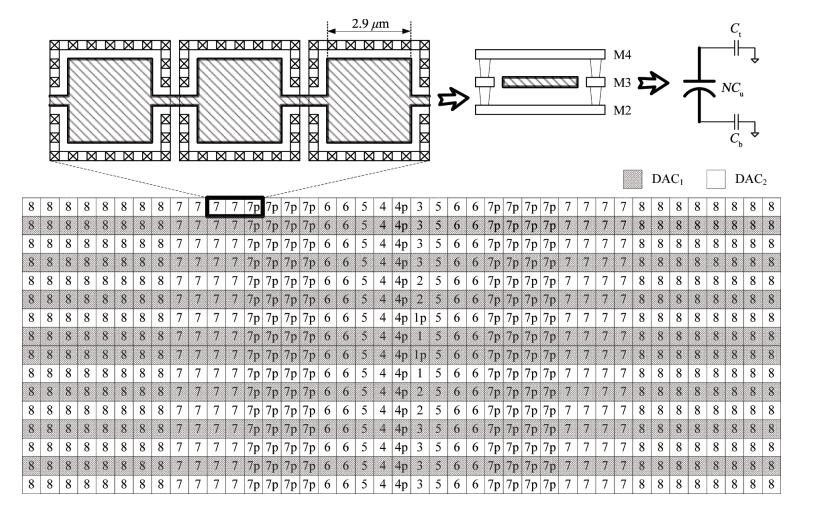

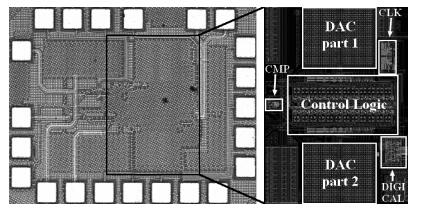

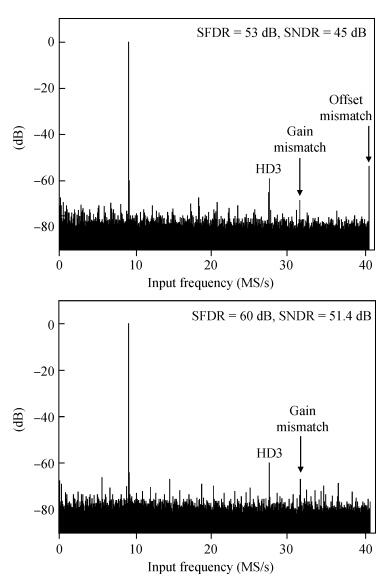

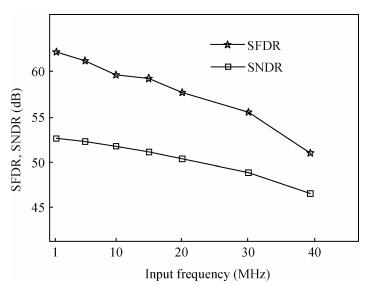

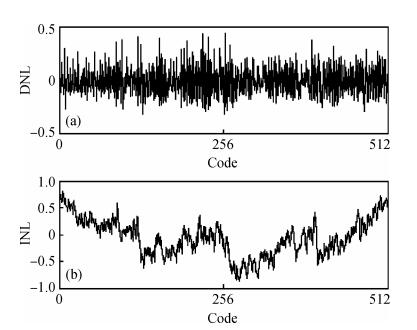

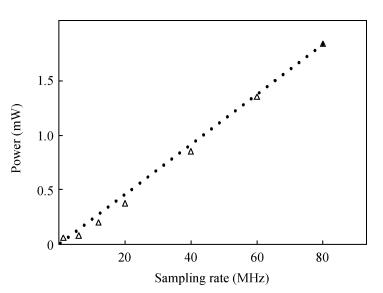

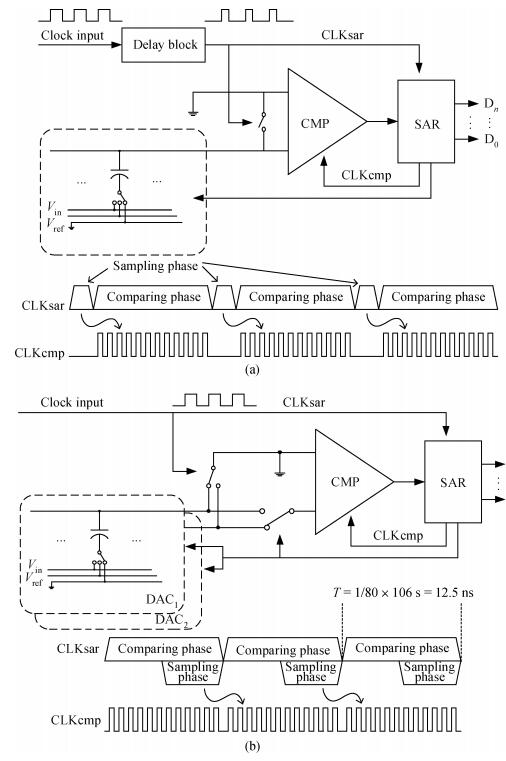

This paper presents a low power 9-bit 80 MS/s SAR ADC that uses the comparator-sharing technique in a 130 nm CMOS process. Compared to the conventional SAR ADC, the sampling phase is removed to reach the full efficiency of the comparator. Thus the conversion rate increases by about 20% and its sampling time is relaxed. The design does not use any static components to achieve a widely scalable conversion rate with a constant FOM. The floorplan of the capacitor network is custom-designed to suppress the gain mismatch between the two DACs. The 'set-and-down' switching procedure and a novel binary-search error compensation scheme are utilized to further speed up the SA bit-cycling operation. A very fast logic controller is proposed with a delay time of only 90 ps. At 1.2 V supply and 80 MS/s the ADC achieves an SNDR of 51.4 dB and consumes 1.86 mW, resulting in an FOM of 76.6 fJ/conversion-step. The ADC core occupies an active area of only 0.089 mm2.-

Keywords:

- ADC,

- SAR,

- capacitor-sharing,

- error compensation,

- capacitor array,

- dynamic logic

-

References

[1] Harpe P, Cntatore E, Roermund A V. A 2.2/2.7 fJ/conversion-step 10/1240 kS/s SAR ADC with data-driven noise reduction. International Solid-State Circuits Conference, 2013:270[2] Ma Jun, Guo Yawei, Wu Yue, et al. A 1-V 10-bit 80-MS/s 1.6-mW SAR ADC in 65-nm GP CMOS. Journal of Semiconductors, 2013, 34(8):085014 doi: 10.1088/1674-4926/34/8/085014[3] Kuttner F. A 1.2 V 10 b 20 MSample/s non-binary successive approximation ADC in 0.13μm CMOS. International Solid-State Circuits Conference, 2002:176[4] Cho S H, Lee C K, Kwon J K, et al. A 550-μ W 10-b 40-MS/s SAR ADC with multistep addition-only digital error correction. IEEE J Solid-State Circuits, 2011, 46(8):1881 doi: 10.1109/JSSC.2011.2151450[5] Liu C C, Chang S J, Huang G Y, et al. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J Solid-State Circuits, 2010, 45(4):731 doi: 10.1109/JSSC.2010.2042254[6] Yoshioka M, Ishikawa K, Takayama T, et al. A 10 b 50 MS/s 820 μW SAR ADC with on-chip digital calibration. International Solid-State Circuits Conference, 2010:384[7] Zhu Y, Chan C H, Chio U F, et al. A 100-MS/s reference-free SAR ADC in 90 nm CMOS. International Solid-State Circuits Conference, 2010:1111[8] Tsai J H, Chen Y J, Shen M H, et al. A 1-V, 8 b, 40 MS/s, 113 μW charge-recycling SAR ADC with a 14 μW asynchronous controller. IEEE Symp on VLSI Circuit, 2011:264 -

Proportional views

DownLoad:

DownLoad: