| Citation: |

Xinsheng Wang, Yizhe Hu, Mingyan Yu. Process variation robust current-mode on-chip interconnect signaling scheme[J]. Journal of Semiconductors, 2014, 35(2): 025004. doi: 10.1088/1674-4926/35/2/025004

****

X S Wang, Y Z Hu, M Y Yu. Process variation robust current-mode on-chip interconnect signaling scheme[J]. J. Semicond., 2014, 35(2): 025004. doi: 10.1088/1674-4926/35/2/025004.

|

Process variation robust current-mode on-chip interconnect signaling scheme

DOI: 10.1088/1674-4926/35/2/025004

More Information

-

Abstract

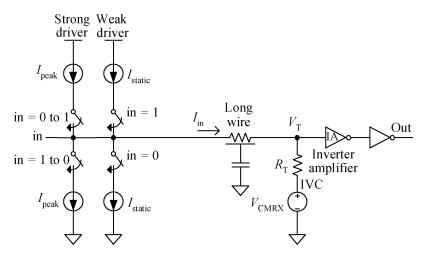

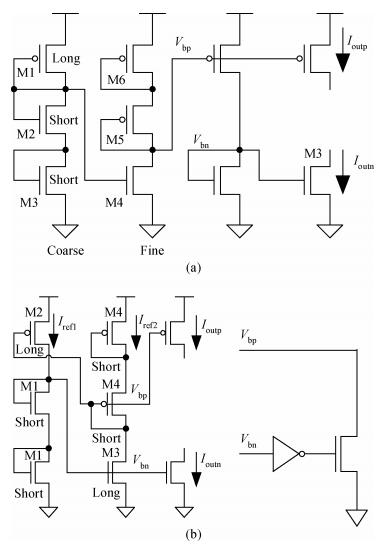

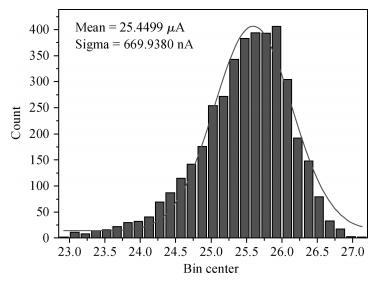

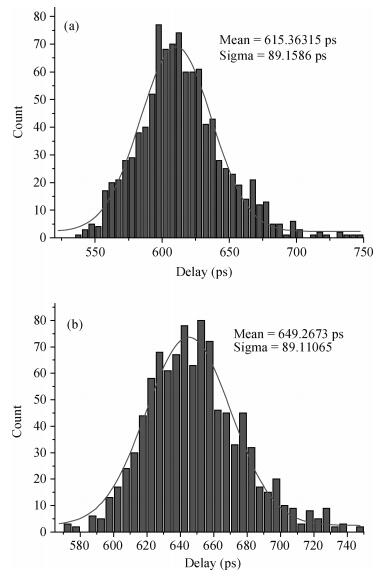

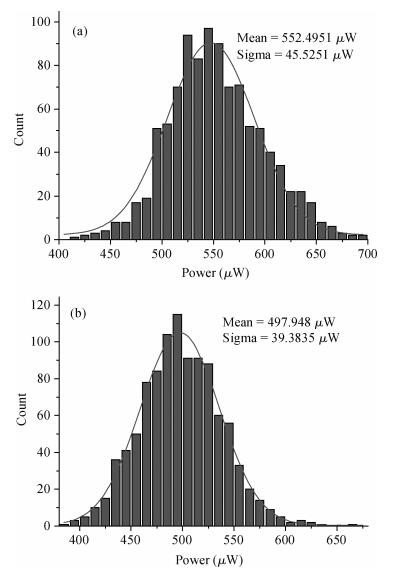

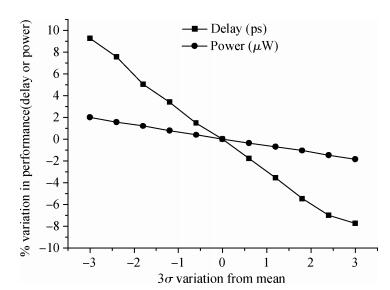

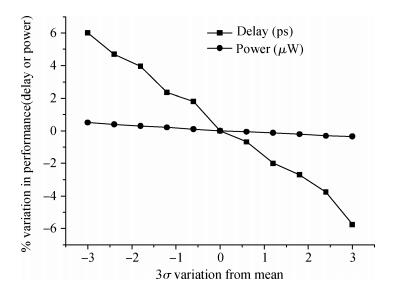

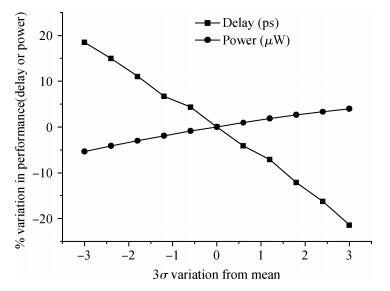

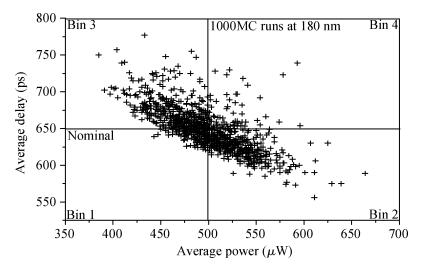

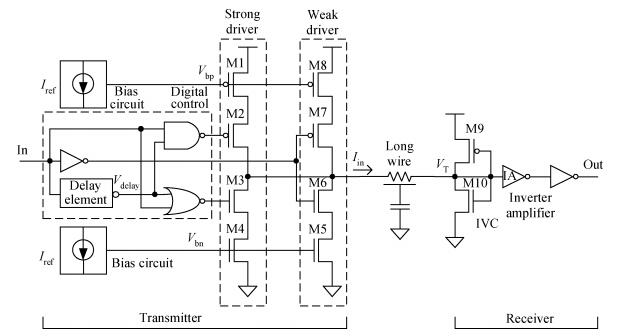

We propose a novel bias circuit, which can help a promising current-mode signaling (CMS) scheme (CMS-bias) enhance the robustness against process variation but consume less energy than the original bias circuit in this scheme. Monte Carlo and process corner analysis are carried out using HSPICE in the Global Foundry 0.18 μm process. Monte Carlo analysis shows that the CMS-bias with proposed bias circuit (CMS-proposed) and the CMS-bias with original circuit (CMS-original) have the same robustness against the variation, but the former offer a 9% reduction in power consumption. The process corner analysis shows that the average power and delay of the CMS-proposed don't change much in different process corners, especially in FS and SF corner. In addition, parameter sensitivity analysis shows that the process variation in long wires has little influence on the delay of the CMS scheme, but the variation in the effective length of MOSFETs influences the performance of the CMS scheme very much.-

Keywords:

- global interconnect,

- current-mode,

- Monte Carlo

-

References

[1] Dennard R H, Gaensslen F H, Rideout V L, et al. Design of ion-implanted MOSFETs with very small physical dimensions. IEEE J Solid-State Circuits, 1974, 9:256 doi: 10.1109/JSSC.1974.1050511[2] Dave M V, Baghini M S, Sharma D. Current mode interconnect. Indian Institute of Technology, Bombay, 2010[3] Dave M V, Baghini M S, Sharma D K. Low power current mode receiver with inductive input impedance, low power electronics and design (ISLPED). ACM/IEEE International Symposium, Bangalore, 2008:225[4] Hedenstierna N, Jeppson K O. CMOS circuit speed and buffer optimization. IEEE Trans Computer Aided Design, 1986, (6):270 http://ieeexplore.ieee.org/document/1270271/?reload=true&arnumber=1270271&punumber%3D43[5] Prasad V, Desai M P. Interconnect delay minimization using a novel pre-mid-post buffer strategy. Proceedings of the 16th International Conference on VLSI Design, New Delhi, 2003:417 http://ieeexplore.ieee.org/document/1183171/keywords[6] Dave M, Satkuri R, Jain M, et al. Low-power current-mode transceiver for on-chip bidirectional buses. ACM/IEEE International Symposium on Low-Power Electronics and Design (ISLPED), 2010:61[7] Nalamalpu A, Srinivasan S, Burleson W P. Boosters for driving long on-chip interconnects-design issues, interconnect synthesis, and comparison with repeaters. IEEE Trans Computer-Aided Design of Integrated Circuits and Systems, 2002, 21:50 doi: 10.1109/43.974137[8] Beers P, Seevinck E, Ontrop H. Current-mode techniques for high-speed VLSI circuits with application to current sense amplifier for CMOS SRAM. IEEE J Solid-State Circuits, 1991, 26:525 doi: 10.1109/4.75050[9] Nassif S. Design for variability in DSM technologies. IEEE International Symposium on Quality Electronic Design, San Jose, 2000:451[10] Borkar S, Kamik T, Narendra S, et al. Parameter variations and impact on circuits and microarchitecture. IEEE Design Automation Conference, Anaheim, 2003:338[11] Venkatraman V, Burleson W. Robust multi-level current-mode on-chip interconnect signaling in the presence of process variations. Sixth International Symposium on Quality of Electronic Design, San Jose, 2005:522[12] Bashirullah R. Reduced delay sensitivity to process induced variability in current sensing interconnects. Electron Lett, 2006, 42:531 doi: 10.1049/el:20064368[13] Europractice, Belgium, Foundry resistance model file, 2007. http://www.europractice-ic.com/index.php[14] Dave M, Shojaei M, Sharma D. A process variation tolerant, high-speed and low-power current mode signaling scheme for on-chip interconnects. Proc GLSVLSI, Boston, 2009:389[15] Dave M, Jain M, Baghini M S, et al. A variation tolerant current-mode signaling scheme for on-chip interconnects. IEEE Trans VLSI Syst, 2013, 21:342 doi: 10.1109/TVLSI.2012.2185835 -

Proportional views

DownLoad:

DownLoad: