| Citation: |

Jianhua Jiang, Man Liang, Lei Wang, Yumei Zhou. An effective timing characterization method for an accuracy-proved VLSI standard cell library[J]. Journal of Semiconductors, 2014, 35(2): 025005. doi: 10.1088/1674-4926/35/2/025005

****

J H Jiang, M Liang, L Wang, Y M Zhou. An effective timing characterization method for an accuracy-proved VLSI standard cell library[J]. J. Semicond., 2014, 35(2): 025005. doi: 10.1088/1674-4926/35/2/025005.

|

An effective timing characterization method for an accuracy-proved VLSI standard cell library

DOI: 10.1088/1674-4926/35/2/025005

More Information

-

Abstract

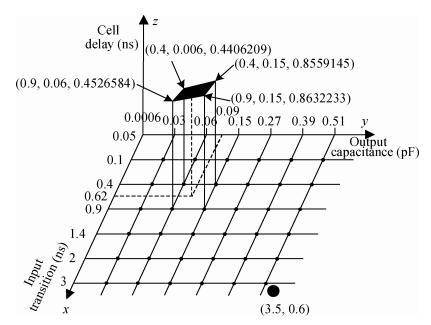

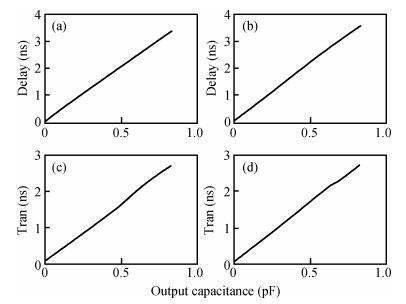

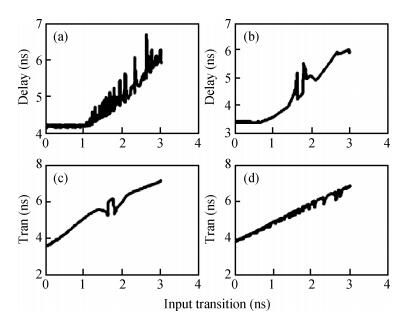

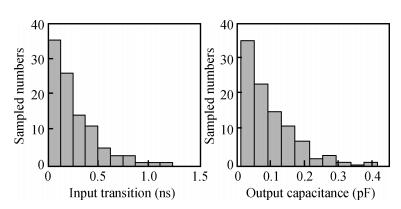

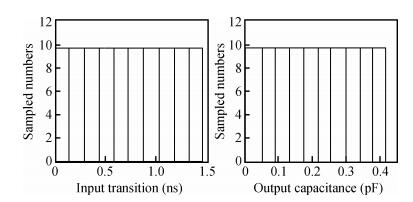

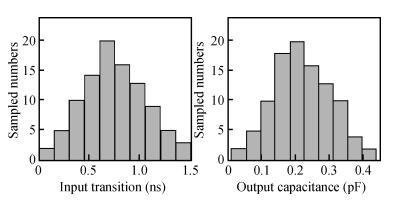

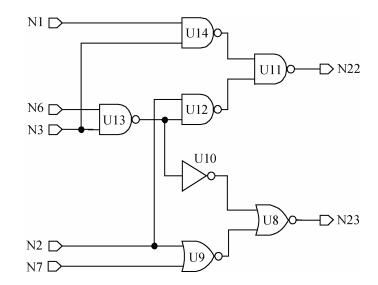

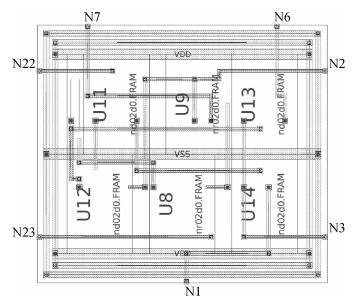

This paper presents a method of tailoring the characterization and modeling timing of a VLSI standard cell library. The paper also presents a method to validate the reasonability of the value through accuracy analysis. In the process of designing a standard cell library, this method is applied to characterize the cell library. In addition, the error calculations of some simple circuit path delays are compared between using the characterization file and an Hspice simulation. The comparison results demonstrate the accuracy of the generated timing library file.-

Keywords:

- characteristic parameters,

- error calculation,

- look-up table,

- Lib file

-

References

[1] Zhang K, Wang D H, Li Y G. Library building for sub-micron CMOS process. Fifth International IEEE Conference on ASIC, 2003:1369[2] Library CompilerTM Modeling Timing, Signal Integrity, and Power in Technology Libraries User Guide[3] Scheffer L. EDA for IC implementation, circuit design, and process technology. Addision-Wesley, Reading[4] Gao Mingzhi, Ye Zuochang, Wang Yan, et al, On modeling the digital gate delay under process variation. Journal of Semiconductors, 2011, 32(7):075010 doi: 10.1088/1674-4926/32/7/075010[5] Ackalloor B, Gaitonde D. An overview of library characterization in semi-custom design. IEEE Custom Integrated Circuits Conference, 1998[6] Rachit I K, Bhat M S. AutoLibGen:an open source tool for standard cell library characterization at 65nm technology. International Conference on Electronic Design Penang, Malaysia, 2008 http://ieeexplore.ieee.org/document/4786726/authors[7] Miryala S, Kaur B, Anand B, et al. Efficient nanoscale VLSI standard cell library characterization using a novel delay model. 12th Int'l Symposium on Quality Electronic Design, 2011 http://ieeexplore.ieee.org/document/5770767/keywords[8] LibertyTM NCX User Guide Version B, December 2008 -

Proportional views

DownLoad:

DownLoad: