| Citation: |

N. Vithyalakshmi, M. Rajaram. A multi coding technique to reduce transition activity in VLSI circuits[J]. Journal of Semiconductors, 2014, 35(2): 026001. doi: 10.1088/1674-4926/35/2/026001

****

N. Vithyalakshmi, M. Rajaram. A multi coding technique to reduce transition activity in VLSI circuits[J]. J. Semicond., 2014, 35(2): 026001. doi: 10.1088/1674-4926/35/2/026001.

|

A multi coding technique to reduce transition activity in VLSI circuits

DOI: 10.1088/1674-4926/35/2/026001

More Information

-

Abstract

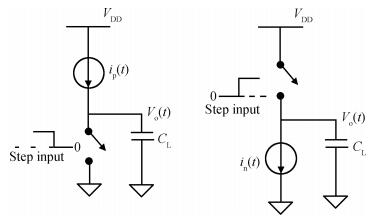

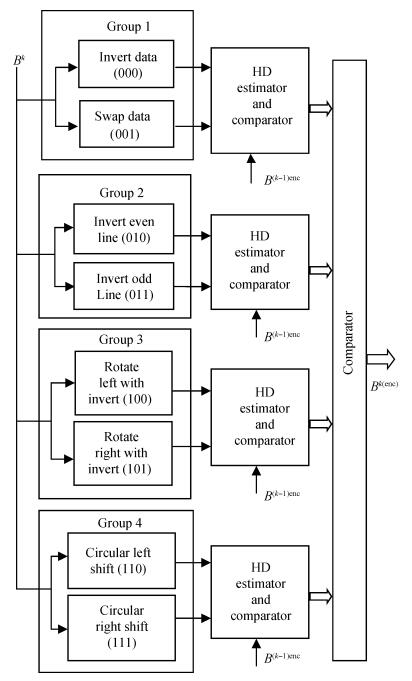

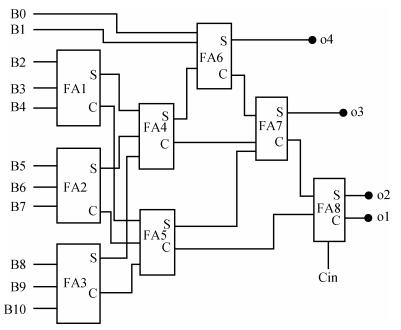

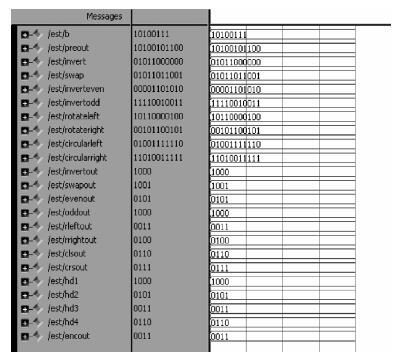

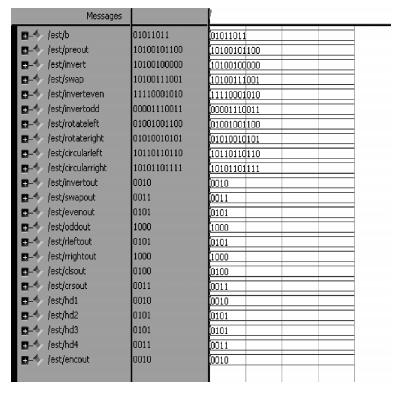

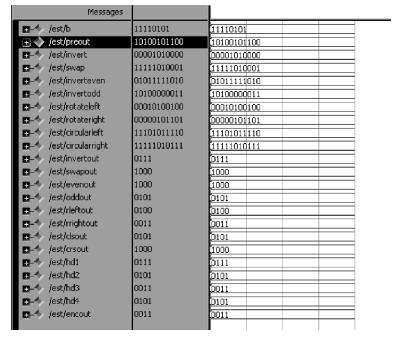

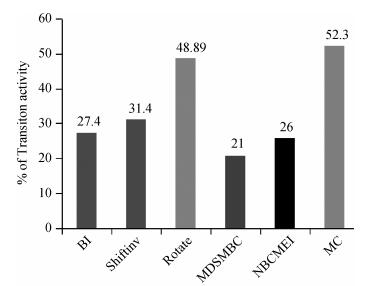

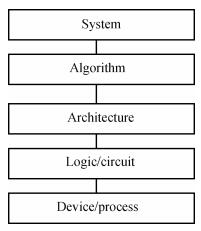

Advances in VLSI technology have enabled the implementation of complex digital circuits in a single chip, reducing system size and power consumption. In deep submicron low power CMOS VLSI design, the main cause of energy dissipation is charging and discharging of internal node capacitances due to transition activity. Transition activity is one of the major factors that also affect the dynamic power dissipation. This paper proposes power reduction analyzed through algorithm and logic circuit levels. In algorithm level the key aspect of reducing power dissipation is by minimizing transition activity and is achieved by introducing a data coding technique. So a novel multi coding technique is introduced to improve the efficiency of transition activity up to 52.3% on the bus lines, which will automatically reduce the dynamic power dissipation. In addition, 1 bit full adders are introduced in the Hamming distance estimator block, which reduces the device count. This coding method is implemented using Verilog HDL. The overall performance is analyzed by using Modelsim and Xilinx Tools. In total 38.2% power saving capability is achieved compared to other existing methods. -

References

[1] Alioto M, Palumbo G, Poli M. Energy consumption in RC tree circuits. IEEE Trans Very Large Scale Integration (VLSI) Syst, 2006, 14(5):452 doi: 10.1109/TVLSI.2006.876093[2] Xie L, Qiu P, Qiu Q. Partitioned bus coding for energy reduction. Asia and South Pacific Design Automation Conference, 2005:1280 http://ieeexplore.ieee.org/document/1466577/[3] Stan M R, Burleson W P. Bus-invert coding for low-power I/O. IEEE Trans VLSI, 1995, 3:49 doi: 10.1109/92.365453[4] Natesan J, Radhakrishnan D. Shift invert coding (SINV) for low power VLSI. Proceedings of the EUROMICRO Systems on Digital System Design, 2004 http://ieeexplore.ieee.org/document/1333276/?reload=true&arnumber=1333276&contentType=Conference%20Publications[5] M1 S B, Jahnavi D Y. Universal rotate invert bus encoding for low power VLSI. International Journal of VLSI design & Communication Systems (VLSICS), 2012, 3(4):97[6] Sainarayana K S, Ravindra J V R, Nath K T, et al. Coding for minimizing energy in VLSI interconnects. The 18th International Conference on Microelectronics, 2006:166 http://ieeexplore.ieee.org/document/4243675/?arnumber=4243675&sortType%3Dasc_p_Sequence%26filter%3DAND(p_IS_Number:4243632)[7] Kumar A, Goyal A K. Study of various full adders using tanner EDA tool. International Journal of Computer Science and Technology, 2012, 3:581 http://ijcst.com/vol31/3/arvind2.pdf[8] Chandrakasan A P, Brodersen R W. Minimizing power consumption in CMOS circuits. Department of EECS University of California at Berkeley[9] Shin Y, Chae S I, Choi K. Partial bus-invert coding for power optimization of application-specific systems. IEEE Trans VLSI, 2001, 9:377 doi: 10.1109/92.924059[10] Ramprasad S, Shanbhag N R, Haji J N. Information theoretic bounds on average signal transition activity. IEEE Trans VLSI, 1999, 7(3):359 doi: 10.1109/92.784097 -

Proportional views

DownLoad:

DownLoad: