| Citation: |

Xiaoyang Liu, He Ma, Daquan Yu, Wenlu Chen, Xiaolong Wu. Optimal design analysis for thermal performance of high power 2.5D package[J]. Journal of Semiconductors, 2016, 37(3): 035006. doi: 10.1088/1674-4926/37/3/035006

****

X Y Liu, H Ma, D Q Yu, W L Chen, X L Wu. Optimal design analysis for thermal performance of high power 2.5D package[J]. J. Semicond., 2016, 37(3): 035006. doi: 10.1088/1674-4926/37/3/035006.

|

Optimal design analysis for thermal performance of high power 2.5D package

DOI: 10.1088/1674-4926/37/3/035006

More Information

-

Abstract

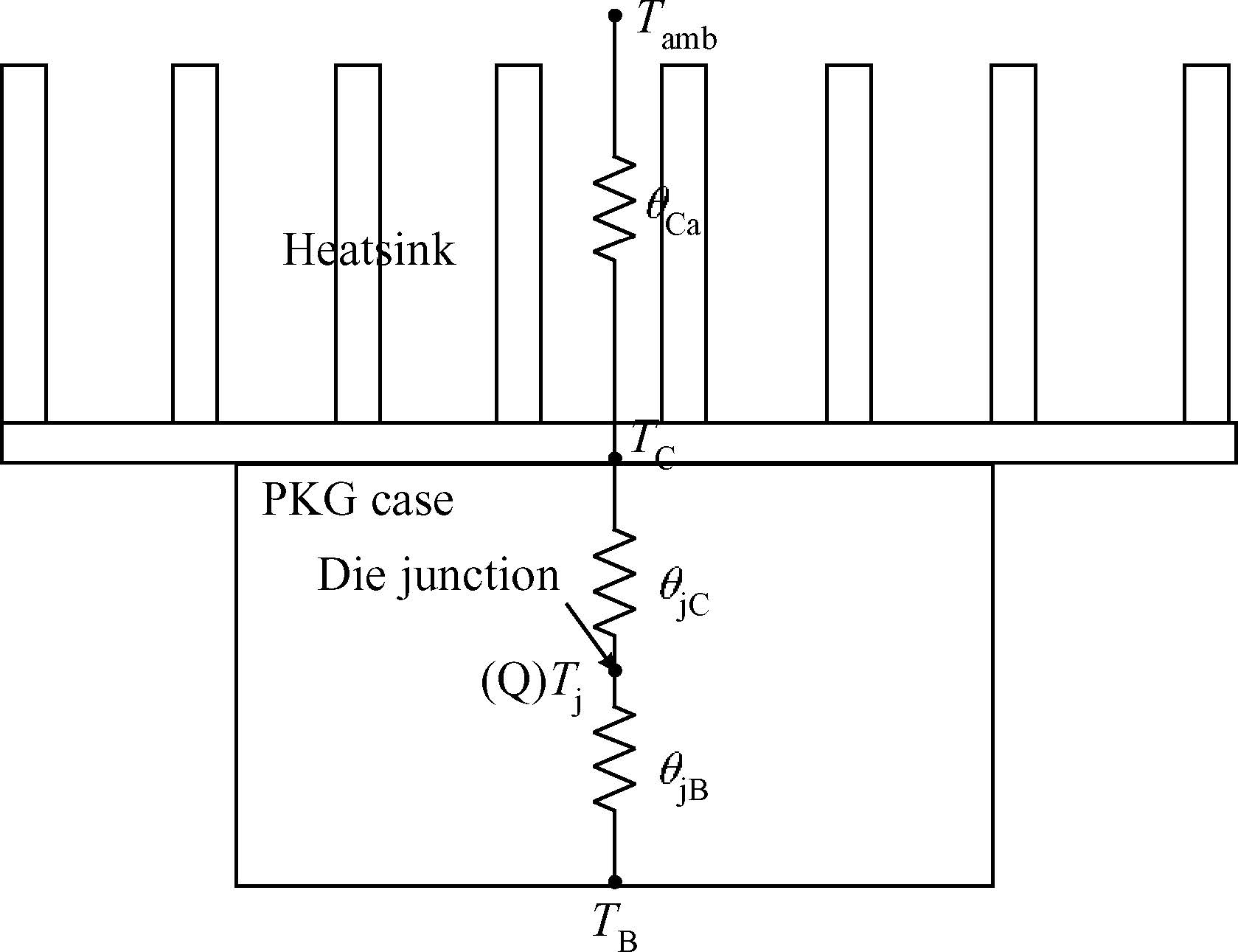

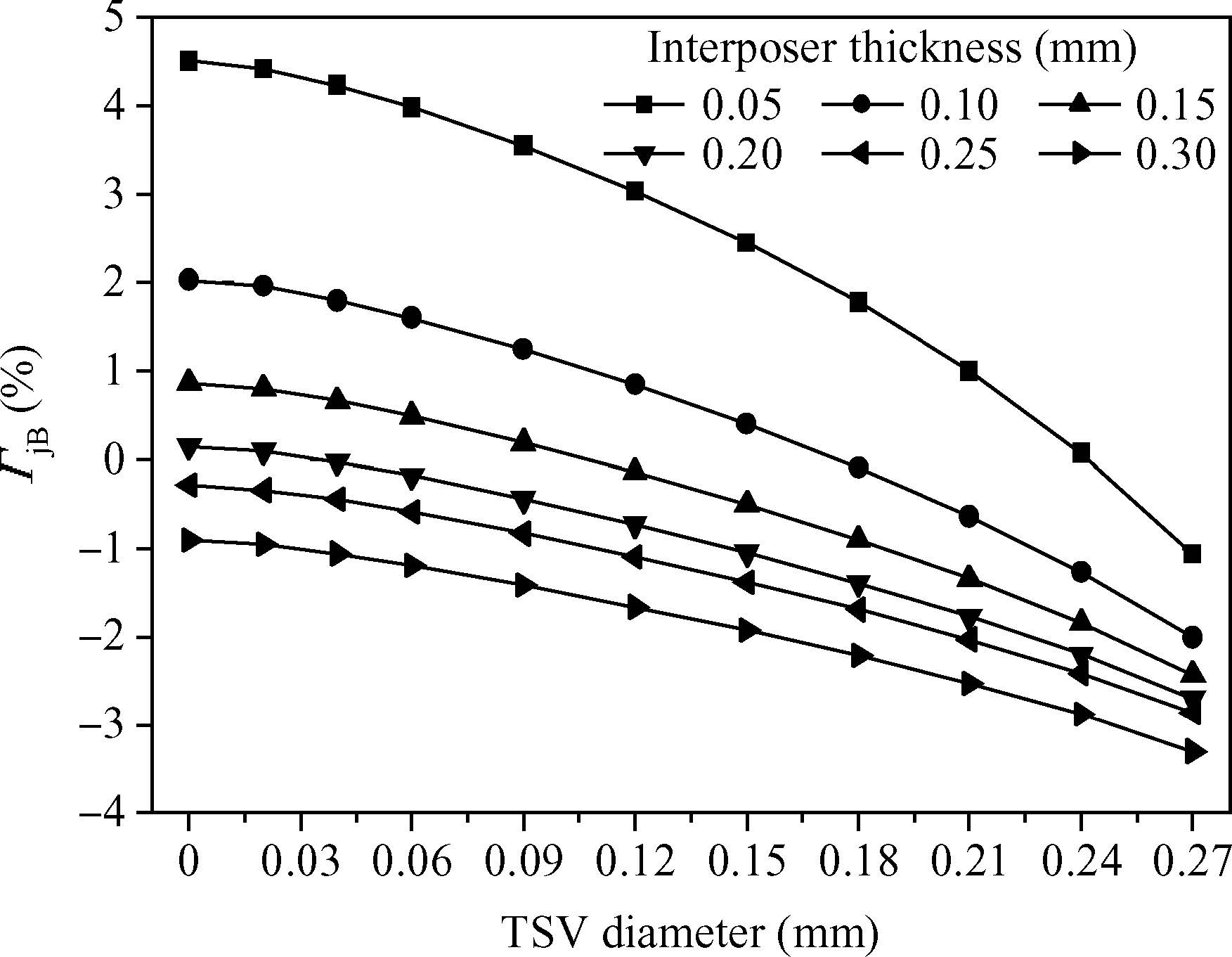

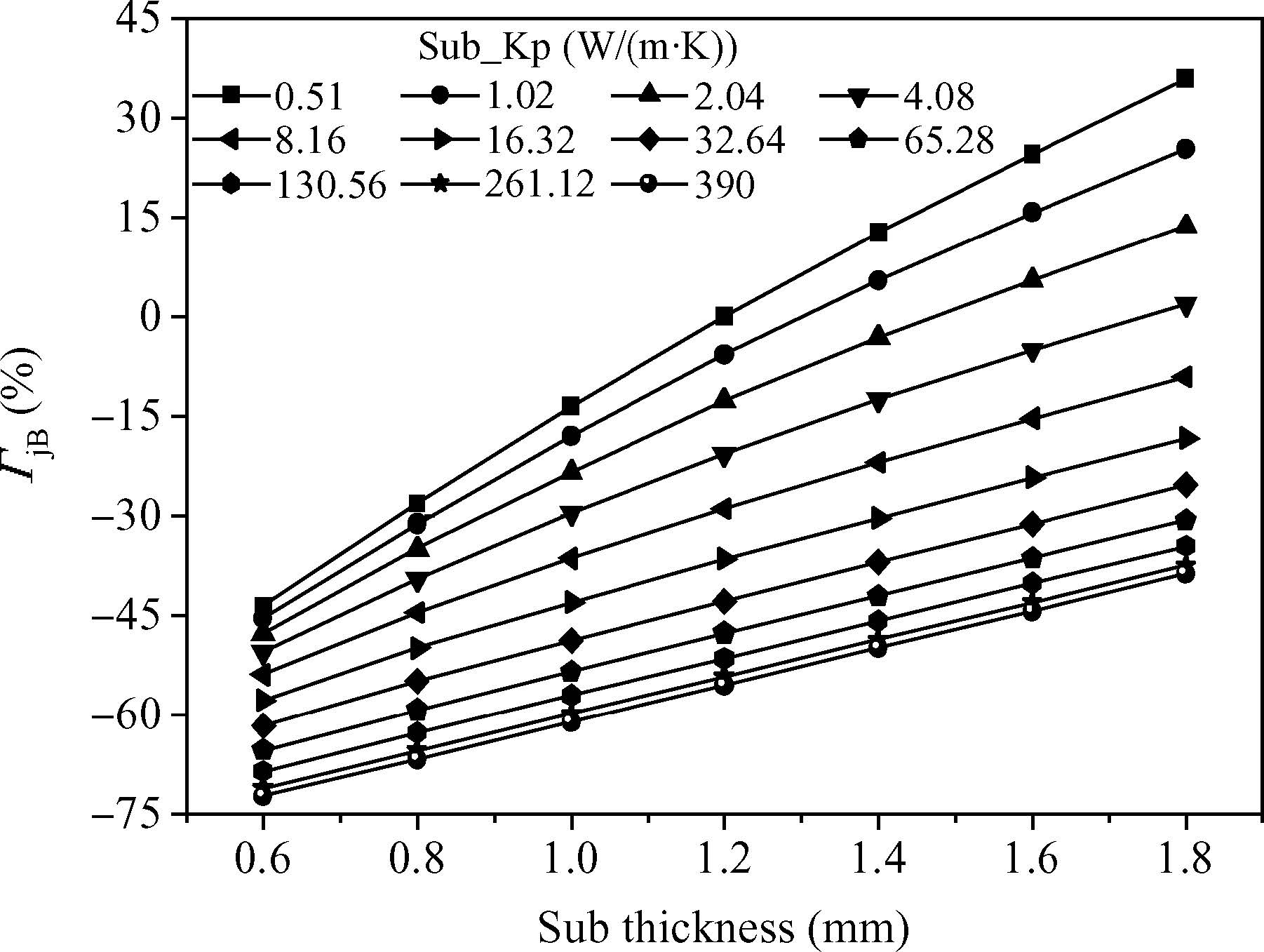

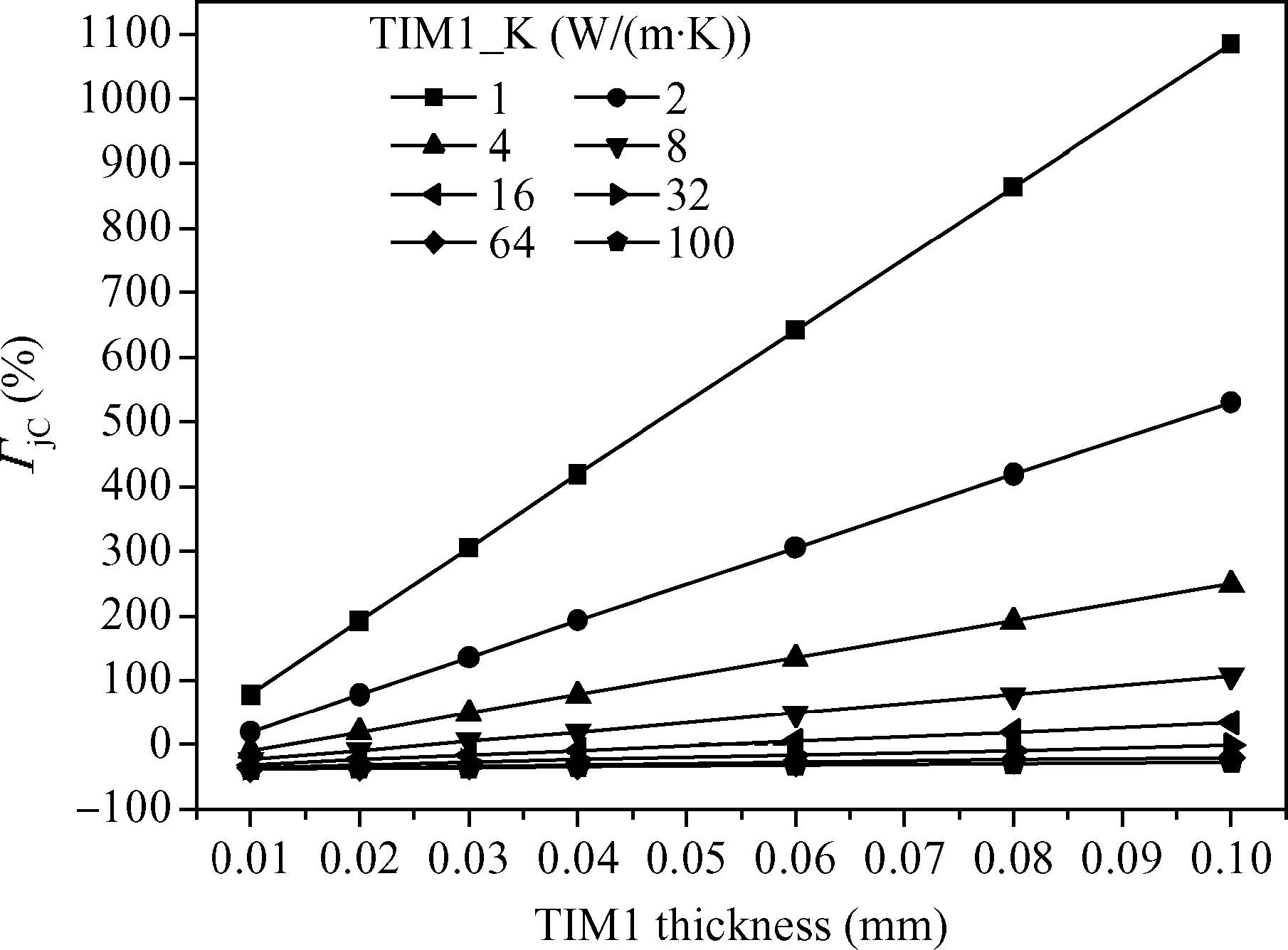

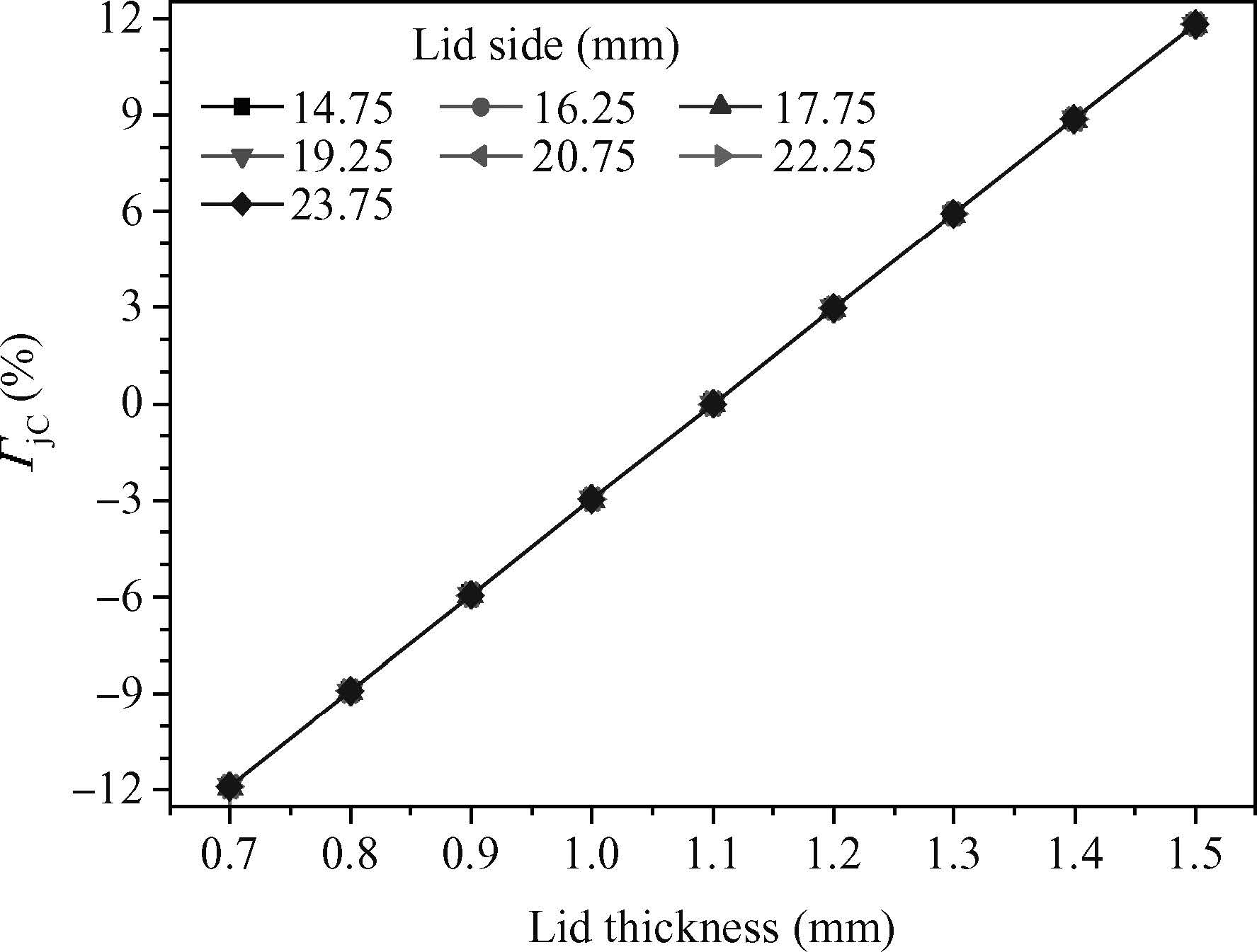

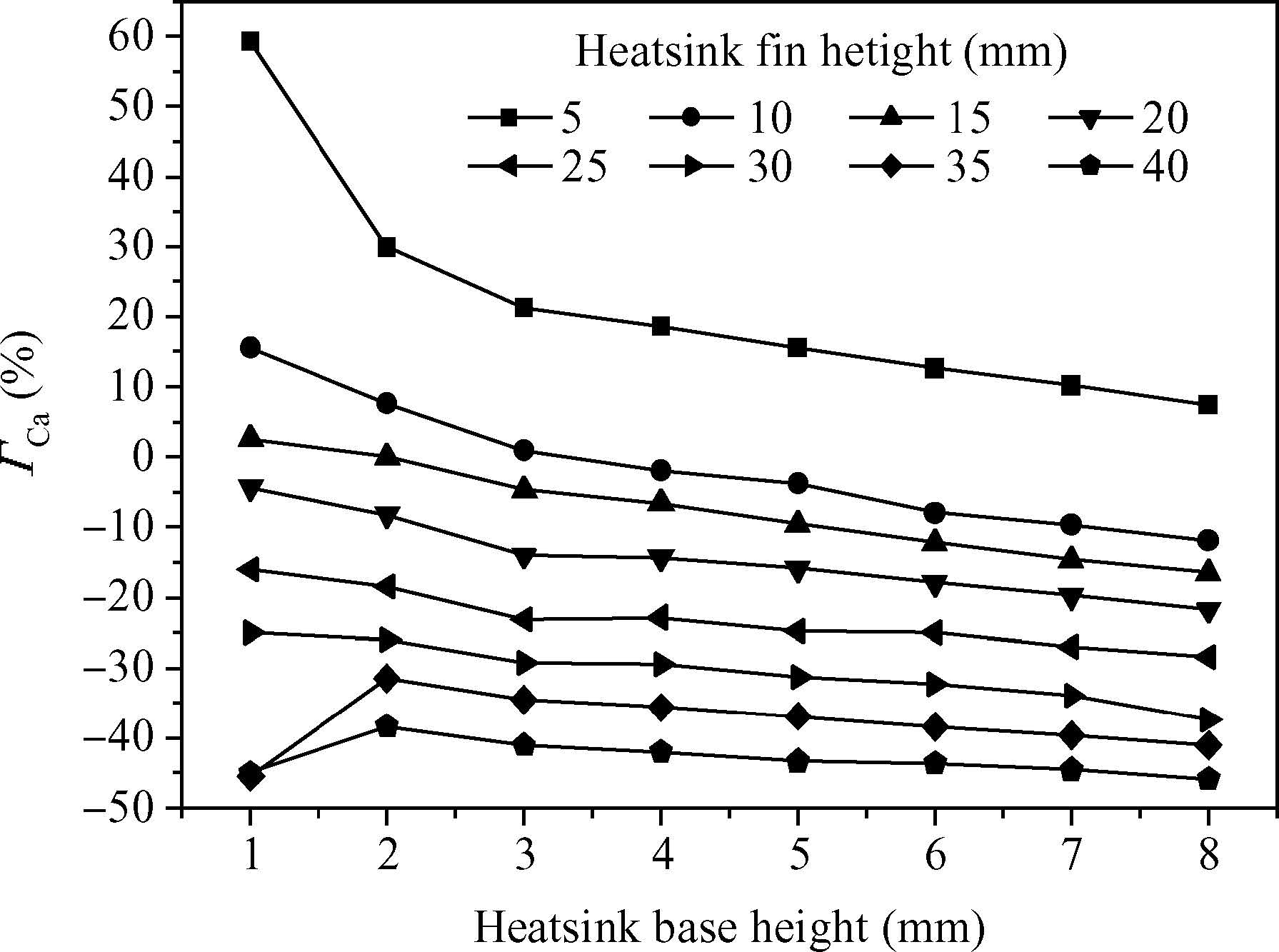

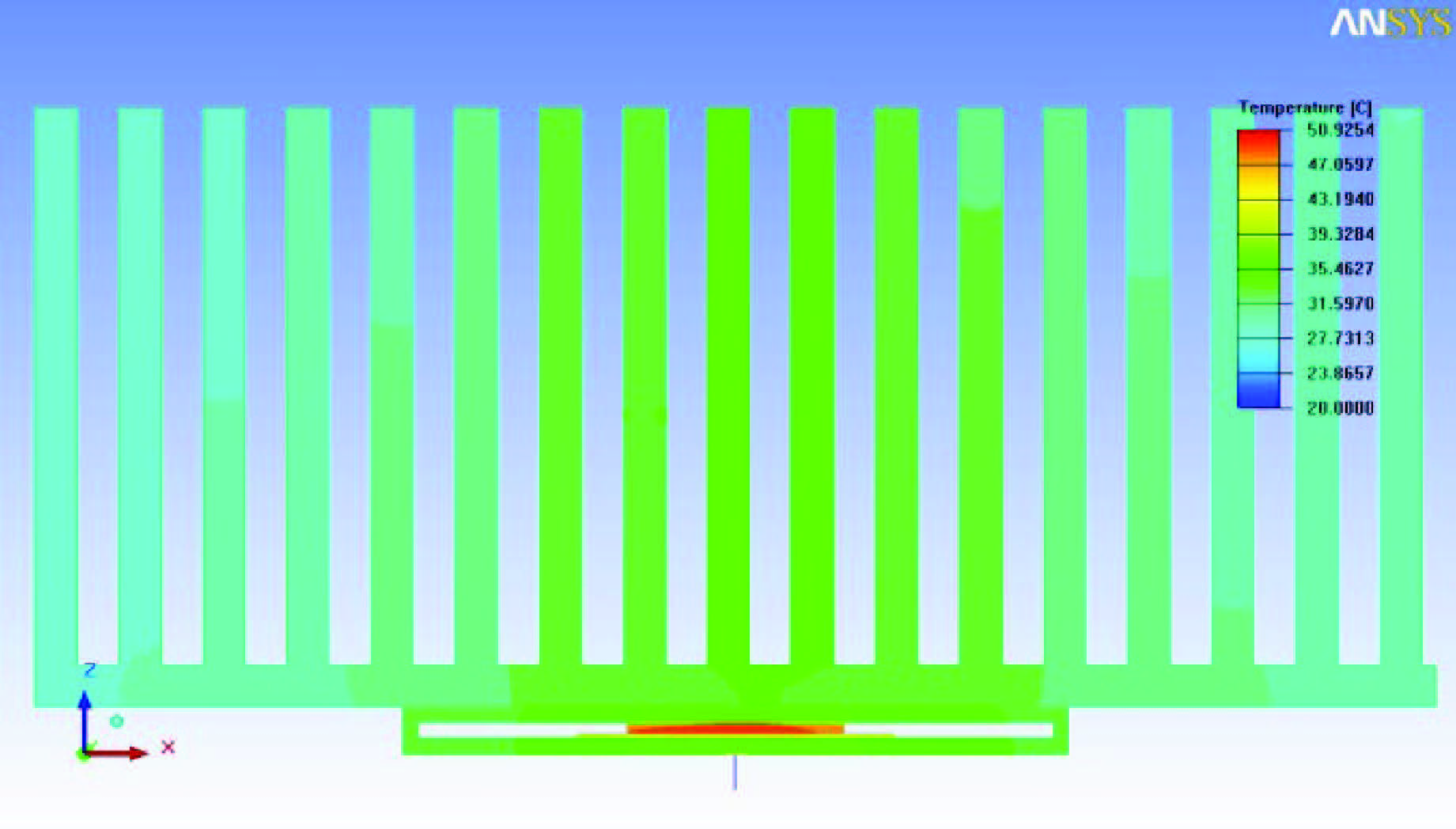

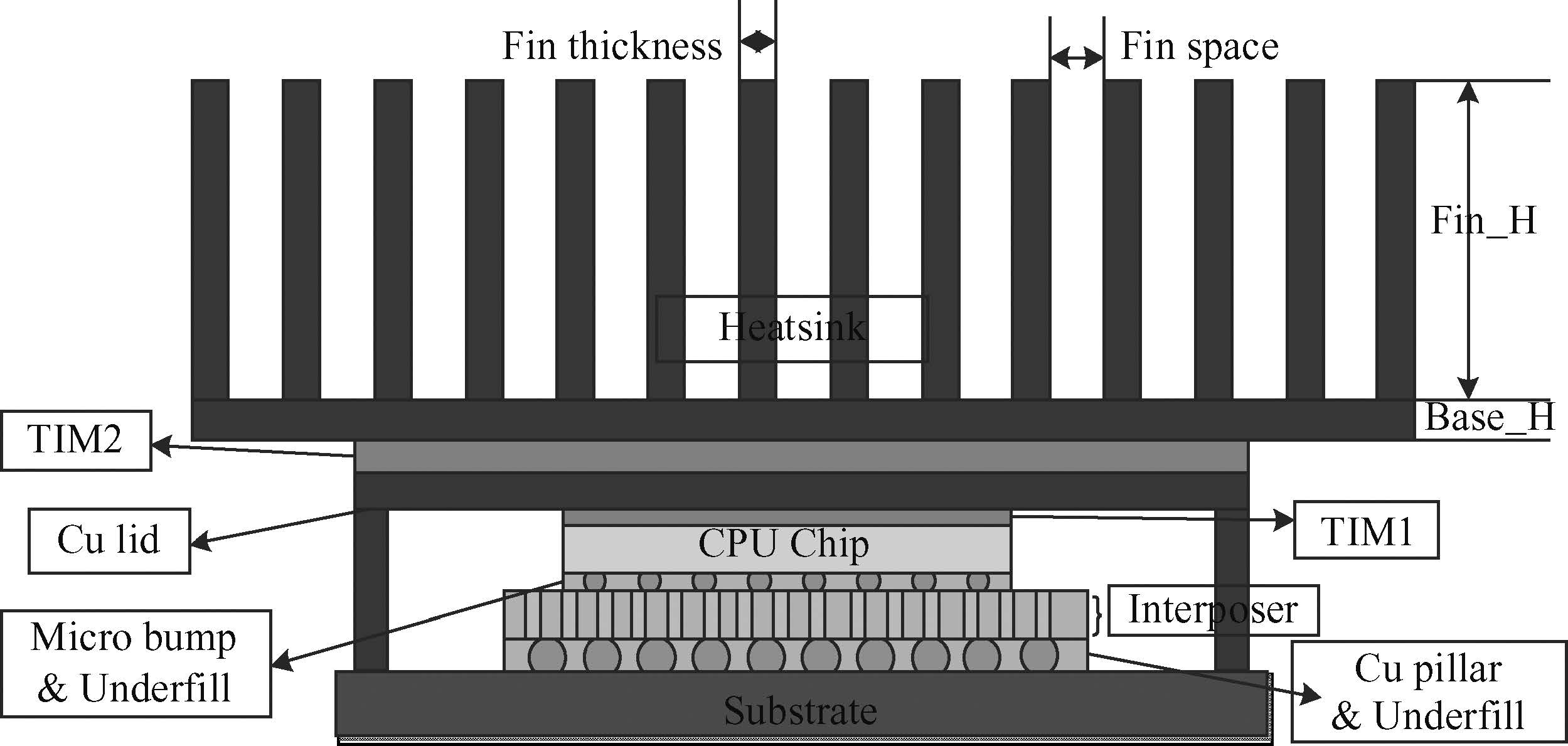

Based on ANSYS and Icepak softwares, the numerical analysis method is used to build up the thermal analysis model of the 2.5D package, which contains a high power CPU chip. The focus of the research is on the determination of the contributing factors and their effects on the thermal resistance and heat distribution of the package. The parametric analysis illustrates that the substrate conductivity, TIM conductivity and fin height are more crucial for heat conduction in the package. Furthermore, these major parameters are compared and analyzed by orthogonal tests, and the optimal solution for 2.5D integration is proposed. The factors' influence patterns on thermal resistance, obtained in this article, could be utilized as a thermal design reference.-

Keywords:

- 2.5D package,

- high power,

- thermal design,

- ANSYS

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] -

Proportional views

DownLoad:

DownLoad: