1. Introduction

Digital signal processing of analog function by connecting the data converter directly to the terminals is becoming a trend, which requires very high bandwidth and sampling speed. Meanwhile, the evolution towards high levels of integration in communication systems also drives the demands for high-speed and high-resolution digital-to-analog converters (DACs). For example, in a communication base station, the IEEE 802.3an 10GBASE-T Ethernet standard requires a 1 GS/s transmit DAC while driving a 50

In recent years, various high speed and high resolution DAC designs have been published[1-9]. Some designs concentrate on obtaining good low-frequency performance and adopt techniques like calibration or dynamic element matching[1, 2], but these methods will not improve high-frequency performance since high frequency matching is no longer the only limiting factor. Although the return-to-zero (RZ) method is used in some other designs to improve high-frequency performance[3, 4], use of this method loses half of the signal power and limits its application fields. In this paper, a segmented current-steering DAC which aims at achieving good SFDR at high frequency without adopting the RZ method is proposed. Meanwhile, a programmable interpolation filter is used to improve energy efficiency with different data rates.

2. DAC architecture

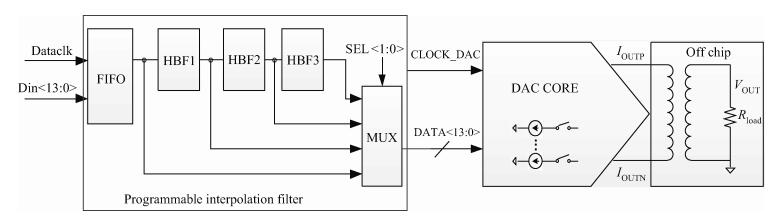

The block diagram of the proposed DAC is depicted in Fig. 1. It is mainly composed of a programmable digital interpolation filter and the DAC core. The programmable digital interpolation filter consists of a FIFO, three half-band filters (HBF1, HBF2 and HBF3) each with an interpolation factor of 2, and a MUX. The input signal to the DAC core (DATA < 13:0 > ) can have the same update rate as the input to the DAC (Din < 13:0 > ) or an update rate 2/4/8 times of the input to the DAC depending on the selection input SEL < 1:0 > to the MUX. The mode to be selected is determined by the DAC core update rate, and the programmable DAC works under non-interpolation mode, 2x-interpolation mode, 4x-interpolation mode or 8x-interpolation mode with the core update rate at 0–250 MS/s, 250–500 MS/s, 500–800 MS/s or 800–1000 GS/s, respectively.

For an interpolation filter with an interpolation factor of

|

$x_I (n)=\sum\limits_{m, =, 0}^N {h\left( {{\rm m}I+(n)_I } \right)} x\left( { {\frac{n}{I}}} \right),$ |

(1) |

where

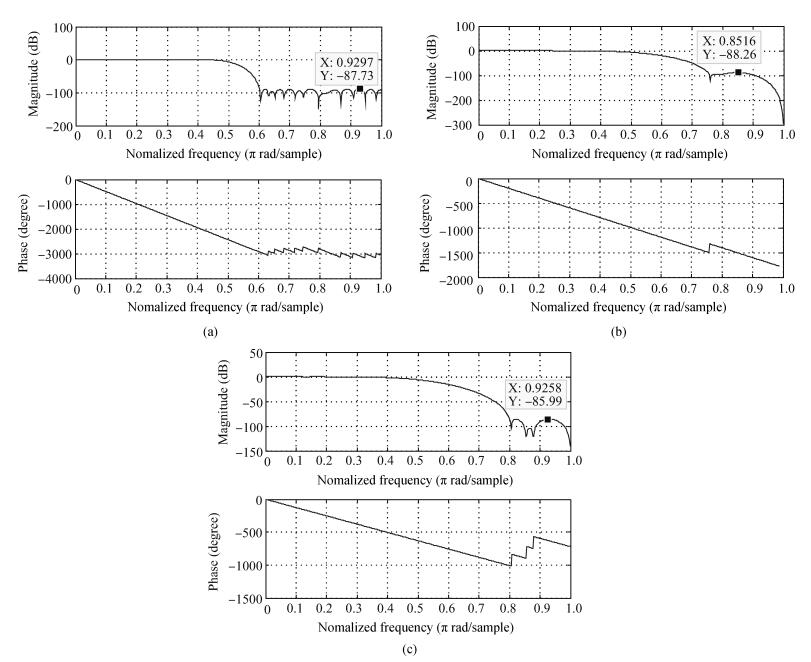

HBF1, HBF2 and HBF3 are half-band low-pass filters and because a half-band filter has 50 percent of its coefficients being zero, it outperforms other types in low power design. The filter order

|

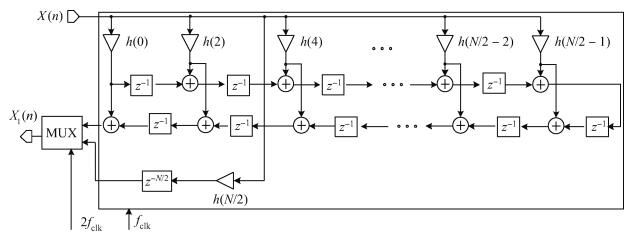

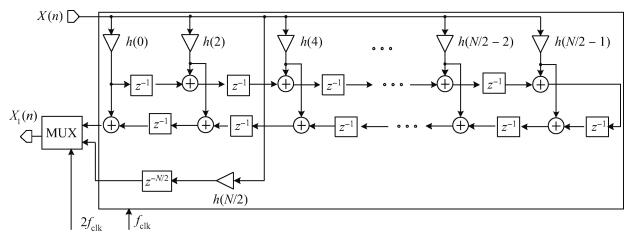

In the hardware implementation, several measures are taken to reduce the area and power consumption of the interpolation filters HBF1, HBF2 and HBF3. Firstly, the ploy-phase structure is adopted to reduce the hardware consumption, as shown in Fig. 3. Besides that, the filter is realized in transposed form which has the advantage of hardware reuse and also has the shortest critical path compared to other kinds of filter realization. Moreover, shift-and-add operations are used instead of dedicated multipliers to realize multiplication. Finally, a canonic sign digit (CSD) representation is adopted to express the coefficients. In this way, the coefficients can be represented with the fewest non-zero bits, which means minimal addition and subtraction operations.

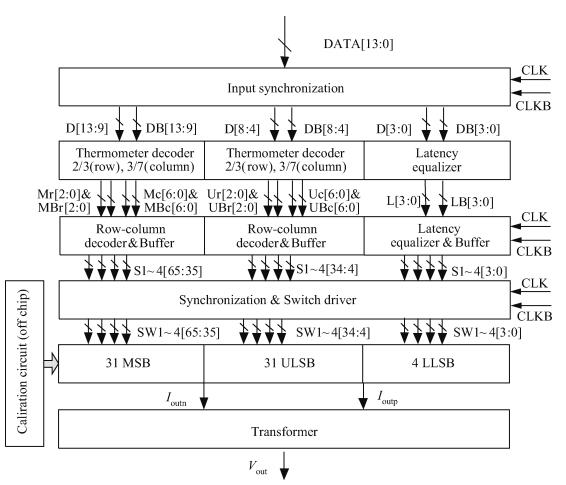

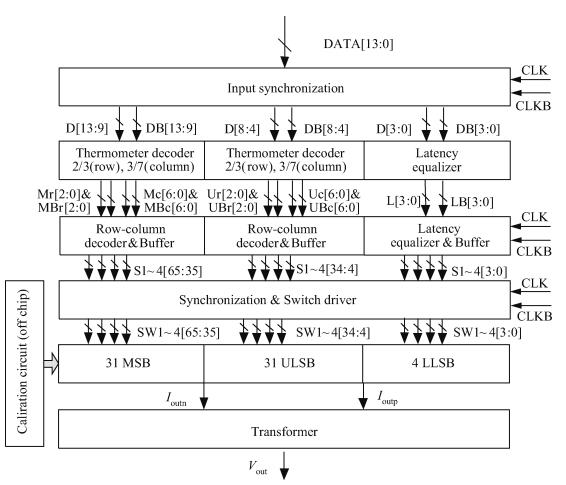

The block diagram of the DAC core is depicted in Fig. 4. The current-steering architecture adopted here is the best choice for fast-sampling DAC so far. In consideration of simplicity, compactness and reducing differential nonlinearity (DNL) and glitch energy, a 5-5-4 segmented structure is used, which consists of 5 thermometer coded most significant bits (5 MSB), 5 thermometer coded upper least significant bits (5 ULSB), and 4 binary coded lower least significant bits (4 LLSB). Most of the design effort is focused on the MSB and the ULSB as these two sections determine the overall performance of the DAC. As shown in Fig. 4, cells in the MSB and the ULSB are driven by row-and-column thermometer decoders, which are easy to design and area efficient. The input signal is separated into two channels (D and DB) with complementary clocks (CLK and CLKB), so signal D is half a clock before signal DB. Although it doubles the digital part area, the high-frequency performance will be greatly improved with a proper switching sequence.

To meet the requirement of 2.5 V output amplitude, an off-chip transformer connects the DAC to the load. The impedance equals 100

3. Distortion mechanism and DAC core design

3.1 Spectral performance of the current cell

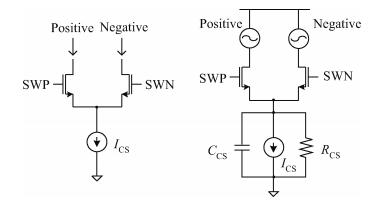

A simple model for the current cell is shown in Fig. 5.

In this model, the current cell contains an ideal current cell and a pair of switches which determine the output current path and the differential voltage between the positive and negative output node. The major non-ideal effect of the current source is the finite frequency-dependent output impedance, which is modeled by

Transistor mismatch of the current sources is a main source of nonlinearity. To meet the INL requirement of the DAC, the relationship between DAC INL_yield and the required accuracy on the current sources can be expressed as[5]:

|

$\frac{\sigma (I)}{I}\leqslant \frac{1}{\sqrt {2^N C}}, \quad C={\rm inv\_norm}\left(0.5+\frac{{\rm INL\_yield}}{2}\right),$ |

(2) |

where

|

$WL = \left[ {\frac{{4A_{{\rm{VT}}}^2}}{{{{\left( {{V_{{\rm{GS}}}} - {V_{{\rm{TH}}}}} \right)}^2}}} + A_\beta ^2} \right]/{\left( {\frac{{\sigma (I)}}{I}} \right)^2}_,$ |

(3) |

in which

The other factor that causes distortion at low frequency is the finite output impedance of DAC current cell

|

${\rm HD}_3 =\left[R_{\rm load} N/ R_{\rm cs} \right]^2.$ |

(4) |

From Eq. (4), it can be seen that the low frequency SFDR can be improved by increasing

Additional performance-degrading effects start to work when the sampling frequency gets high. An assumption of the output impedance can be modeled by the parallel connection of a resistor and a capacitor, and the expression for HD3 can be described as:

|

${\rm HD}_3 =\left[R_{\rm load} N/Z_{\rm cs} \right]^2.$ |

(5) |

For the current sources of 5-bit MSB, to get HD

3.2 Current source implementation

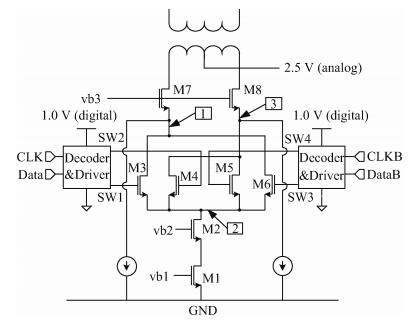

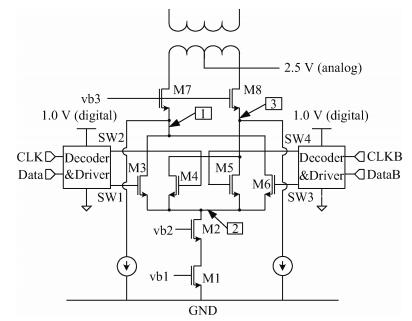

The cascode current source structure is adopted in this design as depicted in Fig. 6. The area of the current cell M1 is determined in a similar way to that described above and the cascode transistor M2 and the switches M3–M6 are minimized to reduce the high-frequency distortion. In addition, a fast switching method is used to reduce the parasitic capacitance[6].

Although a three-cascode-transistor structure can guarantee high impedance at low frequency, M7 and M8 could still cause large parasitic capacitance due to their large size. Therefore, two additional current paths are added to the sources of M7–M8, in which way these two transistors will not be completely switched off and the voltage of node 1 and node 3 will be much more stable. The parasitic capacitor

3.3 Solutions to the data-dependent clock loading effect

Any latch topology presents a load to the buffer that drives the clock input of the latch[8], which depends on whether the state of the latch is about to change or not. This effect will be significant when a large number of latches change with different states. It also becomes one of the most important limitations for high-frequency operation. So here, several circuits are implemented to minimize this effect.

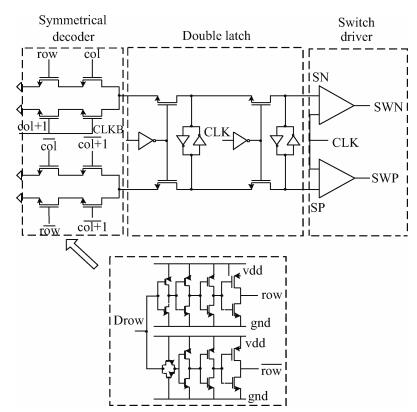

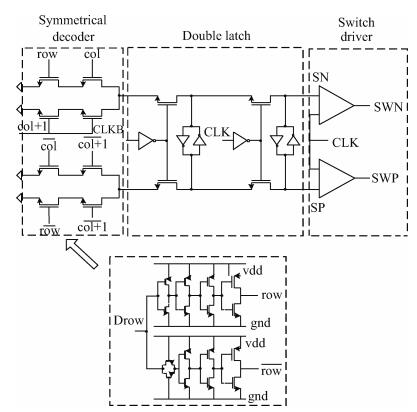

As mentioned in the DAC architecture, row-and-column decoders are used to reduce design complexity and save power. Furthermore, a symmetrical decoding method is adopted, as shown in Fig. 7 to minimize the decoding feed-through effect.

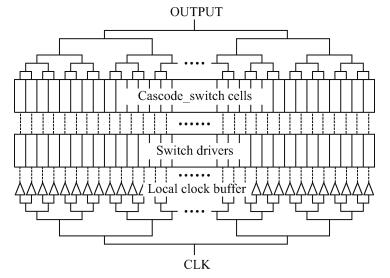

The latch shown in Fig. 7 is adopted to implement the synchronization of the switch-control signals, because it has the shortest clock-to-Q delay and the steepest transition. Although the transition of digital signals still has a finite settling effect at the end of the clock period, it is solved with the double-latch structure. To minimize the sensitivity of the driver to the data-dependent clock load, the clock is local buffered, thus it can enhance the strength of clock signal. Besides that, to minimize the intersymbol interference between successive input codes for achieving low distortion, the input data is also locally converted into a differential equivalent and buffered through a successively scaled buffer, as shown in Fig. 7, in which way it can also improve the switching speed.

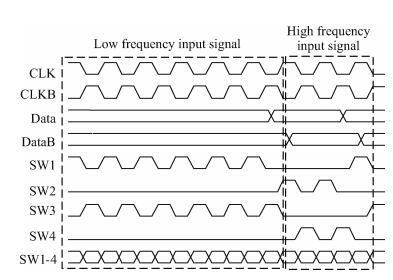

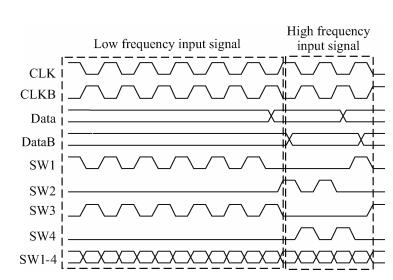

To further reduce the data-dependent clock loading effect, a four-switch method[9] is implemented as shown in Fig. 6 (M3–M6). In this method, two of the four switches change their states, while the other two remain off when the DAC is operating. The input data determines whether the output current flows to one output terminal or the other. It can be seen from Fig. 8 that regardless of whether the input signal is at low frequency or high frequency, the clock has the same load and node 2 in Fig. 6 suffers the same disturbances all the time.

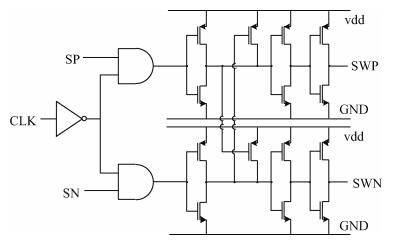

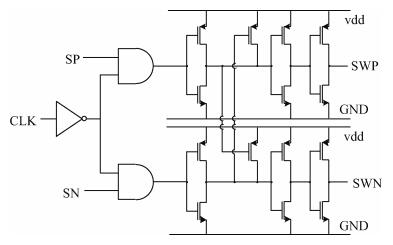

Meanwhile, the crossing point of the switch-control signals is also important. To prevent NMOS switch transistors from turning off at the same time, high crossing switch-control signals are needed, which are provided by the circuit shown in Fig. 9.

3.4 Layout solutions

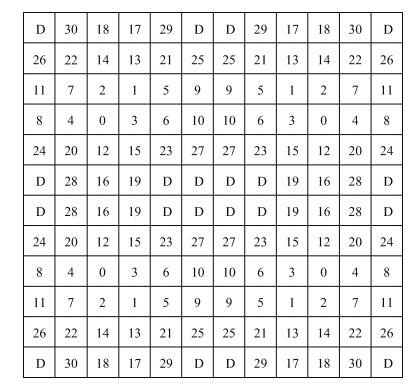

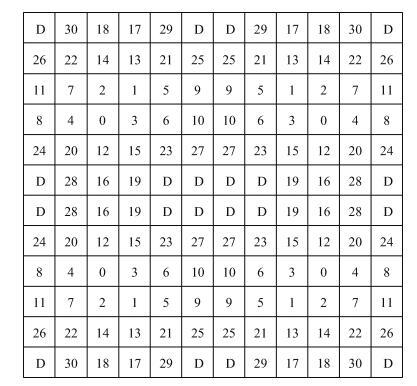

In the DAC design, the matching problem of the layout will have great influence on the chip performance when the DAC is fabricated. In order to ensure transistor-matching, a special layout technique called 'INL bounded switching sequences'[10] is adopted to cancel both the linear and quadratic gradient errors. The layout arrangement of the MSB and ULSB current sources is depicted in Fig. 10.

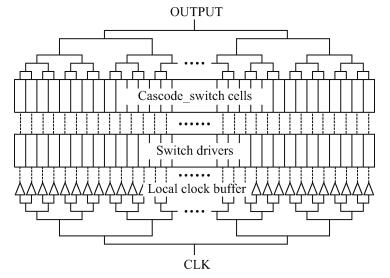

Another layout consideration is routing. According to Ref. [7], the delay differences caused by clock signal and output signal routing will degrade SFDR performance at high-speed operation. So a very tight control over relative timing is necessary. As shown in Fig. 11, binary tree routing method for the clock signal and output signal is adopted here.

4. Experimental results

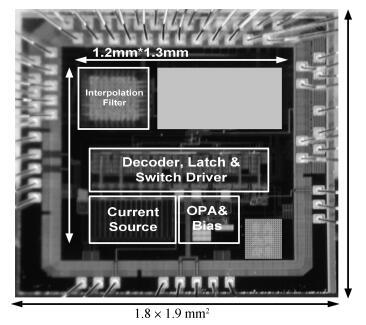

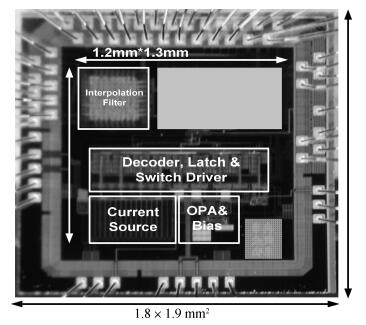

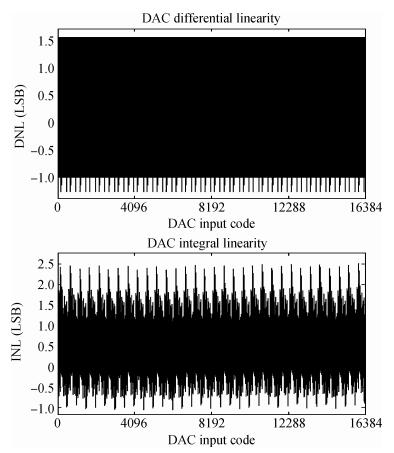

The DAC was fabricated in TSMC 65 nm CMOS technology. Figure 12 is the chip microphotograph, which shows that the core area is 1.2

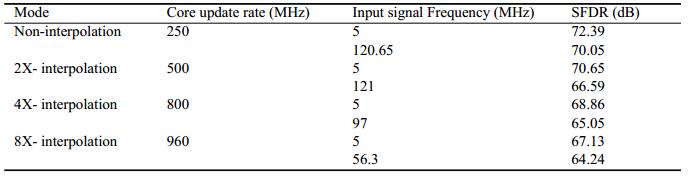

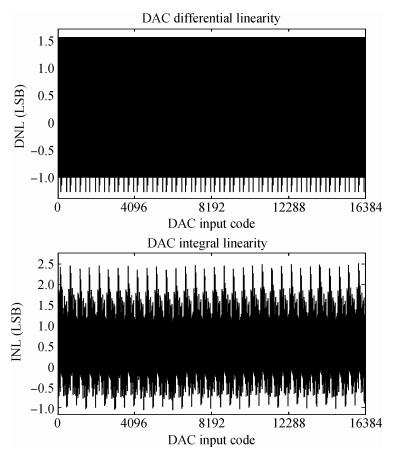

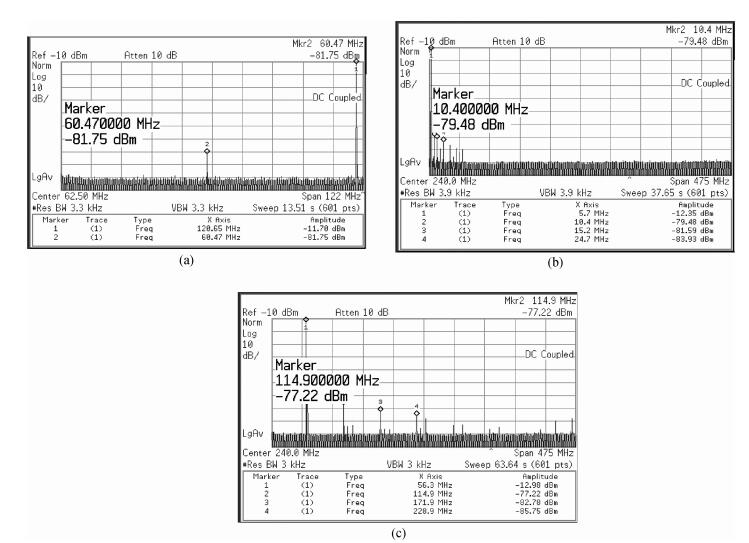

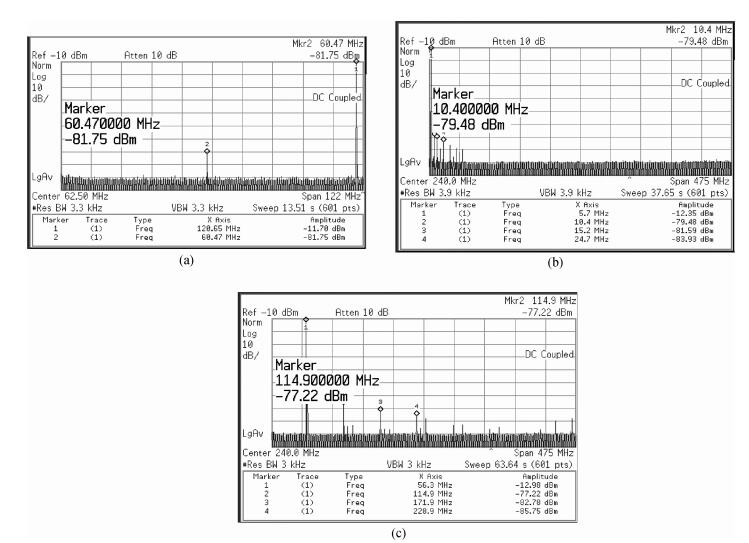

With the programmable digital interpolation filter, the DAC can work under 4 different modes, which are non-interpolation mode, 2x-interpolation mode, 4x-interpolation mode, and 8x-interpolation mode depending on the core update rate. Figure 14(a) shows that the measured SFDR is 70.05 dB for 120.65 MHz input signal when the update rate is 250 MS/s (non-interpolation mode). Under the 8x-interpolation mode, the output spectrum for 5 MHz input signal at 960 MS/s and 56.3 MHz input signal at 960 MS/s are shown in Figs. 14(b) and 14(c), and the SFDRs are 67.13 dB and 64.24 dB, respectively. As can be seen from Fig. 14, SFDR performance is limited by the second-order harmonic distortion. That is because fabrication will cause mismatch and layout and routing are not perfectly symmetrical. To minimize the effect, a better layout technique will be needed.

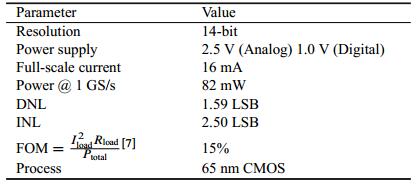

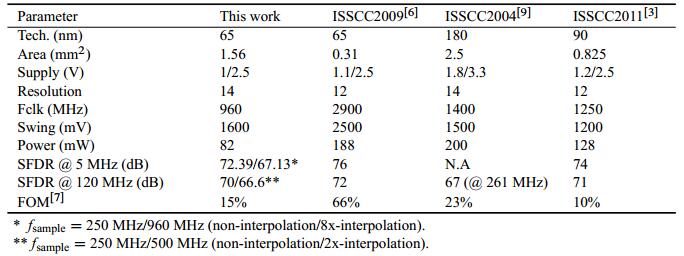

A summarized performance of the programmable DAC and a comparison between this work and other works are listed in Tables 2, 3 and 4. The analog part of the DAC consumes 42 mW from 2.5 V power supply while providing 16 mA full scale current and the digital part consumes 40 mW when the sampling frequency is 1 GHz.

|

|

|

5. Conclusion

This paper presents a programmable 14-bit 1 GS/s DAC, which features a selectable interpolation rate (2x/4x/8x). A "fast switching" technique is adopted to reduce parasitic capacitance at high input frequency and the data-dependent clock loading effect is minimized by various methods such as symmetrical decoding, double-latch, local buffered clock and switch sequence control. The layout techniques for the current source transistors, the clock binary tree and the output signal binary tree are implemented to further improve SFDR at high frequency. The full-scale output current is 16 mA and the power consumption is 82 mW at 1 GS/s. The converter is designed in TSMC 65 nm technology and has a core area of 1.56 mm

DownLoad:

DownLoad:

DownLoad:

DownLoad:

DownLoad:

DownLoad: