Device scaling is an important part of the very large scale integration (VLSI) design to boost up the success path of VLSI industry, which results in denser and faster integration of the devices. As technology node moves towards the very deep submicron region, leakage current and circuit reliability become the key issues. Both are increasing with the new technology generation and affecting the performance of the overall logic circuit. The VLSI designers must keep the balance in power dissipation and the circuit's performance with scaling of the devices. In this paper, different scaling methods are studied first. These scaling methods are used to identify the effects of those scaling methods on the power dissipation and propagation delay of the CMOS buffer circuit. For mitigating the power dissipation in scaled devices, we have proposed a reliable leakage reduction low power transmission gate (LPTG) approach and tested it on complementary metal oxide semiconductor (CMOS) buffer circuit. All simulation results are taken on HSPICE tool with Berkeley predictive technology model (BPTM) BSIM4 bulk CMOS files. The LPTG CMOS buffer reduces 95.16% power dissipation with 84.20% improvement in figure of merit at 32 nm technology node. Various process, voltage and temperature variations are analyzed for proving the robustness of the proposed approach. Leakage current uncertainty decreases from 0.91 to 0.43 in the CMOS buffer circuit that causes large circuit reliability.

One of the core semiconductor devices is the electrostatic chuck. It has been widely used in plasma-based and vacuum-based semiconductor processing. The electrostatic chuck plays an important role in adsorbing and cooling/heating wafers, and has technical advantages on non-edge exclusion, high reliability, wafer planarity, particles reduction and so on. This article extracts key design elements from the existing knowledge and techniques of electrostatic chuck by the method proposed by Paul and Beitz, and establishes a design space systematically. The design space is composed of working objects, working principles and working structures. The working objects involve electrostatic chuck components and materials, classifications, and relevant properties; the working principles involve clamping force, residual force, and temperature control; the working structures describe how to compose an electrostatic chuck and to fulfill the overall functions. The systematic design space exhibits the main issues during electrostatic chuck design. The design space will facilitate and inspire designers to improve the design quality and shorten the design time in the conceptual design.

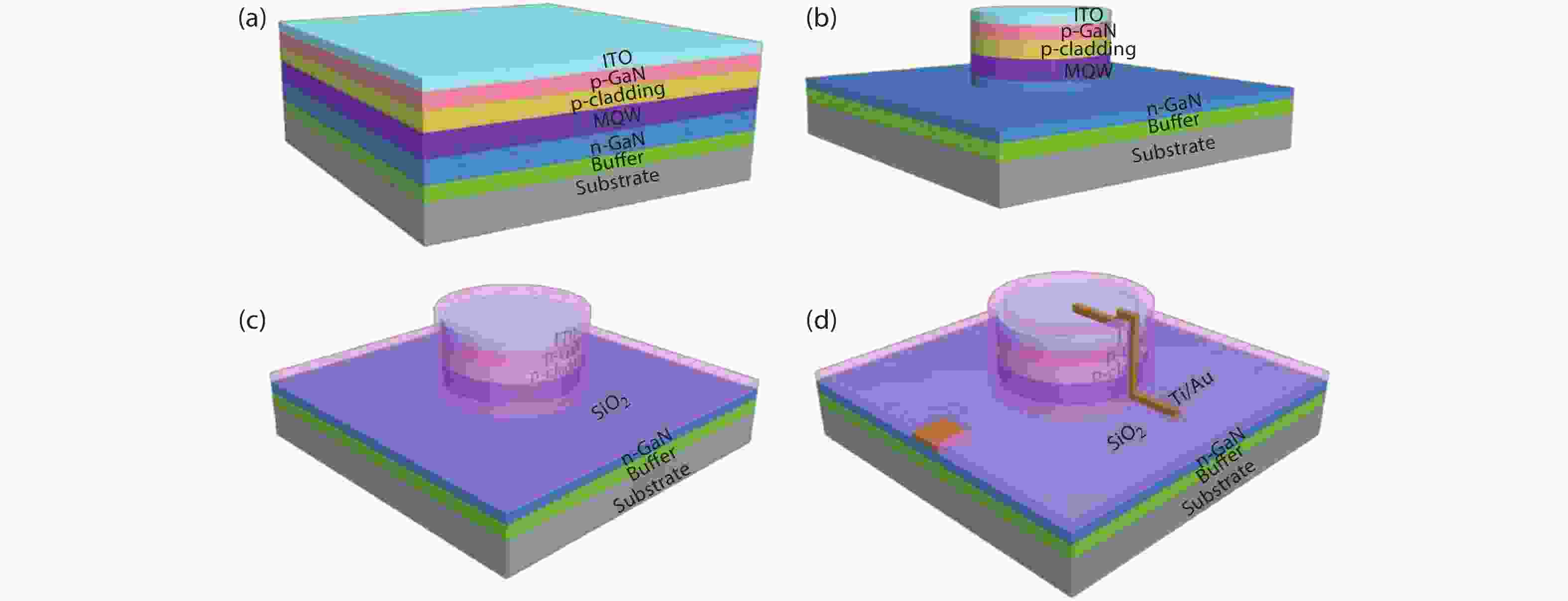

In this work, we design and fabricate a deep ultraviolet (DUV) light-emitting array consisting of 10 × 10 micro-LEDs (μ-LEDs) with each device having 20 μm in diameter. Strikingly, the array demonstrates a significant enhancement of total light output power by nearly 52% at the injection current of 100 mA, in comparison to a conventional large LED chip whose emitting area is the same as the array. A much higher (~22%) peak external quantum efficiency, as well as a smaller efficiency droop for μ-LED array, was also achieved. The numerical calculation reveals that the performance boost can be attributed to the higher light extraction efficiency at the edge of each μ-LED. Additionally, the far-field pattern measurement shows that the μ-LED array possesses a better forward directionality of emission. These findings shed light on the enhancement of the DUV LEDs performance and provide new insights in controlling the light behavior of the μ-LEDs.

Since the invention of amorphous indium–gallium–zinc–oxide (IGZO) based thin-film transistors (TFTs) by Hideo Hosono in 2004, investigations on the topic of IGZO TFTs have been rapidly expanded thanks to their high electrical performance, large-area uniformity, and low processing temperature. This article reviews the recent progress and major trends in the field of IGZO-based TFTs. After a brief introduction of the history of IGZO and the main advantages of IGZO-based TFTs, an overview of IGZO materials and IGZO-based TFTs is given. In this part, IGZO material electron travelling orbitals and deposition methods are introduced, and the specific device structures and electrical performance are also presented. Afterwards, the recent advances of IGZO-based TFT applications are summarized, including flat panel display drivers, novel sensors, and emerging neuromorphic systems. In particular, the realization of flexible electronic systems is discussed. The last part of this review consists of the conclusions and gives an outlook over the field with a prediction for the future.

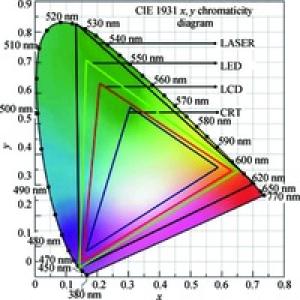

Due to the excellent optoelectronic properties, fast response time, outstanding power efficiency and high stability, micro-LED plays an increasingly important role in the new generation of display technology compared with LCD and OLED display. This paper mainly introduces the preparation methods of the GaN-based micro-LED array, the optoelectronic characteristics, and several key technologies to achieve full-color display, such as transfer printing, color conversion by quantum dot and local strain engineering.

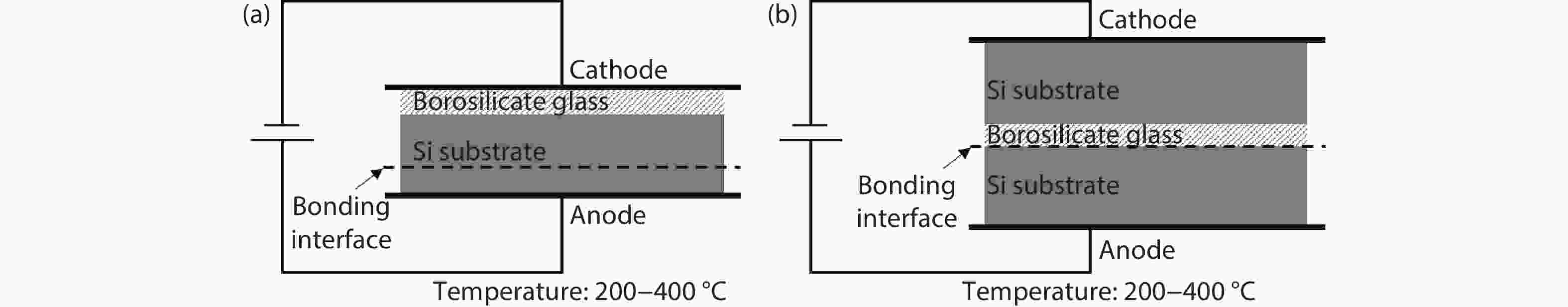

The heterogeneous integration of III–V devices with Si-CMOS on a common Si platform has shown great promise in the new generations of electrical and optical systems for novel applications, such as HEMT or LED with integrated control circuitry. For heterogeneous integration, direct wafer bonding (DWB) techniques can overcome the materials and thermal mismatch issues by directly bonding dissimilar materials systems and device structures together. In addition, DWB can perform at wafer-level, which eases the requirements for integration alignment and increases the scalability for volume production. In this paper, a brief review of the different bonding technologies is discussed. After that, three main DWB techniques of single-, double- and multi-bonding are presented with the demonstrations of various heterogeneous integration applications. Meanwhile, the integration challenges, such as micro-defects, surface roughness and bonding yield are discussed in detail.

This paper presents a review and discussion for high-speed photodetectors and their applications on optical communications and microwave photonics. A detailed and comprehensive demonstration of high-speed photodetectors from development history, research hotspots to packaging technologies is provided to the best of our knowledge. A few typical applications based on photodetectors are also illustrated, such as free-space optical communications, radio over fiber and millimeter terahertz signal generation systems.

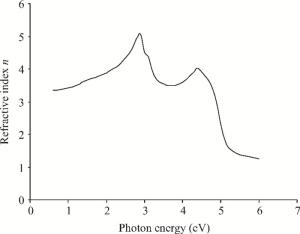

We have investigated the optical properties of gallium arsenide (GaAs) in the photon energy range 0.6-6.0 eV. We obtained a refractive index which has a maximum value of 5.0 at a photon energy of 3.1 eV; an extinction coefficient which has a maximum value of 4.2 at a photon energy of 5.0 eV; the dielectric constant, the real part of the complex dielectric constant has a maximum value of 24 at a photon energy of 2.8 eV and the imaginary part of the complex dielectric constant has a maximum value of 26.0 at a photon energy of 4.8 eV; the transmittance which has a maximum value of 0.22 at a photon energy of 4.0 eV; the absorption coefficient which has a maximum value of 0.22×108 m-1 at a photon energy of 4.8 eV, the reflectance which has a maximum value of 0.68 at 5.2eV; the reflection coefficient which has a maximum value of 0.82 at a photon energy of 5.2 eV; the real part of optical conductivity has a maximum value of 14.2×1015 at 4.8 eV and the imaginary part of the optical conductivity has a maximum value of 6.8×1015 at 5.0 eV. The values obtained for the optical properties of GaAs are in good agreement with other results.

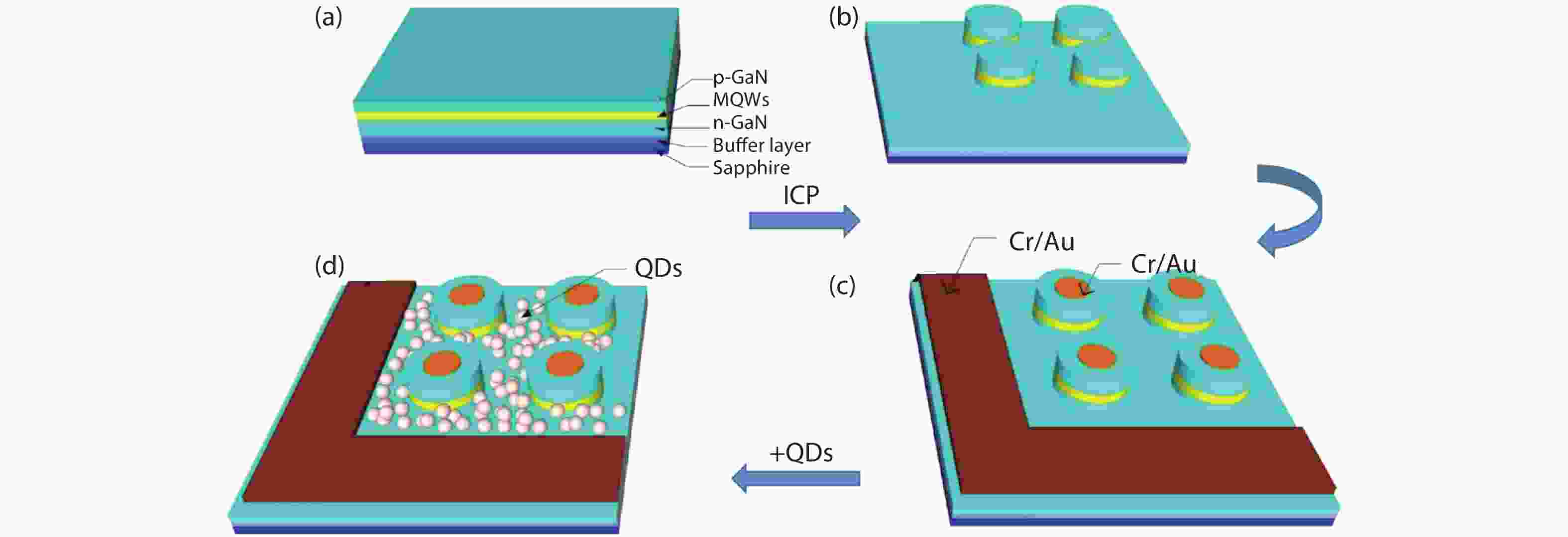

Hybrid white micro-pillar structure light emitting diodes (LEDs) have been manufacture utilizing blue micro-LEDs arrays integrated with 580 nm CIS ((CuInS2-ZnS)/ZnS) core/shell quantum dots. The fabricated hybrid white micro-LEDs have good electrical properties, which are manifested in relatively low turn-on voltage and reverse leakage current. High-quality hybrid white light emission has been demonstrated by the hybrid white micro-LEDs after a systemic optimization, in which the corresponding color coordinates are calculated to be (0.3303, 0.3501) and the calculated color temperature is 5596 K. This result indicates an effective way to achieve high-performance white LEDs and shows great promise in a large range of applications in the future including micro-displays, bioinstrumentation and visible light communication.

The super junction (SJ) has been recognized as the " milestone” of the power MOSFET, which is the most important innovation concept of the voltage-sustaining layer (VSL). The basic structure of the SJ is a typical junction-type VSL (J-VSL) with the periodic N and P regions. However, the conventional VSL is a typical resistance-type VSL (R-VSL) with only an N or P region. It is a qualitative change of the VSL from the R-VSL to the J-VSL, introducing the bulk depletion to increase the doping concentration and optimize the bulk electric field of the SJ. This paper firstly summarizes the development of the SJ, and then the optimization theory of the SJ is discussed for both the vertical and the lateral devices, including the non-full depletion mode, the minimum specific on-resistance optimization method and the equivalent substrate model. The SJ concept breaks the conventional " silicon limit” relationship of Ron∝VB2.5, showing a quasi-linear relationship of Ron∝VB1.03.

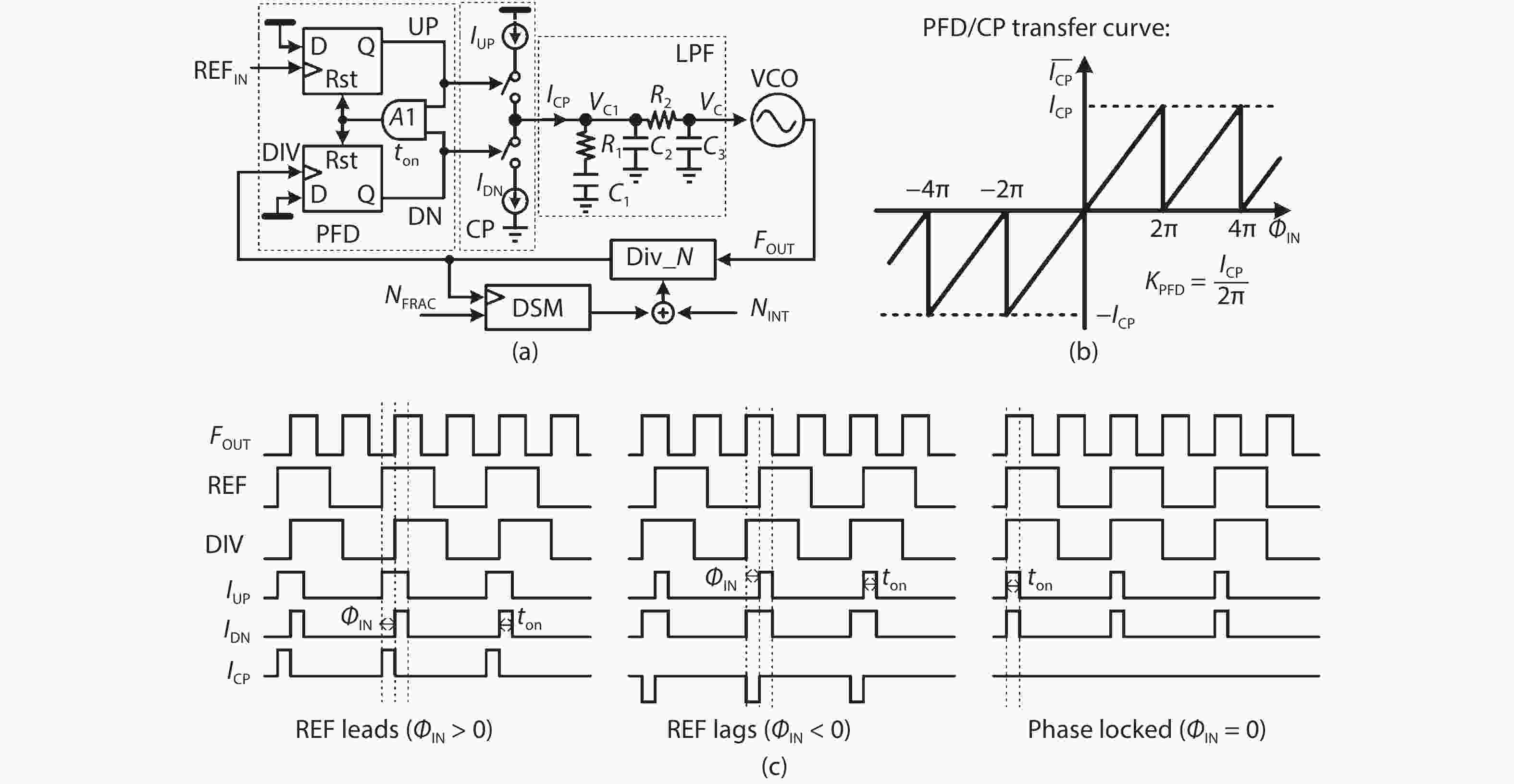

CMOS analog and mixed-signal phase-locked loops (PLL) are widely used in varies of the system-on-chips (SoC) as the clock generator or frequency synthesizer. This paper presents an overview of the AMS-PLL, including: 1) a brief introduction of the basics of the charge-pump based PLL, which is the most widely used AMS-PLL architecture due to its simplicity and robustness; 2) a summary of the design issues of the basic CPPLL architecture; 3) a systematic introduction of the techniques for the performance enhancement of the CPPLL; 4) a brief overview of ultra-low-jitter AMS-PLL architectures which can achieve lower jitter (< 100 fs) with lower power consumption compared with the CPPLL, including the injection-locked PLL (ILPLL), sub-sampling (SSPLL) and sampling PLL (SPLL); 5) a discussion about the consideration of the AMS-PLL architecture selection, which could help designers meet their performance requirements.

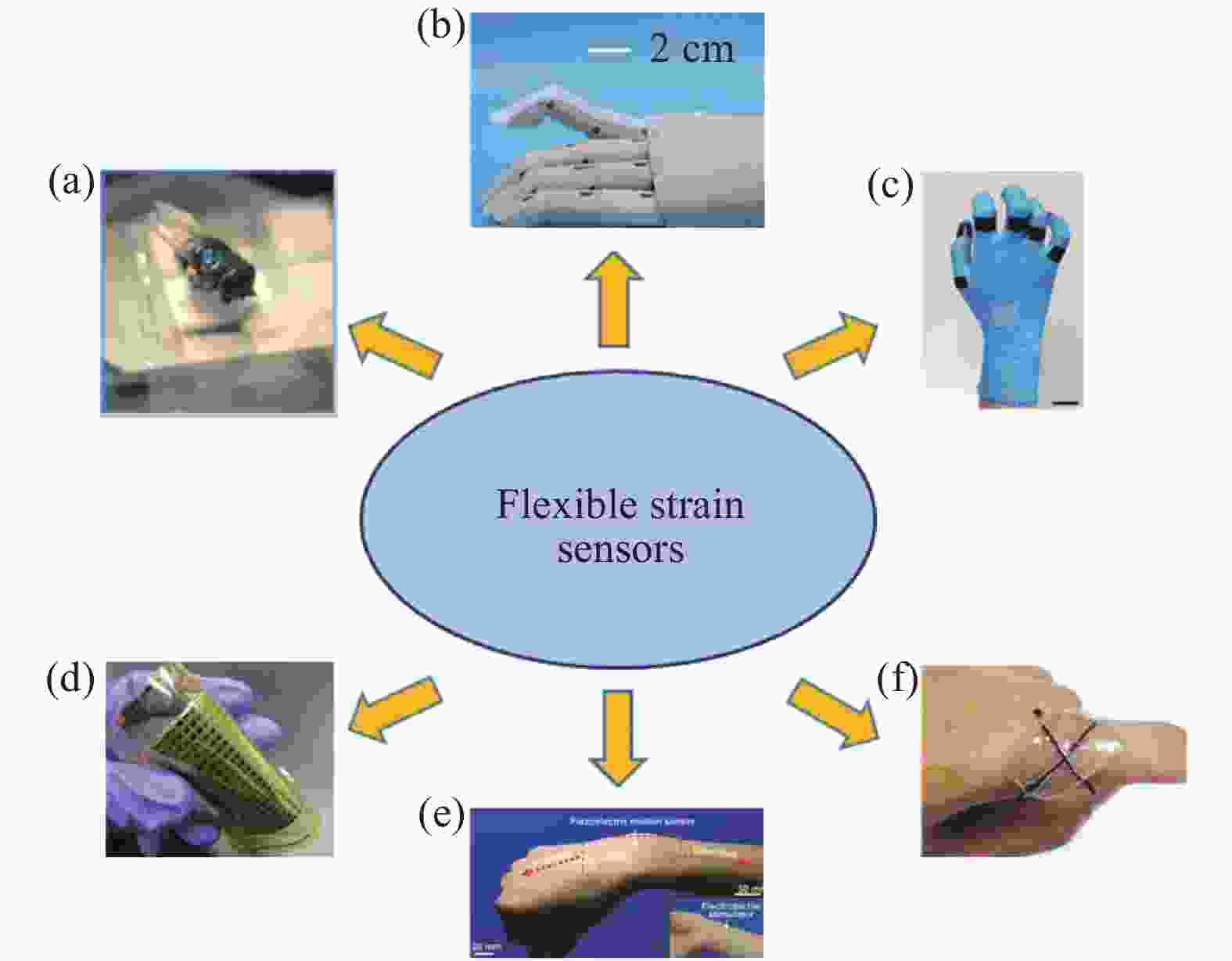

With the rapid development of human artificial intelligence and the inevitably expanding markets, the past two decades have witnessed an urgent demand for the flexible and wearable devices, especially the flexible strain sensors. Flexible strain sensors, incorporated the merits of stretchability, high sensitivity and skin-mountable, are emerging as an extremely charming domain in virtue of their promising applications in artificial intelligent realms, human-machine systems and health-care devices. In this review, we concentrate on the transduction mechanisms, building blocks of flexible physical sensors, subsequently property optimization in terms of device structures and sensing materials in the direction of practical applications. Perspectives on the existing challenges are also highlighted in the end.

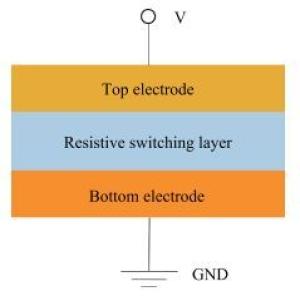

The resistive random access memory (RRAM) device has been widely studied due to its excellent memory characteristics and great application potential in different fields. In this paper, resistive switching materials, switching mechanism, and memory characteristics of RRAM are discussed. Recent research progress of RRAM in high-density storage and nonvolatile logic application are addressed. Technological trends are also discussed.

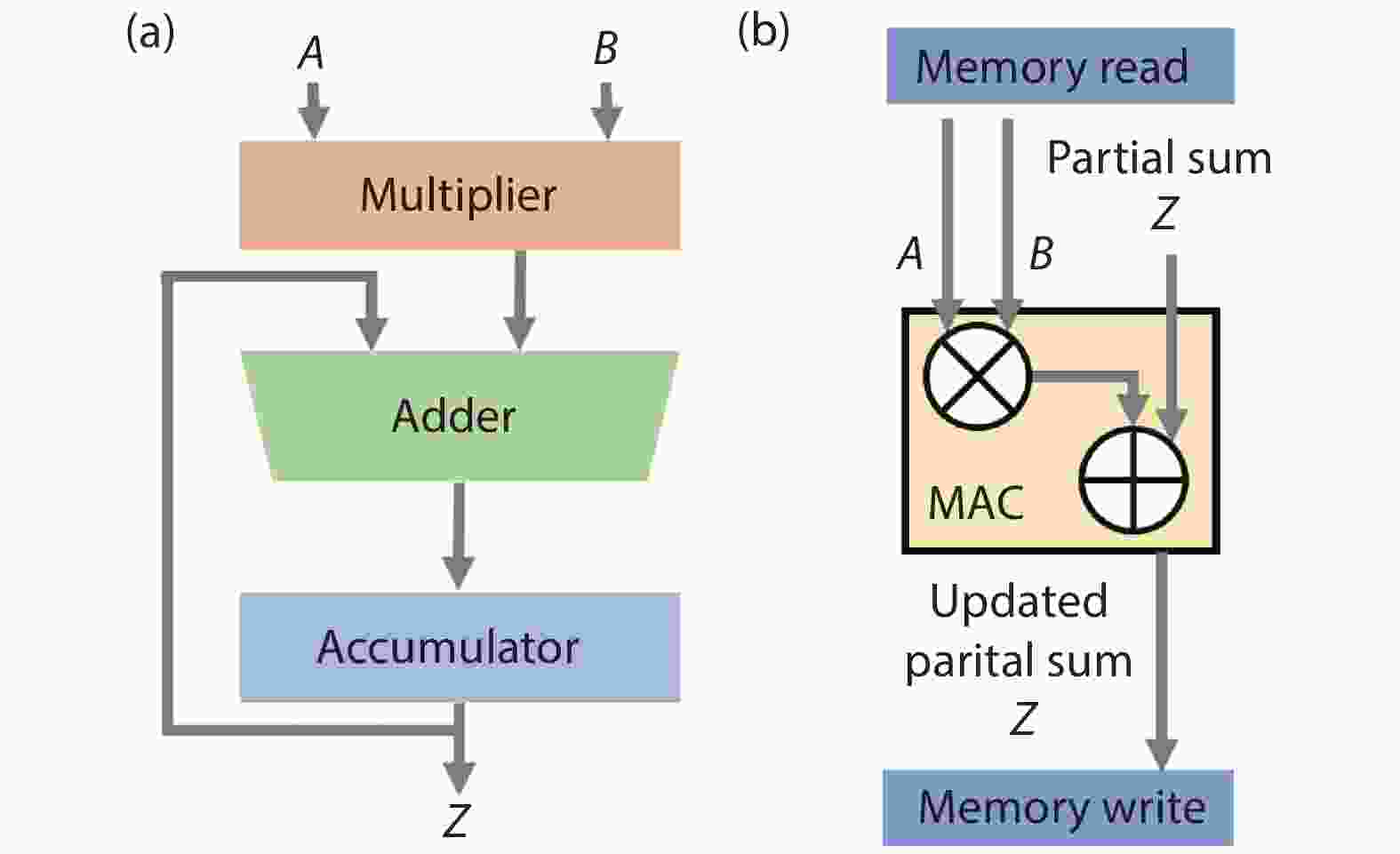

Memristors are now becoming a prominent candidate to serve as the building blocks of non-von Neumann in-memory computing architectures. By mapping analog numerical matrices into memristor crossbar arrays, efficient multiply accumulate operations can be performed in a massively parallel fashion using the physics mechanisms of Ohm’s law and Kirchhoff’s law. In this brief review, we present the recent progress in two niche applications: neural network accelerators and numerical computing units, mainly focusing on the advances in hardware demonstrations. The former one is regarded as soft computing since it can tolerant some degree of the device and array imperfections. The acceleration of multiple layer perceptrons, convolutional neural networks, generative adversarial networks, and long short-term memory neural networks are described. The latter one is hard computing because the solving of numerical problems requires high-precision devices. Several breakthroughs in memristive equation solvers with improved computation accuracies are highlighted. Besides, other nonvolatile devices with the capability of analog computing are also briefly introduced. Finally, we conclude the review with discussions on the challenges and opportunities for future research toward realizing memristive analog computing machines.

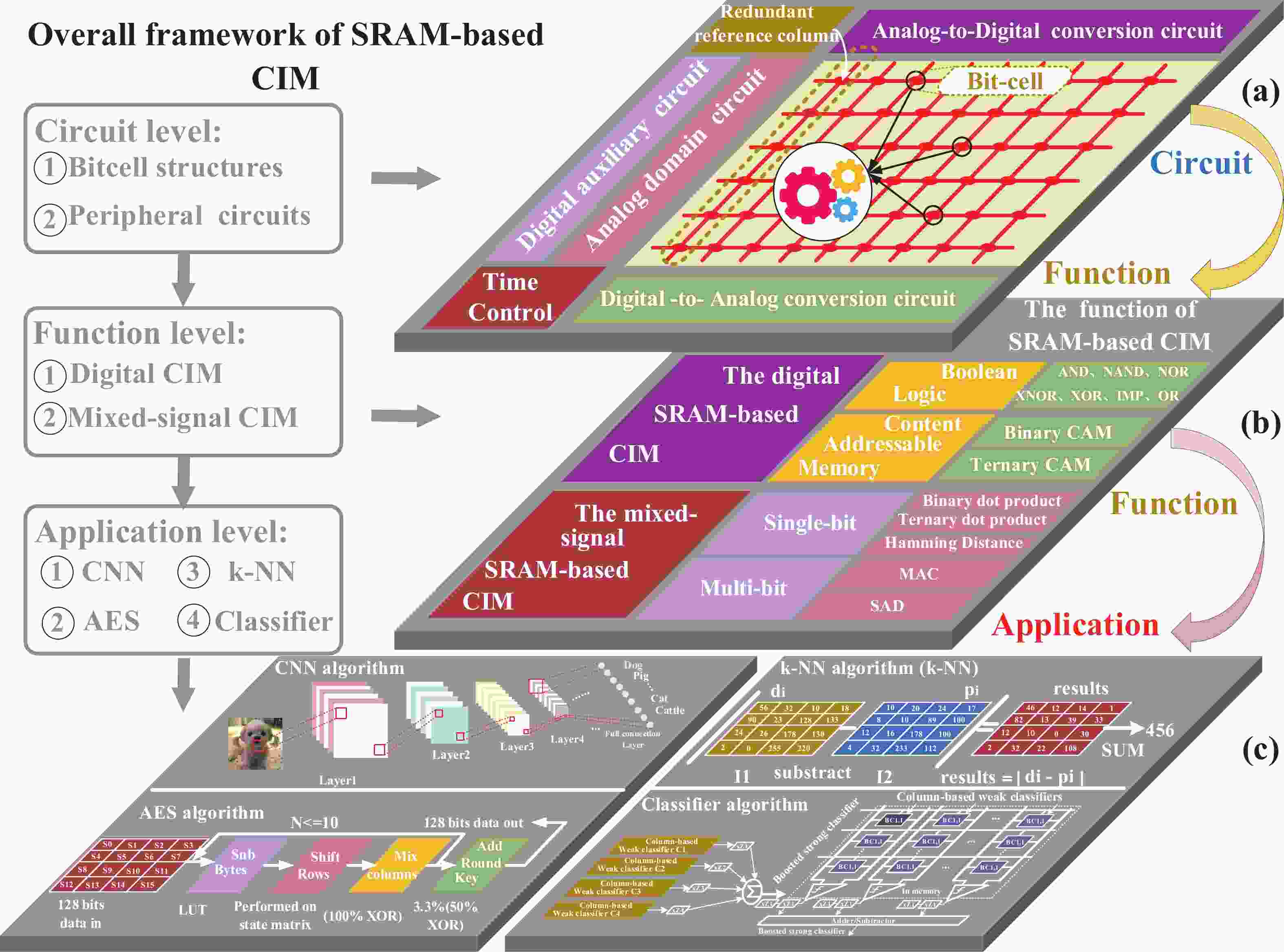

Artificial intelligence (AI) processes data-centric applications with minimal effort. However, it poses new challenges to system design in terms of computational speed and energy efficiency. The traditional von Neumann architecture cannot meet the requirements of heavily data-centric applications due to the separation of computation and storage. The emergence of computing in-memory (CIM) is significant in circumventing the von Neumann bottleneck. A commercialized memory architecture, static random-access memory (SRAM), is fast and robust, consumes less power, and is compatible with state-of-the-art technology. This study investigates the research progress of SRAM-based CIM technology in three levels: circuit, function, and application. It also outlines the problems, challenges, and prospects of SRAM-based CIM macros.

A new simulation method and test instrument has been adopted to verify the traditional stress simulation in FinFET. First, a new algorithm named lattice kinetic Monte Carlo (LKMC) is used to simulate the SiGe epitaxy in source/drain regions and the stress distribution is consequently extracted after the LKMC simulation. Systematic comparison between the traditional polyhedron method and the LKMC method is carried out. The results confirm that extracted stress from both methods is consistent, which verifies the validity of traditional polyhedron method for the purpose of simulating stress in FinFET. In the following experiment, p-type FinFETs with SiGe stressors in source/drain regions are fabricated. The nano beam diffraction (NBD) method is employed to characterize the strain in Si fin. The strain value from the NBD test agrees well with the value extracted from traditional polyhedron simulation.

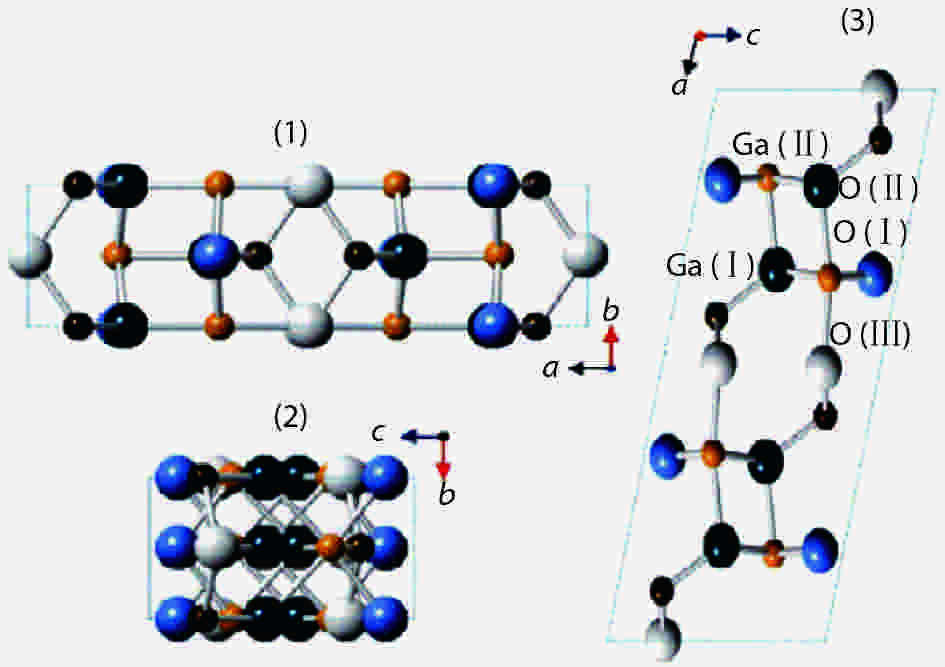

The rapid development of bulk β-Ga2O3 crystals has attracted much attention to their use as ultra-wide bandgap materials for next-generation power devices owing to its large bandgap (~ 4.9 eV) and large breakdown electric field of about 8 MV/cm. Low cost and high quality of large β-Ga2O3 single-crystal substrates can be attained by melting growth techniques widely used in the industry. In this paper, we first present an overview of the properties of β-Ga2O3 crystals in bulk form. We then describe the various methods for producing bulk β-Ga2O3 crystals and their applications. Finally, we will present a future perspective of the research in the area in the area of single crystal growth.

Analytical expressions of electron transmittance and tunneling current in an anisotropic TiNx/HfO2/SiO2/p-Si(100) metal–oxide–semiconductor (MOS) capacitor were derived by considering the coupling of transverse and longitudinal energies of an electron. Exponential and Airy wavefunctions were utilized to obtain the electron transmittance and the electron tunneling current. A transfer matrix method, as a numerical approach, was used as a benchmark to assess the analytical approaches. It was found that there is a similarity in the transmittances calculated among exponential- and Airy-wavefunction approaches and the TMM at low electron energies. However, for high energies, only the transmittance calculated by using the Airy-wavefunction approach is the same as that evaluated by the TMM. It was also found that only the tunneling currents calculated by using the Airy-wavefunction approach are the same as those obtained under the TMM for a range of oxide voltages. Therefore, a better analytical description for the tunneling phenomenon in the MOS capacitor is given by the Airy-wavefunction approach. Moreover, the tunneling current density decreases as the titanium concentration of the TiNx metal gate increases because the electron effective mass of TiNx decreases with increasing nitrogen concentration. In addition, the mass anisotropy cannot be neglected because the tunneling currents obtained under the isotropic and anisotropic masses are very different.

Recently, many groups have focused on the development of GaN-based green LDs to meet the demand for laser display. Great progresses have been achieved in the past few years even that many challenges exist. In this article, we analysis the challenges to develop GaN-based green LDs, and then the approaches to improve the green LD structure in the aspect of crystalline quality, electrical properties, and epitaxial layer structure are reviewed, especially the work we have done.

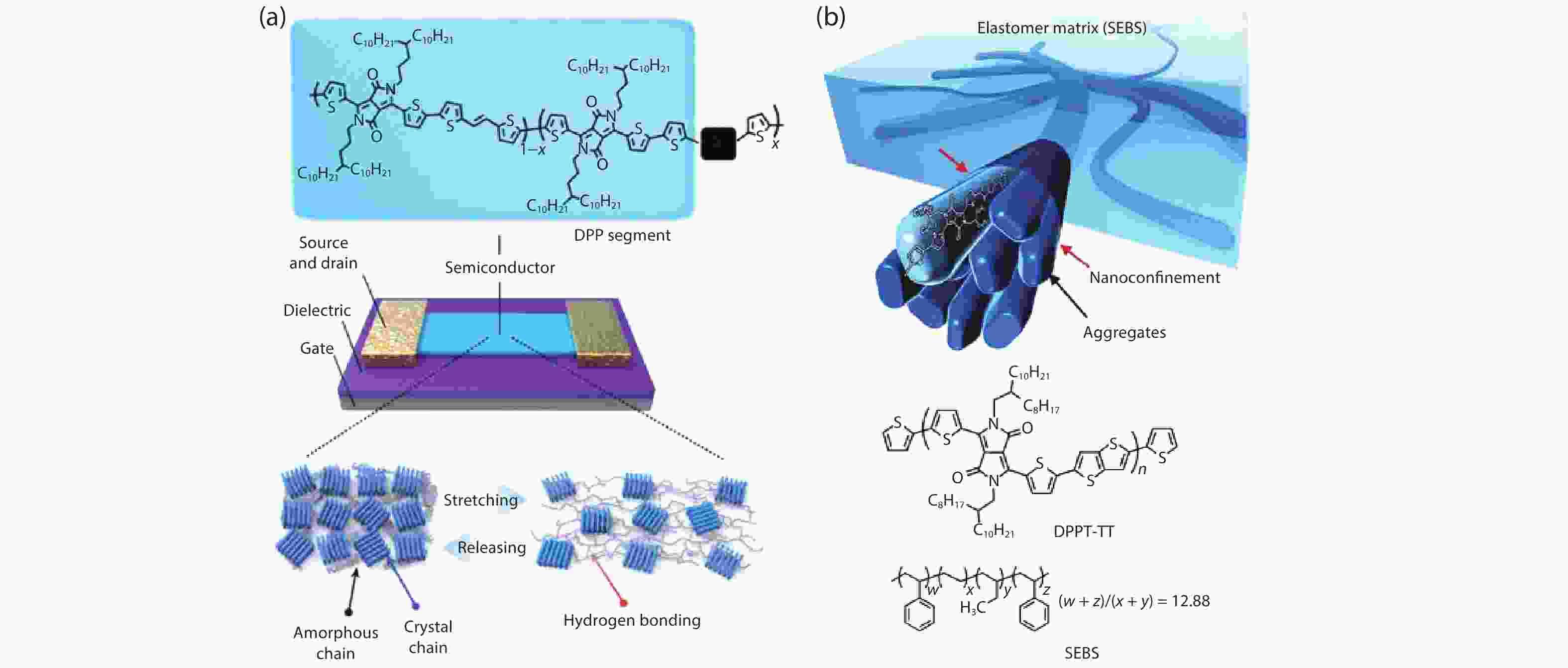

Current electronics are driven by advanced microfabrication for fast and efficient information processing. In spite of high performance, these wafer-based devices are rigid, non-degradable, and unable to autonomous repair. Skin-inspired electronics have emerged as a new class of devices and systems for next-generation flexible and wearable electronics. The technology gains inspiration from the structures, properties, and sensing mechanisms of the skin, which may find a broad range of applications in cutting-edge fields such as healthcare monitoring, human-machine interface, and soft robotics/prostheses. Practical demands have fueled the development of electronic materials with skin-like properties in terms of stretchability, self-healing capability, and biodegradability. These materials provide the basis for functional sensors with innovative and biomimetic designs. Further system-level integrations and optimizations enable new forms of electronics for real-world applications. This review summarizes recent advancements in this active area and speculates on future directions.

- First

- Prev

- 1

- 2

- 3

- 4

- 5

- Next

- Last

- Total: 5

- To

- Go