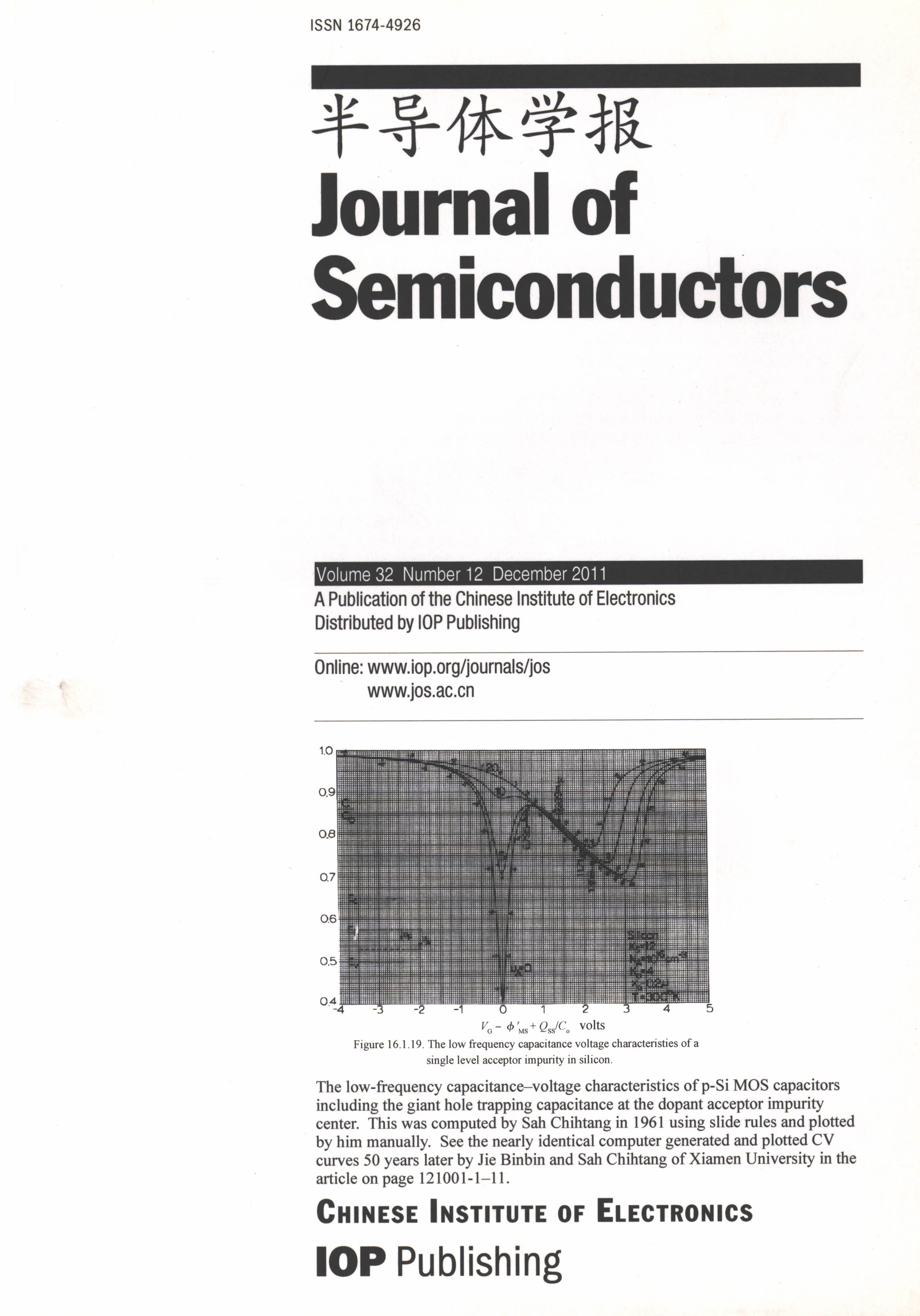

Low-frequency and high-frequency Capacitance-Voltage (C-V) curves of Metal-Oxide-Semiconductor Capacitors (MOSC), including electron and hole trapping at the dopant donor and acceptor impurities, are presented to illustrate giant trapping capacitances, from > 0.01Cox to > 10Cox. Five device and materials parameters are varied for fundamental trapping parameter characterization, and electrical and optical signal processing applications. Parameters include spatially constant concentration of the dopant-donor-impurity electron trap, NDD, the ground state electron trapping energy level depth measured from the conduction band edge, EC-ED, the degeneracy of the trapped electron at the ground state, gD, the device temperature, T, and the gate oxide thickness, xox.

Low-frequency and high-frequency capacitance-voltage curves of Metal-Oxide-Semiconductor Capacitors are presented to illustrate giant electron and hole trapping capacitances at many simultaneously present two-charge-state and one-trapped-carrier, or one-energy-level impurity species. Models described include a donor electron trap and an acceptor hole trap, both donors, both acceptors, both shallow energy levels, both deep, one shallow and one deep, and the identical donor and acceptor. Device and material parameters are selected to simulate chemically and physically realizable capacitors for fundamental trapping parameter characterizations and for electrical and optical signal processing applications.

Research on the magnetron cavity used in the rubidium atomic frequency standards is developed, through which the main characteristic parameters of the magnetron cavity are studied, mainly including the resonant frequency, quality factor and oscillation mode. The resonant frequency and quality factor of the magnetron cavity were calculated, and the test results of the resonant frequency agreed well with the calculation theory. The test results also show that the resonant frequency of the magnetron cavity can be attenuated to 6.835 GHz, which is the resonant frequency of the rubidium atoms, and the Q-factor can be attenuated to 500-1000. The oscillation mode is a typical TE011 mode and is the correct mode needed for the rubidium atomic frequency standard. Therefore these derivative magnetron cavities meet the requirements of the rubidium atomic frequency standards well.

Van der Pauw's function is often used in the measurement of a semiconductor's resistivity. However, it is difficult to obtain its value from voltage measurements because it has an implicit form. If it can be expressed as a polynomial, a semiconductor's resistivity can be obtained from such measurements. Normally, five orders of the abscissa can provide sufficient precision during the expression of any non-linear function. Therefore, the key is to determine the coefficients of the polynomial. By taking five coefficients as weights to construct a neuronetwork, neurocomputing has been used to solve this problem. Finally, the polynomial expression for van der Pauw's function is obtained.

The Seebeck coefficient is determined from silicon microchannel plates (Si MCPs) prepared by photo-assisted electrochemical etching at room temperature (25 ℃). The coefficient of the sample with a pore size of 5 × 5 μm2, spacing of 1 μm and thickness of about 150 μm is -852 μV/K along the edge of the square pore. After doping with boron and phosphorus, the Seebeck coefficient diminishes to 256 μV/K and -117 μV/K along the edge of the square pore, whereas the electrical resistivity values are 7.5 × 10-3 Ω·cm and 1.9 × 10-3 Ω·cm, respectively. Our data imply that the Seebeck coefficient of the Si MCPs is related to the electrical resistivity and is consistent with that of bulk silicon. Based on the boron and phosphorus doped samples, a simple device is fabricated to connect the two type Si MCPs to evaluate the Peltier effect. When a proper current passes through the device, the Peltier effect is evidently observed. Based on the experimental data and the theoretical calculation, the estimated intrinsic figure of merit ZT of the unicouple device and thermal conductivity of the Si MCPs are 0.007 and 50 W/(m·K), respectively.

Different morphologies of comb-like ZnO and oriented ZnO nano-arrays such as ZnO nanoneedles and ZnO nanorods were synthesized by using flexible thermal evaporation method via simply adjusting the temperature and oxygen content. The ZnO nanorods arrays have the lowest turn-on field, highest current density and the largest emission efficiency owning to its good contact with the substrate and relatively weaker field screening effects. The experiments show that the morphologies and orientation of one-dimensional (1D) ZnO nanomaterials have considerable effects on the turn-on field and the emission current density, and the nanoarray also contributes to electrons emission. The results could be valuable for the application of ZnO nanorod arrays as cathode materials in field emission based devices.

Selected area laser-crystallized polycrystalline silicon (p-Si) thin films were prepared by the third harmonics (355 nm wavelength) generated by a solid-state pulsed Nd:YAG laser. Surface morphologies of 400 nm thick films after laser irradiation were analyzed. Raman spectra show that film crystallinity is improved with increase of laser energy. The optimum laser energy density is sensitive to the film thickness. The laser energy density for efficiently crystallizing amorphous silicon films is between 440-634 mJ/cm2 for 300 nm thick films and between 777-993 mJ/cm2 for 400 nm thick films. The optimized laser energy density is 634, 975 and 1571 mJ/cm2 for 300, 400 and 500 nm thick films, respectively.

Nanoscale refinement on a (100) oriented silicon-on-insulator (SOI) wafer was introduced by using tetra-methyl-ammonium hydroxide (TMAH, 25 wt%) anisotropic silicon etchant, with temperature kept at 50 ℃ to achieve precise etching of the (111) crystal plane. Specifically for a silicon nanowire (SiNW) with oxide sidewall protection, the in situ TMAH process enabled effective size reduction in both lateral (2.3 nm/min) and vertical (1.7 nm/min) dimensions. A sub-50 nm SiNW with a length of microns with uniform triangular cross-section was achieved accordingly, yielding enhanced field effect transistor (FET) characteristics in comparison with its 100 nm-wide pre-refining counterpart, which demonstrated the feasibility of this highly controllable refinement process. Detailed examination revealed that the high surface quality of the (111) plane, as well as the bulk depletion property should be the causes of this electrical enhancement, which implies the great potential of the as-made cost-effective SiNW FET device in many fields.

The current through a metal-semiconductor junction is mainly due to the majority carriers. Three distinctly different mechanisms exist in a Schottky diode: diffusion of the semiconductor carriers in metal, thermionic emission-diffusion (TED) of carriers through a Schottky gate, and a mechanical quantum that pierces a tunnel through the gate. The system was solved by using a coupled Poisson-Boltzmann algorithm. Schottky BH is defined as the difference in energy between the Fermi level and the metal band carrier majority of the metal-semiconductor junction to the semiconductor contacts. The insulating layer converts the MS device in an MIS device and has a strong influence on its current-voltage (I-V) and the parameters of a Schottky barrier from 3.7 to 15 eV. There are several possible reasons for the error that causes a deviation of the ideal behaviour of Schottky diodes with and without an interfacial insulator layer. These include the particular distribution of interface states, the series resistance, bias voltage and temperature. The GaAs and its large concentration values of trap centers will participate in an increase in the process of thermionic electrons and holes, which will in turn act on the I-V characteristic of the diode, and an overflow maximum value [NT = 3 × 1020] is obtained. The I-V characteristics of Schottky diodes are in the hypothesis of a parabolic summit.

This paper investigates the effect of a non-uniform gate-finger spacing layout structure on the avalanche breakdown performance of RF CMOS technology. Compared with a standard multi-finger device with uniform gate-finger spacing, a device with non-uniform gate-finger spacing represents an improvement of 8.5% for the drain-source breakdown voltage (BVds) and of 20% for the thermally-related drain conductance. A novel compact model is proposed to accurately predict the variation of BV_ds with the total area of devices, which is dependent on the different finger spacing sizes. The model is verified and validated by the excellent match between the measured and simulated avalanche breakdown characteristics for a set of uniform and non-uniform gate-finger spacing arranged nMOSFETs.

We report high performance InAlN/GaN HEMTs grown on sapphire substrates. The lattice-matched InAlN/GaN HEMT sample showed a high 2DEG mobility of 1210 cm2/(V·s) under a sheet density of 2.6 × 1013 cm-2. Large signal load-pull measurements for a (2 × 100 μm) × 0.25 μm device have been conducted with a drain voltage of 24 V at 10 GHz. The presented results confirm the high performances reachable by InAlN-based technology with an output power density of 4.69 W/mm, a linear gain of 11.8 dB and a peak power-added efficiency of 48%. This is the first report of high performance InAlN/GaN HEMTs in mainland China.

A linearly graded-doping junction termination extension (LG-JTE) for 3.3-kV-class insulated gate bipolar transistors (IGBTs) was proposed and experimentally investigated. Unlike conventional multi-implantation utilizing more than one photolithography step, a single mask with injection window widths varied linearly away from the main junction to the edge was implemented in this proposed structure. Based on the simulation results, IGBTs with LG-JTE structures were successfully fabricated on the domestic process platform. The fabricated devices exhibited a 3.7 kV forward-blocking voltage, which is close to the theoretical value of an ideal parallel plane case. This is the first success in fabrication 3.3 kV-class IGBT in a domestic application.

A novel high-voltage device structure with a floating heavily doped N+ ring embedded in the substrate is reported, which is called FR LDMOS. When the N+ ring is introduced in the device substrate, the electric field peak of the main junction is reduced due to the transfer of the voltage from the main junction to the N+ ring junction, and the vertical breakdown characteristic is improved significantly. Based on the Poisson equation of cylindrical coordinates, a breakdown voltage model is developed. The numerical results indicate that the breakdown voltage of the proposed device is increased by 56% in comparison to conventional LDMOS.

A 4 mm gap semi-insulating (SI) GaAs photoconductive switch (PCSS) was triggered by a pulse laser with a wavelength of 1064 nm and a pulse energy of 0.5 mJ. In the experiment, when the bias field was 4 kV, the switch did not induce self-maintained discharge but worked in nonlinear (lock-on) mode. The phenomenon is analyzed as follows: an exciton effect contributes to photoconduction in the generation and dissociation of excitons. Collision ionization, avalanche multiplication and the exciton effect can supply carrier concentration and energy when an outside light source was removed. Under the combined influence of these factors, the SI-GaAs PCSS develops into self-maintained discharge rather than just in the light-controlled prebreakdown status. The characteristics of the filament affect the degree of damage to the switch.

Performance and reliability of a 2 transistor Si nanocrystal nonvolatile memory (NVM) are investigated. A good performance of the memory cell has been achieved, including a fast program/erase (P/E) speed under low voltages, an excellent data retention (maintaining for 10 years) and good endurance with a less threshold voltage shift of less than 10% after 104 P/E cycles. The data show that the device has strong potential for future embedded NVM applications.

In order to increase collection efficiency and eliminate image lag, multi n-type implants were introduced into the process of a pinned-photodiode. For the purpose of improving the collection efficiency, multi n-type implants with different implant energies were proposed, which expanded the vertical collection region. To reduce the image lag, a horizontal gradient doping concentration eliminating the potential barrier was also formed by multi n-type implants. The simulation result shows that the collection efficiency can be improved by about 10% in the long wavelength range and the density of the residual charge is reduced from 2.59 × 109 to 2.62 × 107 cm-3.

A dual-mode analog baseband with digital-assisted DC-offset calibration (DCOC) for WCDMA/GSM receiver is presented. A digital-assisted DCOC is proposed to solve the DC-offset problem by removing the DC-offset component only. This method has no bandwidth sacrifice. After calibration the measured output residual offset voltage is within 5 mV at most gain settings and the IIP2 is more than 60 dBm. The baseband is designed to be reconfigurable at bandwidths of 200 kHz and 2.1 MHz. Total baseband gain can be programmed from 6 to 54 dB. The chip is manufactured with 0.13 μm CMOS technology and consumes 10 mA from a 1.5 V supply in the GSM mode including an on-chip buffer while the core area occupies 1.2 mm2.

A 2.4 GHz radio frequency receiver front end with an on-chip transformer compliant with IEEE 802.11b/g standards is presented. Based on zero-IF receiver architecture, the front end comprises a variable gain common-source low noise amplifier with an on-chip transformer as its load and a high linear quadrature folded Gilbert mixer. As the load of the LNA, the on-chip transformer is optimized for lowest resistive loss and highest power gain. The whole front end draws 21 mA from 1.2 V supply, and the measured results show a double side band noise figure of 3.75 dB, -31 dBm IIP3 with 44 dB conversion gain at maximum gain setting. Implemented in 0.13 μ m CMOS technology, it occupies a 0.612 mm2 die size.

A new low-voltage and high-speed sense amplifier is presented, based on a very simple direct current-mode comparison. It adopts low-voltage reference current extraction and a dynamic output method to realize its performance indicators such as low voltage, low power and high precision. The proposed amplifier can sense a 0.5 μ A current gap and work with a lowest voltage of 1 V. In addition, the current power of a single amplifier is optimized by 15%.

A novel matching method between the power amplifier (PA) and antenna of an active or semi-active RFID tag is presented. A PCB dipole antenna is used as the resonance inductor of a differential power amplifier. The total PA chip area is reduced greatly to only 240 × 70 μm2 in a 0.18 μm CMOS process due to saving two on-chip integrated inductors. Operating in class AB with a 1.8 V supply voltage and 2.45 GHz input signal, the PA shows a measured output power of 8 dBm at the 1 dB compression point.

A fully balanced harmonic-suppressed quadrature-input frequency divider is proposed. The frequency divider improves the quadrature phase accuracy at the output by using both input I/Q signals. Compared with conventional dividers, the circuit achieves an output I/Q phase sequence that is independent of the input I/Q phase sequence. Moreover, the third harmonic is effectively suppressed by employing a double degeneration technique. The design is fabricated in TSMC 0.13-μ m CMOS and operated at 1.2 V. While locked at 8.5 GHz, the proposed divider measures a maximum third harmonic rejection of 45 dB and a phase noise of -124 dBc/Hz at a 10 MHz offset. The circuit achieves a locking range of 15% while consuming a total current of 4.5 mA.

A 5GHz low power direct conversion receiver radio frequency front-end with balun LNA is presented. A hybrid common gate and common source structure balun LNA is adopted, and the capacitive cross-coupling technique is used to reduce the noise contribution of the common source transistor. To obtain low 1/f noise and high linearity, a current mode passive mixer is preferred and realized. A current mode switching scheme can switch between high and low gain modes, and meanwhile it can not only perform good linearity but save power consumption at low gain mode. The front-end chip is manufactured on a 0.13-μm CMOS process and occupies an active chip area of 1.2 mm2. It achieves 35 dB conversion gain across 4.9-5.1 GHz, a noise figure of 7.2 dB and an IIP3 of -16.8 dBm, while consuming 28.4 mA from a 1.2 V power supply at high gain mode. Its conversion gain is 13 dB with an IIP3 of 5.2 dBm and consumes 21.5 mA at low gain mode.

A wide bandwidth continuous time sigma delta ADC is implemented in 130 nm CMOS. A detailed non-idealities analysis (excess loop delay, clock jitter, finite gain and GBW, comparator offset and DAC mismatch) is performed developed in Matlab/Simulink. This design is targeted for wide bandwidth applications such as video or wireless base-stations. A third-order continuous time sigma delta modulator comprises a third-order RC operational-amplifier-based loop filter and 3-bit internal quantizer operated at 512 MHz clock frequency. The sigma delta ADC achieves 60 dB SNR and 59.3 dB SNDR over a 16-MHz signal band at an OSR of 16. The power consumption of the CT sigma delta modulator is 22 mW from the 1.2-V supply.

A low power mixed signal DC offset calibration (DCOC) circuit for direct conversion receiver applications is designed. The proposed DCOC circuit features low power consumption, fast settling time and a small die area by avoiding the trade-off between loop response time and the high pass frequency of the DCOC servo loop in conventional analog DCOC systems. By applying the proposed DC offset correction circuitry, the output residue DC offset voltages are reduced to less than 38 mV and the DCOC loop settling time is less than 100 μs. The DCOC chip is fabricated in a standard 0.13-μm CMOS technology and drains only 196 μA from a 1.2-V power supply with its chip area of only 0.372 × 0.419 mm2.

A semi-digital clock and data recovery (CDR) is presented. In order to lower CDR trace jitter and decrease loop latency, an average-based phase detection algorithm is adopted and realized with a novel circuit. Implemented in a 0.13 μm standard 1P8M CMOS process, our CDR is integrated into a high speed serial and de-serial (SERDES) chip. Measurement results of the chip show that the CDR can trace the phase of the input data well and the RMS jitter of the recovery clock in the observation pin is 122 ps at 75 MHz clock frequency, while the bit error rate of the recovery data is less than 10 × 10-12.

A 12.5 Gbps 1:16 demultiplexer (DEMUX) integrated circuit is presented for multi-channel high-speed data transmission. A novel high-speed synchronizing technique is proposed and integrated in this DEMUX chip. Compared with conventional synchronizing techniques, the proposed method largely simplifies the system configuration. The experimental result demonstrates that the proposed circuit is effective in two-channel synchronization under a clock frequency of 12.5 GHz. The circuit is realized using 1 μ m GaAs heterojunction bipolar transistor technology with die area of 2.3 × 2.3 mm2.

A simple CNT/Fe3O4 composite electrophoretic deposition method to improve the field emission cathode properties of carbon nanotubes (CNTs) is proposed. It is found that CNT/Fe3O4 composite electrophoretic deposition leads to better field emission performance than that of single CNT electrophoretic deposition. The result is investigated using SEM, J-E and FE. After the process, the turn-on electric field decreases from 0.882 to 0.500 V/μm at an emission current density of 0.1 mA/cm2, and the latter increases from 0.003 to 1.137 mA/cm2 at an electric field of 0.64 V/μm. CNT/Fe3O4 composite electrophoretic deposition is an easy and effective cathode preparation for field emission display applications.

Chemical mechanical polishing (CMP) is the most effective wafer global planarization technology. The CMP polishing head is one of the most important components, and zone back pressure control technology is used to design a new generation of polishing head. The quality of polishing not only depends on slurry, but also depends on the precise control of polishing pressures. During the CMP polishing process, the set pressure of each chamber is usually not the same and the presence of a flexible elastic diaphragm causes coupling effects. Because of the coupling effects, the identification of multi-chambers and pressure controls becomes complicated. To solve the coupling problem, this paper presents a new method of multi-chamber decoupled control, and then system identification and control parameter tuning are carried out based on the method. Finally, experiments of multi-chambers inflated at the same time are performed. The experimental results show that the presented decoupling control method is feasible and correct.