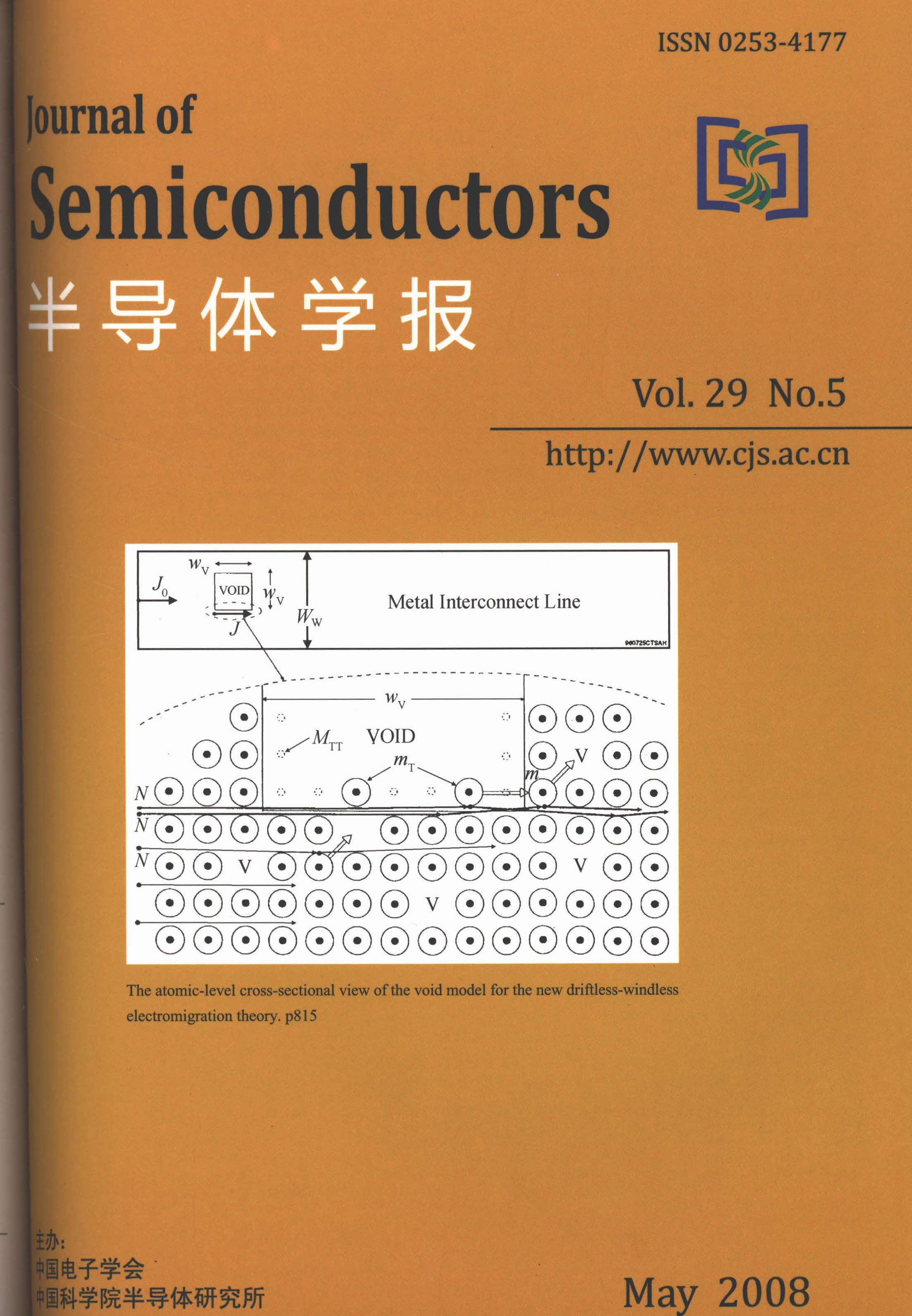

Electromigration is the transport of atoms in metal conductors at high electronic current-densities which creates voids in the conductors and increases the conductors’ electrical resistance.It was delineated in 1961 by Huntington;then modeled by the empirical electrical resistance formula derived by Black in 1969 to fit the dependences of the experimental electrical resistance and failure data on the electrical current density and temperature.Tan in 2007 reviewed 40-years’ applications of the empirical Black formula to conductor lines interconnecting transistors and other devices in silicon integrated circuits.Since the first Landauer theory in 1957,theorists have attempted for 50 years to justify the drift force or electron momentum transfer assumed by Black as some electron-wind force to impart on the metal atoms and ions to move them.Landauer concluded in 1989 that the electron wind force is untenable even considering the most fundamental and complete many-body quantum transport theory.A driftless or electron-windless atomic void model for metal conductor lines is reviewed in this article.It was developed in the mid-1980 and described in 1996 by Sah in a homework solution.This model accounts for all the current and temperature dependences of experimental resistance data fitted to the empirical Black formula.Exact analytical solutions were obtained for the metal conductor line resistance or current,R(t)/R(0)=J(t)/J(0)=[1-2(t/τα)1/α]-1/2, in the bond-breaking limit with α=1 to 2 and diffusion limit with α=2 to 4,from low to high current densities, where τα is the characteristic time constant of the mechanism, containing bond breaking and diffusion rates and activation energies of the metal.

The effect of rapid thermal annealing (RTA) ambient on denuded zone and oxygen precipitates in Czochralski (CZ) silicon wafers is studied in this paper.N2 and a N2/NH3 mixture are used as RTA ambient.It is demonstrated that a high density of oxygen precipitates and thin denuded zone are obtained in N2/NH3 ambient,while a relatively lower density of oxygen precipitates and thicker denuded zone are observed in N2 ambient.As the RTA duration times increased,the oxygen precipitate density increased and the denuded zone depth decreased.X-ray photoelectron spectroscopy (XPS) data and atomic force microscope (AFM) results show that there was a surface nitriding reaction during the N2/NH3 ambient RTA process,which can explain the different effect of RTA ambient.

This paper introduces a 2.5GHz low phase-noise cross-coupled LC-VCO realized in 0.35μm SiGe BiCMOS technology.The conventional definition of a VCO operating regime is revised from a new perspective.Analysis shows the importance of inductance and bias current selection for oscillator phase noise optimization.Differences between CMOS and BJT VCO design strategy are then analyzed and the conclusions are summarized.In this implementation,bonding wires form the resonator to improve the phase noise performance.The VCO is then integrated with other components to form a PLL frequency synthesizer with a loop bandwidth of 30kHz.Measurement shows a phase noise of -95dBc/Hz at 100kHz offset and -116dBc/Hz at 1MHz offset from a 2.5GHz carrier.At a supply voltage of 3V,the VCO core consumes 8mA.To our knowledge,this is the first differential cross-coupled VCO in SiGe BiCMOS technology in China.

GaAs PIN diodes optimized for X-band low loss and high isolation switch application are presented.The impact of diode physical characteristics and electrical parameters on switch performance is discussed.A new structure for GaAs PIN diodes is proposed and the fabrication process is described.GaAs PIN diodes with an on-state resistance of <2.2Ω and off-state capacitance <20fF in the range of 100MHz to 12.1GHz are obtained.

This paper describes the design of a low voltage differential signal (LVDS) transmitter and receiver with high speed and low power for CPU,LCD,FPGA,and other fast links.In the proposed transmitter,a stable reference and a common mode feedback circuit are integrated into the LVDS drivers,which enable the transmitter to tolerate variations of process,temperature,and supply voltage.The proposed receiver implements a rail-to-rail amplifier architecture that allows a 1.6Gb/s transmission.The transmitter and receiver are implemented in HJ TC 3.3V,0.18μm CMOS technology.The experimental results demonstrate that the transmitter and receiver reach 1.6Gb/s.The transmitter and receiver pad cells exhibit a power consumption of 35 and 6mW,respectively.

The binding energy of a bound polaron in a finite parabolic quantum well is studied theoretically by a fractional-dimensional variational method.The numerical results for the binding energies of the bound polaron and longitudinal-optical phonon contributions in GaAs/Al0.3Ga0.7As parabolic quantum well structures are obtained as functions of the well width.It is shown that the binding energies of the bound polaron are obviously reduced by the electron-phonon interaction and the phonon contribution is observable and cannot be neglected.

We study the influences of the temperature on the energy-band structure for the Holstein molecular-crystal model.We show that the energy-band width and the energy-gap width of a solid are relevant to both the interaction between an electron and thermal phonons and to thermal expansion.For a one-dimensional Li atom lattice chain,under the chosen parameters,the width of the 1s and 2s energy bands narrows as the temperature increases and the energy-gap width between the two bands widens.These results agree qualitatively with those observed experimentally.Studying temperature dependence of the energy-band structure is of great importance for understanding optical and transporting characteristics of a solid.

A method for estimating the defects density in SiC bulk crystals by defect-selective etching in molten KOH has already been successfully demonstrated.In this paper,the results of applying this technique to bulk SiC crystals are reported.Etching produced hexagonal pits on the Si-polar (0001) plane,while round pits formed on the C face.The etching rate and the nature of etch pits for SiC depends on the growth process.For SiC crystals grown by the PVT process with high growth gas flow rate,the edge and screw dislocation density and the MP density are about 2.82E5,94,and 38cm-2,respectively.For SiC crystals grown by the PVT process with low growth gas flow rate,those defects densities are about 9.34E5,2, and 29cm-2,respectively.The results indicate that as the growth gas flow rate increases,the edge dislocation density decreases to avoid N2 impurity.

A series of microcrystalline silicon thin films were fabricated by very high frequency plasma enhanced chemical vapor deposition (VHF-PECVD) at different silane concentrations in a P chamber.Through analysis of the structural and electrical properties of these materials,we conclude that the photosensitivity slightly decreased then increased as the silane concentration increased,while the crystalline volume fraction indicates the opposite change.Results of XRD indicate that thin films have a (220) preferable orientation under certain conditions.Microcrystalline silicon solar cells with conversion efficiency 4.7% and micromorph tandem solar cells 8.5% were fabricated by VHF-PECVD (p layer and i layer of microcrystalline silicon solar cells were deposited in P chamber),respectively.

Transparent zinc oxide thin film transistors (ZnO-TFTs) with bottom-gate and top-gate structures were constructed on 50mm silica glass substrates.The ZnO films were deposited by RF magnetron sputtering and SiO2 films served as the gate insulator layer.We found that the ZnO-TFTs with bottom-gate structure have better electrical performance than those with top-gate structure.The bottom-gate ZnO-TFTs operate as an n-channel enhancement mode,which have clear pinch off and saturation characteristics.The field effect mobility,threshold voltage,and the current on/off ratio were determined to be 18.4cm2 /(V·s),-0.5V and 1E4,respectively.Meanwhile,the top-gate ZnO-TFTs exhibit n-channel depletion mode operation and no saturation characteristics were detected.The electrical difference of the devices may be due to the different character of the interface between the channel and insulator layers.The two transistors types have high transparency in the visible light region.

An analytical model of electron mobility for strained-silicon channel nMOSFETs is proposed in this paper.The model deals directly with the strain tensor,and thus is independent of the manufacturing process.It is suitable for 〈100〉/〈110〉 channel nMOSFETs under biaxial or 〈100〉/〈110〉 uniaxial stress and can be implemented in conventional device simulation tools.

A compact drain current including the variation of barrier heights and carrier quantization in ultrathin-body and double-gate Schottky barrier MOSFETs (UTBDG SBFETs) is developed.In this model,Schrodinger's equation is solved using the triangular potential well approximation.The carrier density thus obtained is included in the space charge density to obtain quantum carrier confinement effects in the modeling of thin-body devices.Due to the quantum effects,the first subband is higher than the conduction band edge,which is equivalent to the band gap widening.Thus,the barrier heights at the source and drain increase and the carrier concentration decreases as the drain current decreases.The drawback of the existing models,which cannot present an accurate prediction of the drain current because they mainly consider the effects of Schottky barrier lowering (SBL) due to image forces,is eliminated.Our research results suggest that for small nonnegative Schottky barrier (SB) heights,even for zero barrier height,the tunneling current also plays a role in the total on-state currents.Verification of the present model was carried out by the device numerical simulator-Silvaco and showed good agreement.

The reverse generation current under high-gate-voltage stress condition in LDD nMOSFET's is studied.We find that the generation current peak decreases as the stress time increases.We ascribe this finding to the dominating oxide trapped electrons that reduce the effective drain bias,lowering the maximal generation rate.The density of the effective trapped electrons affecting the effective drain bias is calculated with our model.

A monolithic single pole single throw (SPST) switch is developed with GaAs PIN diode technology from IMECAS.A novel small signal model of a GaAs PIN diode is developed for circuit simulation.The switch features an on-state insertion loss of less than 1.6dB and a return loss of greater than 10dB while maintaining an off-state isolation of greater than 23dB from 5.5 to 7.5GHz.The measured 1dB power gain compression point is about 20dBm.

This paper presents an optimized SRAM that is repairable and dissipates less power.To improve the yield of SRAMs per wafer,redundancy logic and an E-FUSE box are added to the SRAM and an SR SRAM is set up.In order to reduce power dissipation,power on/off states and isolation logic are introduced into the SR SRAM and an LPSR SRAM is constructed.The optimized LPSR SRAM64K×32 is used in SoC and the testing method of the LPSR SRAM64K×32 is also discussed.The SoC design is successfully implemented in the Chartered 90nm CMOS process.The SoC chip occupies 56mm×56mm of die area and the power dissipation is 1997mW.The test results indicate that LPSR SRAM64K×32 obtains 17301% power savings and the yield of the LPSR SRAM64K×32s per wafer is improved by 13255%.

The forbidden pitch "dip" in the critical dimension (CD) through the pitch curve is a well-known optical proximity effect.The CD and CD process window near the "dip" ,usually found near a pitch range of 1.1 to 1.4 wavelength/NA (numerical aperture),is smaller when compared with other pitches.This is caused by inadequate imaging contrast for an unequal line and space grating.Although this effect is relatively well-known,its relationship with typical process condition parameters,such as the effective image blur caused by the photo-acid diffusion during the post exposure bake or the aberration in the imaging lens,has not been systematically studied.In this paper,we will examine the correlation between the image blur and the effect on the CD,including the decrease in the CD value (the depth of the "dip" ) and the CD process window.We find that both the decrease in the CD value and the focus latitude near the forbidden pitch correlate very well with the effective Gaussian image blur.Longer effective diffusion length correlates well with a smaller process window and a deeper CD "dip" .We conclude that the dip depth is very sensitive to the change in image contrast.

The waveguide design is one of the most important parts in a terahertz quantum cascade laser(QCL).Si/SiGe QCL waveguides,based on the Drude model and finite-difference time-domain (FDTD) method,are designed by the traditional refractive index waveguide structure,the single-sided metal structure,the double-metal clad structure,and a novel metal/metal silicide structure.The metal/metal silicide structure,showing high modal confinement,is convenient in process engineering and is expected to be a viable waveguide solution for Si/SiGe QCLs in the THz range.

A compact and stable three-port optical gate has been successfully fabricated by monolithically integrating a simple photodiode and an electroabsorption modulator.The gate shows an excellent DC logic "and" function with different load resistors.Its dynamical characteristics without packaging have also been measured.We observed a dynamic extinction ratio of over 7dB with a 950Ω load resistor and a 7mW control light power at 622Mbit/s.

A novel high-bandwidth,high-sensitivity differential optical receiver without any additional cost compared to general optical receivers,is proposed for high-speed optical communications and interconnections.High bandwidth and high sensitivity are achieved through a fully differential transimpedance amplifier with balanced input loads and two photodetectors to convert the incident light into a pair of differential photogenerated currents,respectively.In addition,a corresponding 0.35μm standard CMOS optoelectronic integrated receiver with two 60μm× 30μm,1.483pF fingered p+/n-well/p-substrate photodiodes is also presented.The simulation results demonstrate that it achieves a 1.37GHz bandwidth and a 819dBΩ transimpedance gain,supporting data rates up to at least 2Gbit/s.The device consumes a core area of 0.198mm2 and the optical sensitivity is at least -13dBm for a 1E-12 bit error rate under a 2E15-1 PRBS input signal.

This paper presents a novel adaptive-bandwidth charge pump PLL with low jitter and a wide tuning range.With an adaptive bandwidth,the proposed PLL can scale its loop dynamics proportional to the output frequency and maintain optimal performance over its entire output range.In order to improve the jitter performance of the PLL,a matching technique is employed in the charge pump,and a voltage-to-voltage converter is used to achieve a low gain VCO.The experimental chip was fabricated in a 0.35μm CMOS process.The measured results show that the PLL has perfect jitter performance within its operating range from 200MHz to 1.1GHz.

An improved charge-averaging charge pump and the corresponding circuit implementation are presented.The charge-averaging charge pump proposed by Koo is analyzed and a new scheme is proposed.This new scheme decreases power by 1/3 and eliminates the practical defects in the original.Spectre Verilog behavioral simulation results show that the proposed scheme can strongly reduce the energy of spurs.Circuit implementation of this new charge pump for a frequency synthesizer with a fractional division ratio of 1/3 is then presented and multi-level simulation is performed to validate its feasibility at the circuit level.The simulation results show this new scheme outputs a flat voltage curve in a locked state and can thus effectively suppress fraction spurs.

This paper presents two approaches for system-level simulation of force-balance accelerometers.The derivation of the system-level model is elaborated and simulation results are obtained from the implementation of those strategies on the fabricated silicon force-balance MEMS accelerometer.The mathematical model presented is implemented in VHDL-AMS and SIMULINK TM,respectively.The simulation results from the two approaches are compared and show a slight difference.Using VHDL-AMS is flexible,reusable,and more accurate.But there is not a mature solver developed for the language and this approach takes more time,while the simulation model can be easily built and quickly evaluated using SIMULINK.

A novel low-voltage,low constant-impedance switch is proposed,which not only eliminates the parasitic capacitor but also reduces the variation of switch "on" resistance.With the gain-boost technology,the operational transconductance amplifier used in this analog-to-digital converter (ADC) achieves enough DC gain and unity-gain frequency under the low voltage supply and to guarantee the performance of the sample and hold circuit (S/H) and the sub-stages.Based on these methods,a 10bit 100Msps pipelined ADC is fabricated in a 0.18μm CMOS process and operates under a 1.8V voltage supply.The ADC achieves an SNR of 54.2dB (input frequency of 6.26MHz) and an SNR of 49.8dB (input frequency of 48.96MHz) when the sampling frequency is 100MHz.

In this paper,a detailed analysis of a phase interpolator for clock recovery is presented.A mathematical model is setup for the phase interpolator and we perform a precise analysis using this model.The result shows that the output amplitude and linearity of phase interpolator is primarily related to the difference between the two input phases.A new encoding pattern is given to solve this problem.Analysis in the circuit domain was also undertaken.The simulation results show that the relation between RC time-constant and time difference of input clocks affects the linearity of the phase interpolator.To alleviate this undesired effect,two adjustable-RC buffers are added at the input of the PI.Finally,a 90nm CMOS phase interpolator,which can work in the frequency from 1GHz to 5GHz,is proposed.The power dissipation of the phase interpolator is 1mW with a 1.2V power supply.Experiment results show that the phase interpolator has a monotone output phase and good linearity.

3C-SiC film was hetero-epitaxial grown on 6H-SiC substrate by the low temperature hot wall chemical vapor deposition method at 1250℃,using SiH4 and C3H8 as gas sources.Results of scanning electron microscopy and atomic force microscopy show that the sample's surface is smooth without a visible island structure.The image of the cross-section transmission electron microscopy shows that the compact and uniform SiC epi-layer has a flat interface,and its thickness is about 50nm.High-resolution transmission electron microscopy shows that the substrate and epi-layer are well-arranged 6H-SiC and 3C-SiC structures,respectively,with a smooth transition and no polytype in the junction.The selected area electron diffraction pattern also shows that the epi-layer is 3C-SiC film with a zinc blende structure,and the calculated lattice constant is 0.4362nm.

ZnTe single crystals were grown perfectly by employing the Te-solution method.X-ray diffraction was introduced to investigate the crystals,and 〈110〉 oriented crystals of 10mm×10mm size were obtained.The transmittance is about 61% in range of 2.5 ~20mm,as measured with a Fourier Transform Infrared spectrometer.The visible and near-infrared spectrum show that the ZnTe band-gap is about 2.24eV.Moreover,a THz pulse was emitted and detected on a ZnTe single crystal by means of a femto-second Ti:sapphire amplifier system.The THz radiation signal has a pulse width of about 0.18ps and frequency bandwidth of 5THz.

This article reports on the study of the transition region of a SiO2/4H-SiC interface prepared by dry oxidation using ADXPS.The study contains interface composition,component distribution and so on.We prepared the samples with oxidation thicknesses between 1nm and 1.5nm based on controlling the speed that the dilute HF acid etches SiO2 grown on SiC.The standard samples were adopted to assist in analysis.The results indicate that the SiO2/4H-SiC interface simultaneously contains Si1+,Si2+,and Si3+.The ADXPS results suggest a layered model is suitable for describing the component distribution.An atom-level model of the transition region was established and the thickness of oxidation was calculated.The change of the transition components quantum and C-Vcurve indicate that the transition components directly affect the density interface trap.

According to the relation among peak voltage Vp,series resistance RS,and external resistance Rex,a novel method for measuring the series resistance RS of RTDs is proposed.The experimental result demonstrates that this method is accurate,simple,convenient,and quick.The derivation of the relation among Vp,RS,and Rex,the principle of RS measurement,the measured result of RS,and a comparison between this method and other measurement methods are illustrated in detail.

The temperature distribution of typical-sized n-type polycrystalline silicon thin film transistors under self-heating (SH) stress is studied by finite element analysis. From both steady-state and transient thermal simulation, the influence of device power density,substrate material,and channel width on temperature distribution is analyzed.This study is useful for understanding the mechanism of self-heating degradation,and to find approaches to effectively alleviate the SH effect in device operation.

In this work,our modeling research focuses on two-step Ge profile base SiGe heterojunction bipolar transistors (HBTs) manufactured by IMEC advanced 0.13μm quasi-self-aligned SiGe BiCMOS process technology.From 25℃ to 125℃,measurements including Early voltage plots and Gummel plots of the SiGe HBT are taken and all parameters of the temperature scalable Mextram 504 model are extracted.Based on this,a complete solution of the temperature scalable modeling work is explored.The extracting method of the temperature scalable Mextram 504 model is improved and an optimized flow of model extraction for a 0.13μm two-step Ge profile base SiGe HBT is suggested.The temperature impacted characteristics of the avalanche current are discussed and new temperature scaling parameters of the avalanche current are presented.Simulation of the Mextram model for SiGe HBTs at different temperatures becomes more accurate.

Using novel technologies such as the mesa junction termination structure with one guard ring and a nonlinear blasting resistor of microwave power transistors,a high L-band medium silicon pulse power transistor has been developed.Under 40V supply voltage,internally matched devices cover the frequency for high L-band radar applications from 1.46~1.66GHz with a pulsed output power of 250W and 45% collector efficiency.The gain is more than 7.0dB.

Based on the 6×6 Luttinger-Kohn Hamiltonian,including strain,and taking into account of the quantum-size effect and spin-orbit coupling,a band structure model for p-type silicon nanoplate piezoresistors is established using the finite difference method.The effect of thickness,impurity concentration,and temperature on the piezoresistive coefficient of the silicon nanoplate was quantitatively investigated based on its dependence on the band structure.The results indicate that the effect of the quantum confinement of holes,which dramatically alters the band structure,enhances the piezoresistive coefficient of the p-type silicon nanoplate piezoresistors.The spin-orbit coupling,which changes the band-edge energies,plays a significant role in the high strained silicon nanoplates.The size-dependent piezoresistive coefficient of the p-type silicon nanoplate piezoresistors increases as the thickness decreases.The piezoresistive coefficient was also observed to decrease with increased impurity concentration and temperature.In the extreme degenerate range,the piezoresistive coefficient is controlled only by the impurity concentration and becomes temperature-independent.In the non-degenerate range,the opposite phenomenon occurs.Furthermore,according to the form change of constant energy surfaces for heavy and light holes in the presence of stress,we qualitatively analyze the origin of the longitudinal piezoresistive effect in the silicon nanoplate.

Based on the fabrication process of a microchannel,a method to measure the flow characteristics of fluids in a microchannel driven by hydrostatic pressure is proposed.This method easily stabilizes the pressure.The effects of different factors such as pressure,type of working fluid,and temperature on the flow characteristics are analyzed.The results show that some flow characteristics of the microfluid are the same as the micro fluid,but some other flow characteristics are different from the micro fluid.These results provide not only new evidence to understand the flow characteristics of microfluid,but also new references to design devices using flow characteristics of microfluid.

In order to understand the relationship between RF bias voltage on bottom electrode and other process parameters,we designed an experiment.The results indicated that the relationship varies depending on the other parameters' variation.The upper electrode RF power,the bottom electrode RF power,and gas pressure all distinctly affect this relationship.

The slurry method based on water soluble PVA is discussed.A controlled phosphor layer is obtained by the slurry method on the surface of blue LED chips.Due to the absorption of Cr3+,the luminous intensity of white LEDs can be improved by decreasing the concentration of ADC or increasing the concentration of phosphor in the slurry.The stand-time of slurry for 3~5h was optimized in a darkroom.The hue of output light moved to the blue-light zone and the luminous flux increased from 44.8~59 lm to 79.4~84.9 lm after the silica gel was coated on the LED coated phosphor particles.

This paper presents a 20W×2 class-D audio power amplifier with high efficiency in a 0.8μm BCDMOS process.The amplifier is capable of driving 2×8Ω loads from a 18V power supply at more than 85% power efficiency,and its maximum output power is more than 20W×2.The circuit detail of the output stage,over-current protection,and rail-to-rail comparator are also presented.Through analysis of the LDMOSFET cross section,the impact of the parasitical effect on the distortion of the output is discussed.Finally,the experimental results of this work are presented.

Calibration is a crucial technique for the implementation of high-speed and high resolution analog-to-digital converters.This paper describes the structure of a pipelined ADC,analyzes the sources of errors in the pipelined ADC,focuses on a calibration algorithm that gains the weights by calculating the height of the jumping point of the transition function,presents its implementation scheme,and gives the implementation results and layout of the calibration system.Implementation the calibration system is simple and requires only pure digital circuits.Meanwhile,the simulation of this algorithm shows that it meets the requirements of high-resolution ADCs,and,with respect to availability and reliability,it is a well implemented scheme.

Aimed at the problem of quickly detecting phosphorus-containing toxic gas,we used home-made hybrid PdPc-PANI as the material for sensitive film and designed a binary channel SAW sensor.We expound the basic principle of the sensor and deduce that when using organic film as the intermediate medium of channel,different frequency output Δf was superimposed by a mathematical model using the two mechanisms of physical chemistry adsorption.According to the conditions of sound wave oscillation,we designed a signal gathering circuit whose oscillation frequency is 146±5MHz.Using lithium tantalate as piezoelectric substrate,through MEMS micro-fabrication we made finger-cross electrodes couple and hot film.We adopted vacuum deposition technology to make material of sensitive film into film,which modified the center of the SAW channel to compose the SAW sensor.The testing result indicates that when material has the best sensitivity,the mixture ratio is PdPc0.35PANIO.65.When the chip is heated to 60~80℃,it can increase the performance,the responsive time is less than or equal to 30s;The gas concentration of output and testing is consistent with that in the mathematic model,and is the N-style linear relation of linear change rate -110kHz (mg/m3).The SAW sensor counteracts the interference of gasoline oil and carbon dioxide and so on;Through the checking of stability for 80 days,Δf is less than or equal to ±0.1kHz,which meets the requirement for practical use.

This paper presents a fully integrated wideband LC voltage-controlled oscillator (VCO) with small tuning gain fluctuation.This VCO is designed for a dual-conversion low-IF architecture (DLIF) DTV tuner.A switched varactor array is proposed to suppress tuning gain fluctuation for the performance of the phase locked loop (PLL).The whole VCO was implemented in a 0.18μm CMOS process.The measured results show -126dBc/Hz phase noise at 1MHz offset frequency.The measured tuning range is 860MHz (53.8%) from 1.17 to 2.03GHz with the tuning gain from 69 to 93MHz/V.Power consumption is about 9mW with a 1.5V supply voltage.

A conversion-precision and sampling-rate programmable pipeline analog-to-digital converter (ADC),without adjusting the bias current of operational amplifiers,is presented in this paper.This ADC achieves a conversion-precision of 8 to 11bits and a sampling-rate from 400k to 40MSa/s.To increase the power-on speed and reduce the power consumption,a novel pre-charged switched operational amplifier is proposed.The power can be significantly reduced by adopting an improved current modulated power scaling (CMPS) technique,the proposed switched operational amplifier,a SHA-less technique,and a dynamic comparator.The ADC is designed in a 1.8V 1P6M 0.18μm CMOS process.Simulation results indicate that the ADC exhibits a spurious free dynamic range (SFDR) of 81dB and a signal-to-noise and distortion ratio (SNDR) of 67dB.Programmed at 11bits and 40MSa/s,the ADC consumes 29mW when a 19.02MHz sine signal is fed-in.

This paper presents a method for reusing the results of standard-cell-based OPCs.For this purpose,a reduced standard cell library composed of an inverter and MUX2 is constructed to realize the core logic of a traditional standard cell library.This library is manufacturing-friendly,and the reuse of its OPC results can improve the efficiency of chip manufacturing greatly and highly reduce the need for large storage.The electrical simulation results of the library also show that its increase in area,delay,and power is minor compared with traditional standard cell libraries.